Page 36 - Chip Scale Review_January-February_2024-digital

P. 36

information provided by the 3D-IC automatic place-and-route electronic To h e l p d e s i g n e r s m a k e t h i s

system-level netlist. design automation (EDA) tools), which transition, we developed an automated

Another challenge when verifying means that the interposer connectivity approach—using Siemens’s Xpedition

the connectivity of a multi-substrate is usually captured in a Verilog netlist Su b s t r a t e I n t eg r a t o r (x S I ) — i n

3D-IC design is the project version- format. As far as the designer can tell, which the desig ner can compare

based connectivity exceptions, i.e., this is the best system-level golden their traditional flow netlist (SPICE,

the need for creating shorts/opens connectivity reference that he or she can Verilog, or CSV) versus the system-

while physically implementing the generate using the traditional IC flows. level assembly netlist generated from

substrates. Designers need to treat Now, however, when graduating to xSI (CSV). This automated netlist-

these opens/shorts as “expected” errors 3D-IC system-level design tools and versus-netlist comparison is done

and differentiate them from the “real” approaches, how will designers know using Calibre tools accessed through

and “undesirable” errors. they built the connectivity correctly? an add-on feature integrated with xSI.

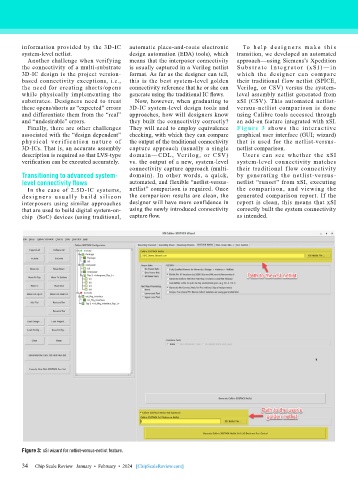

Finally, there are other challenges They will need to employ equivalence F i g u re 3 shows t he i nt e r a c t ive

associated with the “design dependent” checking, with which they can compare graphical user interface (GUI; wizard)

phy sic a l ve r i f ic a t io n n a t u r e of the output of the traditional connectivity that is used for the netlist-versus-

3D-ICs. That is, an accurate assembly capture approach (usually a single netlist comparison.

description is required so that LVS-type domain— CDL, Verilog, or CSV) Users can see whether the xSI

verification can be executed accurately. vs. the output of a new, system-level system-level connectivity matches

connectivity capture approach (multi- their traditional f low connectivity

Transitioning to advanced system- domain). In other words, a quick, by generating the netlist-versus-

level connectivity flows automated, and flexible “netlist-versus- netlist “runset” from xSI, executing

In the case of 2.5D-IC systems, netlist” comparison is required. Once the comparison, and viewing the

d e sig n e r s u s u a l ly bu i ld si l ic o n the comparison results are clean, the generated comparison report. If the

interposers using similar approaches designer will have more confidence in report is clean, this means that xSI

that are used to build digital system-on- using the newly introduced connectivity correctly built the system connectivity

chip (SoC) devices (using traditional, capture flow. as intended.

Figure 3: xSI wizard for netlist-versus-netlist feature.

34 Chip Scale Review January • February • 2024 [ChipScaleReview.com]

34