Page 42 - Chip Scale Review_May June_2021-digital

P. 42

A new RDL-first FOWLP for low-density applications

By Isamu Nishimura, Mamoru Yamagami, Hiroshi Oji, Taro Hayashi [ROHM Co., Ltd.]

A s Mo or e’s L aw dev ic e W h ile FOW LP a nd FOPLP a re performance. In addition, we have

scali ng approaches it s

applications, we are targeting low-

s m a l l er, t h i n n er a n d e n a b li n g

limits, a variety of “More attracting attention for high-density added value by creating products

than Moore” breakthrough technologies density applications, which have a modularization. Businesses in the

are attracting attention [1]. For example, relatively small number of pins and field of low-density applications,

fan-out packages such as fan-out wafer- a small package size. We provide however, also require technology

level package (FOWLP) and fan-out FOWLP technology, called RISPAC, that meets low-cost requirements.

panel-level package (FOPLP) have been for low-density applications using Therefore, our FOWLP production

proposed by various companies, and the mass production capabilities of line has selected the redistribution

materials and equipment to support large-scale integration (LSI). This layer (RDL)-first (or RDL-1st) process

them have been developed [2,3]. These capability effectively combines front- that utilizes legacy 8-inch wafer LSI

fan-out packages are normally designed end wafer technology and back-end manufacturing based on its lower

for the high-density application field, package assembly technology. costs (equipment, substrate, etc.). The

which enables high functionality for By using our FOWLP technology, RDL-1st FOWLP has a cost advantage

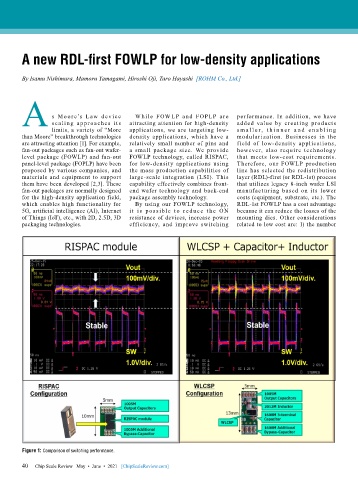

5G, artificial intelligence (AI), Internet it i s p o s sible t o r e d uc e t he ON because it can reduce the losses of the

of Things (IoT), etc., with 2D, 2.5D, 3D resistance of devices, increase power mounting dies. Other considerations

packaging technologies. efficiency, and improve switching related to low cost are: 1) the number

Figure 1: Comparison of switching performance.

40 Chip Scale Review May • June • 2021 [ChipScaleReview.com]

40