Page 44 - Chip Scale Review_May June_2021-digital

P. 44

formation. We have confirmed in our A new concept in FOWLP equipment that was indispensable

own studies that stable open and short technology for FOWLP production was installed

yields can be achieved with a 90µm We developed RISPAC to increase in the clean room for use in mass

terminal pitch device. This silicon the added value of our products. production. Our FOWLP technology

body type RDL-1st FOWLP has two O u r FOW LP manufact u r i ng li ne targets the low-density application

options: one for a single device, w a s l a u n c h e d b y u t i l i z i n g L SI field, which has a relatively small

and the other for a dual device in equipment—such legacy equipment number of pins and a small package

which dies are stacked. Both options can be satisfactorily used in FOWLP size. As previously noted, we have two

achieved the required performance manufacturing, contributing to the types of FOWLP: resin body type, and

and reliability in our evaluations. reduction of the early investment in silicon body type.

the line. In addition, a subset of the By using RISPAC technology, our

customers’ device requirements have

been fulfilled. It is possible to reduce

Laser Assisted Bonding the ON resistance of devices, increase

p owe r e f f i c i e n c y, a n d i m p r ove

switching performance (Figure 1).

T he example i ncludes switchi ng

performance improvement in resin-

body type products. We confirmed that

the switching noise can be reduced to

1/10 in the voltage regulator module

with a driver and MOSFET (DrMOS).

On the other hand, our silicon body

type FOWLP also complies with a

variety of customers’ requests and

captures their demands. The silicon

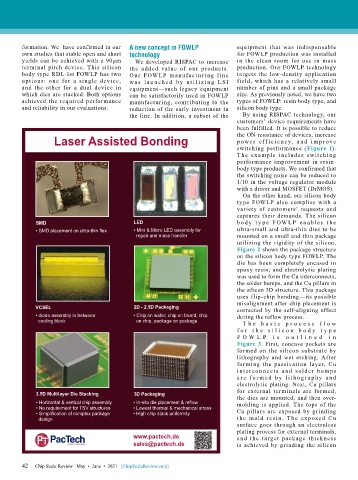

SMD LED b o d y t y p e F OW L P e n a b l e s t h e

• SMD placement on ultra-thin flex • Mini & Micro LED assembly for ultra-small and ultra-thin dies to be

repair and mass transfer mounted on a small and thin package

utilizing the rigidity of the silicon.

Figure 2 shows the package structure

on the silicon body type FOWLP. The

die has been completely encased in

epoxy resin; and electrolytic plating

was used to form the Cu interconnects,

the solder bumps, and the Cu pillars in

the silicon 3D structure. This package

uses flip-chip bonding—its possible

misalignment after chip placement is

VCSEL 2D - 2.5D Packaging corrected by the self-aligning effect

• diode assembly in between • Chip on wafer, chip on board, chip during the reflow process.

cooling block on chip, package on package T h e b a s i c p r o c e s s f l o w

f o r t h e s i l i c o n b o d y t y p e

F O W L P i s ou t l i n e d i n

Figure 3. First, concave pockets are

formed on the silicon substrate by

lithography and wet etching. After

forming the passivation layer, Cu

i ntercon nect s a nd solder bu mps

a r e fo r m e d b y l it hog r a p hy a n d

electrolytic plating. Next, Cu pillars

for external terminals are formed,

3.5D Multilayer Die Stacking 3D Packaging the dies are mounted, and then over-

• Horizontal & vertical chip assembly • In-situ die placement & reflow molding is applied. The tops of the

• No requirement for TSV structures • Lowest thermal & mechanical stress

• Simplification of complex package • High chip stack uniformity Cu pillars are exposed by grinding

design the mold resi n. T he exposed Cu

surface goes through an electroless

plating process for external terminals,

www.pactech.de and the target package thick ness

sales@pactech.de is achieved by grinding the silicon

42

42 Chip Scale Review May • June • 2021 [ChipScaleReview.com]