Page 45 - ChipScale_May-June_2020-digital

P. 45

Scaling CMOS beyond FinFETs: from nanosheets and

forksheets to CFETs

By Julien Ryckaert [imec]

Get ready! New transistor architectures below 3nm will impact interconnect structures in a chip’s BEOL. CSR asked imec for input.

T h e F i n F E T t r a n s i s t o r for enhanced performance and reduced technology node can be used to perform

architecture is the workhorse

FinFET allowed an increased fin height

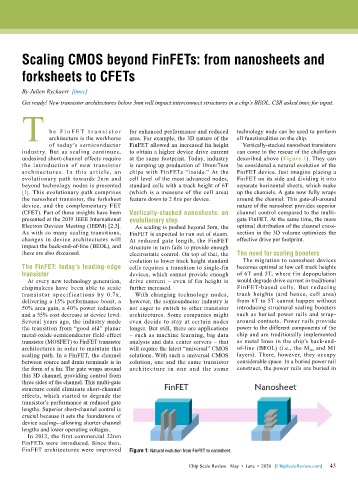

Vertically-stacked nanosheet transistors

of today’s semiconductor area. For example, the 3D nature of the all functionalities on the chip.

industry. But as scaling continues, to obtain a higher device drive current can come to the rescue of the challenges

undesired short-channel effects require at the same footprint. Today, industry described above (Figure 1). They can

the introduction of new transistor is ramping up production of 10nm/7nm be considered a natural evolution of the

architect u res. In this ar ticle, an chips with FinFETs “inside.” At the FinFET device. Just imagine placing a

evolutionary path towards 2nm and cell level of the most advanced nodes, FinFET on its side and dividing it into

beyond technology nodes is presented standard cells with a track height of 6T separate horizontal sheets, which make

[1]. This evolutionary path comprises (which is a measure of the cell area) up the channels. A gate now fully wraps

the nanosheet transistor, the forksheet feature down to 2 fins per device. around the channel. This gate-all-around

device, and the complementary FET nature of the nanosheet provides superior

(CFET). Part of these insights have been Vertically-stacked nanosheets: an channel control compared to the multi-

presented at the 2019 IEEE International evolutionary step gate FinFET. At the same time, the more

Electron Devices Meeting (IEDM) [2,3]. As scaling is pushed beyond 5nm, the optimal distribution of the channel cross-

As with so many scaling transitions, FinFET is expected to run out of steam. section in the 3D volume optimizes the

changes in device architectures will At reduced gate length, the FinFET effective drive per footprint.

impact the back-end-of-line (BEOL), and structure in turn fails to provide enough

these are also discussed. electrostatic control. On top of that, the The need for scaling boosters

evolution to lower track height standard The migration to nanosheet devices

The FinFET: today’s leading-edge cells requires a transition to single-fin becomes optimal at low cell track heights

transistor devices, which cannot provide enough of 6T and 5T, where fin depopulation

At every new technology generation, drive current – even if fin height is would degrade drive current in traditional

chipmakers have been able to scale further increased. FinFET-based cells. But reducing

transistor specif ications by 0.7x, With changing technology nodes, track heights (and hence, cell area)

delivering a 15% performance boost, a however, the semiconductor industry is from 6T to 5T cannot happen without

50% area gain, a 40% power reduction not eager to switch to other transistor introducing structural scaling boosters

and a 35% cost decrease at device level. architectures. Some companies might such as buried power rails and wrap-

Several years ago, the industry made even decide to stay at certain nodes around contacts. Power rails provide

the transition from “good old” planar longer. But still, there are applications power to the different components of the

metal-oxide-semiconductor field-effect – such as machine learning, big data chip and are traditionally implemented

transistor (MOSFET) to FinFET transistor analysis and data center servers – that as metal lines in the chip’s back-end-

architectures in order to maintain this will require the latest “universal” CMOS of-line (BEOL) (i.e., the M int and M1

scaling path. In a FinFET, the channel solutions. With such a universal CMOS layers). There, however, they occupy

between source and drain terminals is in solution, one and the same transistor considerable space. In a buried power rail

the form of a fin. The gate wraps around architecture in one and the same construct, the power rails are buried in

this 3D channel, providing control from

three sides of the channel. This multi-gate

structure could eliminate short-channel

effects, which started to degrade the

transistor’s performance at reduced gate

lengths. Superior short-channel control is

crucial because it sets the foundations of

device scaling-–allowing shorter channel

lengths and lower operating voltages.

In 2012, the first commercial 22nm

FinFETs were introduced. Since then,

FinFET architectures were improved Figure 1: Natural evolution from FinFET to nanosheet.

43

Chip Scale Review May • June • 2020 [ChipScaleReview.com] 43