Page 45 - Chip Scale Review_November-December_2023-digital

P. 45

®

®

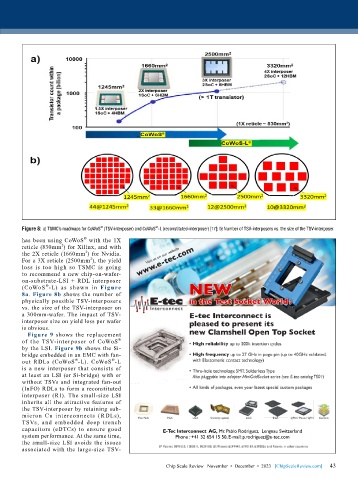

Figure 8: a) TSMC’s roadmaps for CoWoS (TSV-interposer) and CoWoS -L (reconstituted-interposer) [17]; b) Number of TSV-interposers vs. the size of the TSV-interposer.

®

has been using CoWoS with the 1X

reticle (830mm ) for Xilinx, and with

2

2

the 2X reticle (1660mm ) for Nvidia.

For a 3X reticle (2500mm ), the yield

2

loss is too high so TSMC is going

to recommend a new chip-on-wafer-

on-substrate-LSI + RDL interposer

(CoWoS -L) as show n i n Figure

®

8a. Figure 8b shows the number of

physically possible TSV-interposers

vs. the size of the TSV-interposer on

a 300mm-wafer. The impact of TSV-

interposer size on yield loss per wafer

is obvious.

Figure 9 shows the replacement

®

of the TSV-interposer of CoWoS

by the LSI. Figure 9b shows the Si-

bridge embedded in an EMC with fan-

®

out RDLs (CoWoS -L). CoWoS -L

®

is a new interposer that consists of

at least an LSI (or Si-bridge) with or

without TSVs and integrated fan-out

(InFO) RDLs to form a reconstituted

interposer (RI). The small-size LSI

inherits all the attractive features of

the TSV-interposer by retaining sub-

micron Cu interconnects (RDLs),

TSVs, and embedded deep trench

capacitors (eDTCs) to ensure good E-Tec Interconnect AG, Mr. Pablo Rodriguez, Lengnau Switzerland

system performance. At the same time, Phone : +41 32 654 15 50, E-mail: p.rodriguez@e-tec.com

the small-size LSI avoids the issues

associated with the large-size TSV-

43

Chip Scale Review November • December • 2023 [ChipScaleReview.com] 43