Page 46 - Chip Scale Review_November-December_2023-digital

P. 46

®

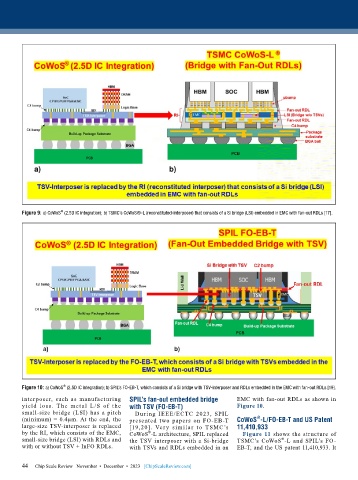

Figure 9: a) CoWoS (2.5D IC integration); b) TSMC’s CoWoS®-L (reconstituted-interposer) that consists of a Si bridge (LSI) embedded in EMC with fan-out RDLs [17].

®

Figure 10: a) CoWoS (2.5D IC integration); b) SPIL’s FO-EB-T, which consists of a Si bridge with TSV-interposer and RDLs embedded in the EMC with fan-out RDLs [19].

interposer, such as manufacturing SPIL’s fan-out embedded bridge EMC with fan-out RDLs as shown in

yield loss. T he met al L/S of the with TSV (FO-EB-T) Figure 10.

small-size bridge (LSI) has a pitch During IEEE/ECTC 2023, SPIL

®

(minimum) = 0.4µm. At the end, the presented two papers on FO-EB-T CoWoS -L/FO-EB-T and US Patent

large-size TSV-interposer is replaced [19,20]. Ver y similar to TSMC’s 11,410,933

by the RI, which consists of the EMC, CoWoS -L architecture, SPIL replaced Figure 11 shows the structure of

®

small-size bridge (LSI) with RDLs and the TSV interposer with a Si-bridge TSMC’s CoWoS -L and SPIL’s FO-

®

with or without TSV + InFO RDLs. with TSVs and RDLs embedded in an EB-T, and the US patent 11,410,933. It

44

44 Chip Scale Review November • December • 2023 [ChipScaleReview.com]