Page 35 - Chip Scale Review_November-December_2023-digital

P. 35

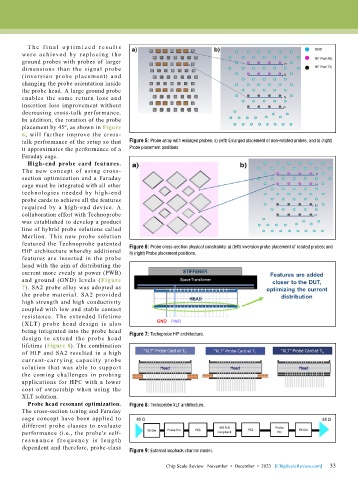

T h e f i n al o p t i m i z e d r e s u l t s

we r e a ch ieve d by r e pla ci ng t he

ground probes with probes of larger

dimensions than the signal probe

(inversion probe placement) and

changing the probe orientation inside

the probe head. A large ground probe

enables the same retur n loss and

insertion loss improvement without

decreasing cross-talk performance.

In addition, the rotation of the probe

placement by 45°, as shown in Figure

6, will further improve the cross-

talk performance of the setup so that Figure 5: Probe array with enlarged probes: a) (left) Enlarged placement of non-rotated probes; and b) (right)

it approximates the performance of a Probe placement positions.

Faraday cage.

High-end probe card features.

The new concept of using cross-

section optimization and a Faraday

cage must be integrated with all other

technologies needed by high-end

probe cards to achieve all the features

required by a high-end device. A

collaboration effort with Technoprobe

was established to develop a product

line of hybrid probe solutions called

Merlion. This new probe solution

featured the Technoprobe patented

HiP architecture whereby additional Figure 6: Probe cross-section physical constraints: a) (left) Inversion probe placement of rotated probes; and

b) (right) Probe placement positions.

features are inserted in the probe

head with the aim of distributing the

current more evenly at power (PWR)

and ground (GND) levels (Figure

7). SA2 probe alloy was adopted as

the probe material. SA2 provided

high strength and high conductivity

coupled with low and stable contact

resistance. The extended lifetime

(XLT) probe head design is also

being integrated into the probe head Figure 7: Techoprobe HIP architecture.

desig n to extend the probe head

lifetime (Figure 8). The combination

of HIP and SA2 resulted in a high

cu r rent- ca r r y i ng capacit y probe

solution that was able to support

the coming challenges in probing

applications for HPC with a lower

cost of ownership when using the

XLT solution.

Probe head resonant optimization. Figure 8: Techoprobe XLT architecture.

The cross-section tuning and Faraday

cage concept have been applied to

different probe classes to evaluate

performance (i.e., the probe’s self-

r e s o n a nc e f r e q ue nc y i s l e n g t h

dependent and therefore, probe-class

Figure 9: External loopback channel model.

33

Chip Scale Review November • December • 2023 [ChipScaleReview.com] 33