Page 63 - Chip Scale Review_November December_2021-digital

P. 63

Acknowledgment

This article is based on the article “ATE

in the Age of Convergence and Exascale

Computing,” by Matthias Stahl, Business

Development Manager, Advantest Corp.,

in GO SEMI & BEYOND, Feb. 25, 2021.

References

1. “Global Semiconductor Sales

Increase 1.9% Month-to-Month

in April; Annual Sales Projected

to Increase 19.7% in 2021, 8.8%

in 2022,” Semiconductor Industry

Association, June 9, 2021.

2. https://www.lanl.gov/projects/

exascale-computing-projects

3. T. Trader, “Frontier to Meet 20MW

Exascale Power Target Set by DARPA

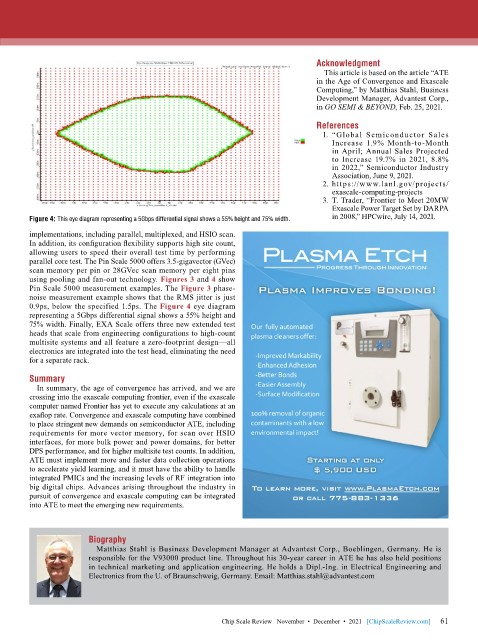

Figure 4: This eye diagram representing a 5Gbps differential signal shows a 55% height and 75% width. in 2008,” HPCwire, July 14, 2021.

implementations, including parallel, multiplexed, and HSIO scan.

In addition, its configuration flexibility supports high site count,

allowing users to speed their overall test time by performing

parallel core test. The Pin Scale 5000 offers 3.5-gigavector (GVec)

scan memory per pin or 28GVec scan memory per eight pins

using pooling and fan-out technology. Figures 3 and 4 show

Pin Scale 5000 measurement examples. The Figure 3 phase-

noise measurement example shows that the RMS jitter is just

0.9ps, below the specified 1.5ps. The Figure 4 eye diagram

representing a 5Gbps differential signal shows a 55% height and

75% width. Finally, EXA Scale offers three new extended test

heads that scale from engineering configurations to high-count

multisite systems and all feature a zero-footprint design—all

electronics are integrated into the test head, eliminating the need

for a separate rack.

Summary

In summary, the age of convergence has arrived, and we are

crossing into the exascale computing frontier, even if the exascale

computer named Frontier has yet to execute any calculations at an

exaflop rate. Convergence and exascale computing have combined

to place stringent new demands on semiconductor ATE, including

requirements for more vector memory, for scan over HSIO

interfaces, for more bulk power and power domains, for better

DPS performance, and for higher multisite test counts. In addition,

ATE must implement more and faster data collection operations

to accelerate yield learning, and it must have the ability to handle

integrated PMICs and the increasing levels of RF integration into

big digital chips. Advances arising throughout the industry in

pursuit of convergence and exascale computing can be integrated

into ATE to meet the emerging new requirements.

Biography

Matthias Stahl is Business Development Manager at Advantest Corp., Boeblingen, Germany. He is

responsible for the V93000 product line. Throughout his 30-year career in ATE he has also held positions

in technical marketing and application engineering. He holds a Dipl.-Ing. in Electrical Engineering and

Electronics from the U. of Braunschweig, Germany. Email: Matthias.stahl@advantest.com

61

Chip Scale Review November • December • 2021 [ChipScaleReview.com] 61