Page 62 - Chip Scale Review_November December_2021-digital

P. 62

such as DPS boards that do not require

a lot of vector memory, such integration

can eliminate the need for an additional

memory chip, resulting in more fully-

independent pins in a small form factor.

There are several other factors

to consider when choosing ATE for

semiconductor devices targeting

convergence and exascale computing

applications. Choose a platform that

can be configured to scale from an

engineering station to a full high-volume

multisite production system that can

cover all application segments. Choose

a system that is compatible with your

existing device under test (DUT) interface

boards while offering a seamless upgrade

path to larger load boards. Water-cooled

instruments can achieve the highest levels

of accuracy and repeatability. Still other

factors to consider include instrument and

software compatibility.

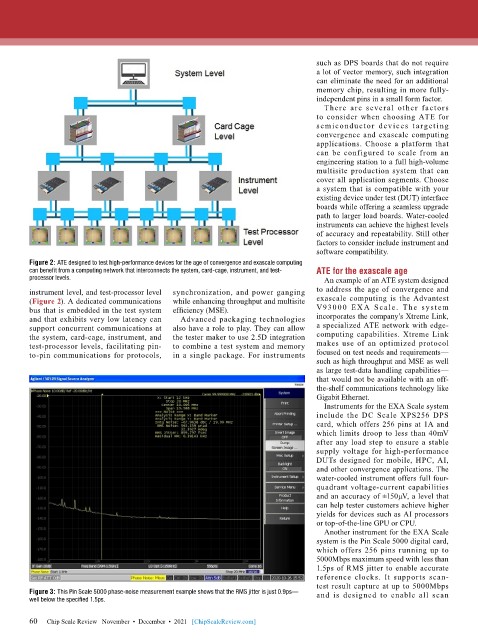

Figure 2: ATE designed to test high-performance devices for the age of convergence and exascale computing

can benefit from a computing network that interconnects the system, card-cage, instrument, and test- ATE for the exascale age

processor levels. An example of an ATE system designed

instrument level, and test-processor level synchronization, and power ganging to address the age of convergence and

(Figure 2). A dedicated communications while enhancing throughput and multisite exascale computing is the Advantest

bus that is embedded in the test system efficiency (MSE). V930 0 0 EX A Scale. T he system

and that exhibits very low latency can Advanced packaging technologies incorporates the company’s Xtreme Link,

support concurrent communications at also have a role to play. They can allow a specialized ATE network with edge-

the system, card-cage, instrument, and the tester maker to use 2.5D integration computing capabilities. Xtreme Link

test-processor levels, facilitating pin- to combine a test system and memory makes use of an optimized protocol

to-pin communications for protocols, in a single package. For instruments focused on test needs and requirements—

such as high throughput and MSE as well

as large test-data handling capabilities—

that would not be available with an off-

the-shelf communications technology like

Gigabit Ethernet.

Instruments for the EXA Scale system

include the DC Scale XPS256 DPS

card, which offers 256 pins at 1A and

which limits droop to less than 40mV

after any load step to ensure a stable

supply voltage for high-performance

DUTs designed for mobile, HPC, AI,

and other convergence applications. The

water-cooled instrument offers full four-

quadrant voltage-current capabilities

and an accuracy of ±150µV, a level that

can help tester customers achieve higher

yields for devices such as AI processors

or top-of-the-line GPU or CPU.

Another instrument for the EXA Scale

system is the Pin Scale 5000 digital card,

which offers 256 pins running up to

5000Mbps maximum speed with less than

1.5ps of RMS jitter to enable accurate

reference clocks. It supports scan-

test result capture at up to 5000Mbps

Figure 3: This Pin Scale 5000 phase-noise measurement example shows that the RMS jitter is just 0.9ps— and is designed to enable all scan

well below the specified 1.5ps.

60 Chip Scale Review November • December • 2021 [ChipScaleReview.com]

60