Page 48 - Chip Scale Review_September-October_2023-digital

P. 48

interconnect layers (M z ) used for

power delivery. A more randomized

configuration, commonly used for

signal routing in M x and M y layers,

contributes to increased heating of the

interconnect layers.

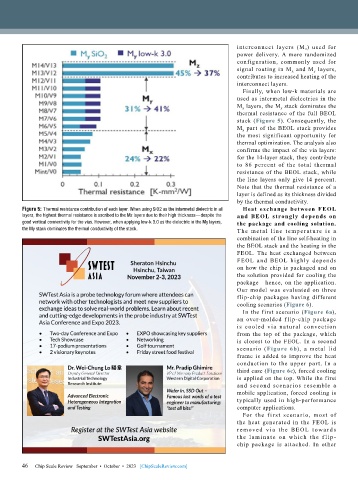

Finally, when low-k materials are

used as intermetal dielectrics in the

M y layers, the M y stack dominates the

thermal resistance of the full BEOL

stack (Figure 5). Consequently, the

M y part of the BEOL stack provides

the most significant opportunity for

thermal optimization. The analysis also

confirms the impact of the via layers:

for the 14-layer stack, they contribute

to 86 percent of the total thermal

resistance of the BEOL stack, while

the line layers only give 14 percent.

Note that the thermal resistance of a

layer is defined as its thickness divided

by the thermal conductivity.

Figure 5: Thermal resistance contribution of each layer. When using SiO2 as the intermetal dielectric in all Heat exchange between FEOL

layers, the highest thermal resistance is ascribed to the Mz layers due to their high thickness—despite the and BEOL strongly depends on

good vertical connectivity for the vias. However, when applying low-k 3.0 as the dielectric in the My layers, the package and cooling solution.

the My stack dominates the thermal conductivity of the stack. T he met al li ne temperat u re is a

combination of the line self-heating in

the BEOL stack and the heating in the

FEOL. The heat exchanged between

FEOL and BEOL highly depends

on how the chip is packaged and on

the solution provided for cooling the

package—hence, on the application.

Our model was evaluated on three

flip-chip packages having different

cooling scenarios (Figure 6).

In the first scenario (Figure 6a),

an over-molded f lip-chip package

is cooled via nat u ral convection

from the top of the package, which

is closest to the FEOL. In a second

scenario (Figure 6b), a metal lid

frame is added to improve the heat

conduction to the upper part. In a

third case (Figure 6c), forced cooling

is applied on the top. While the first

and second scenarios resemble a

mobile application, forced cooling is

typically used in high-performance

computer applications.

For the f irst scenar io, most of

the heat generated in the FEOL is

r e move d v ia t he BEOL t owa rd s

t he la m i nate on wh ich t he f lip -

chip package is attached. In other

46

46 Chip Scale Review September • October • 2023 [ChipScaleReview.com]