Page 17 - Chip Scale Review_July August_2023-digital

P. 17

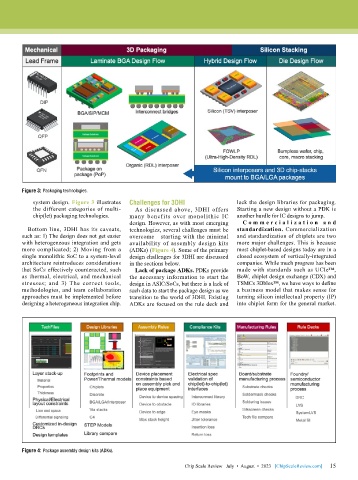

Figure 3: Packaging technologies.

system design. Figure 3 illustrates Challenges for 3DHI lack the design libraries for packaging.

the different categories of multi- As discussed above, 3DHI offers Starting a new design without a PDK is

chip(let) packaging technologies. many benefits over monolithic IC another hurdle for IC designs to jump.

design. However, as with most emerging C o m m e r c i a l i z at i o n a n d

Bottom line, 3DHI has its caveats, technologies, several challenges must be standardization. Commercialization

such as: 1) The design does not get easier overcome—starting with the minimal and standardization of chiplets are two

with heterogeneous integration and gets availability of assembly design kits more major challenges. This is because

more complicated; 2) Moving from a (ADKs) (Figure 4). Some of the primary most chiplet-based designs today are in a

single monolithic SoC to a system-level design challenges for 3DHI are discussed closed ecosystem of vertically-integrated

architecture reintroduces considerations in the sections below. companies. While much progress has been

that SoCs effectively counteracted, such Lack of package ADKs. PDKs provide made with standards such as UCIe™,

as thermal, electrical, and mechanical the necessary information to start the BoW, chiplet design exchange (CDX) and

stresses; and 3) The correct tools, design in ASIC/SoCs, but there is a lack of TSMCs 3Dblox™, we have ways to define

methodologies, and team collaboration such data to start the package design as we a business model that makes sense for

approaches must be implemented before transition to the world of 3DHI. Existing turning silicon intellectual property (IP)

designing a heterogeneous integration chip. ADKs are focused on the rule deck and into chiplet form for the general market.

Figure 4: Package assembly design kits (ADKs).

15

Chip Scale Review July • August • 2023 [ChipScaleReview.com] 15