Page 16 - Chip Scale Review_January February_2023-digital

P. 16

on a temporary carrier wafer using

temporary adhesives and then molded

and transferred to another carrier

wafer using a wafer supporting system.

This sequence is common for all the

HIFOM slices. For the base HIFOM

(i.e., on the bottom), multiple RDLs

are deposited using polymer dielectrics

and electroplated Cu interconnects.

After RDL fabrication, the HIFOM

is flipped again and the overmold is

ground off using the typical backgrind

process. This is a simple process

that can be carried out before RDL

fabrication and one carrier transferring

step can be removed.

For the upper HIFOM slice, the

process flow is similar to that used

for the base HIFOM. The number of

RDLs would be optimized depending

on the pad locations of the memory

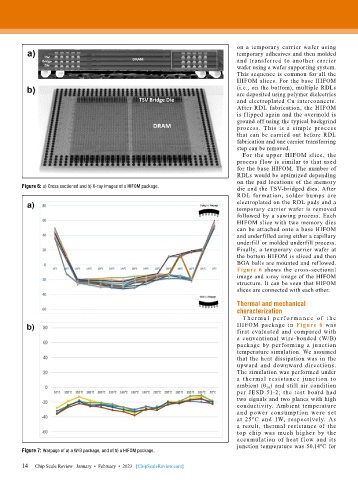

Figure 6: a) Cross sectioned and b) X-ray images of a HIFOM package. die and the TSV-bridged dies. After

RDL formation, solder bumps are

electroplated on the RDL pads and a

temporary carrier wafer is removed

followed by a sawing process. Each

HIFOM slice with two memory dies

can be attached onto a base HIFOM

and underfilled using either a capillary

underfill or molded underfill process.

Finally, a temporary carrier wafer at

the bottom HIFOM is sliced and then

BGA balls are mounted and reflowed.

Figure 6 shows the cross-sectional

image and x-ray image of the HIFOM

structure. It can be seen that HIFOM

slices are connected with each other.

Thermal and mechanical

characterization

T h e r m a l p e r f o r m a n c e o f t h e

HIFOM package in Figure 6 was

first evaluated and compared with

a conventional wire-bonded (W/B)

package by performing a junction

temperature simulation. We assumed

that the heat dissipation was in the

upward and downward directions.

The simulation was performed under

a ther mal resist ance ju nction to

ambient (θ JA ) and still air condition

per JESD 51-2; the test board had

two signals and two planes with high

conductivity. Ambient temperature

and power consumption were set

at 25ºC and 1W, respectively. As

a result, thermal resistance of the

top chip was much higher by the

accumulation of heat f low and its

junction temperature was 50.14ºC for

Figure 7: Warpage of a) a W/B package, and of b) a HIFOM package.

14

14 Chip Scale Review January • February • 2023 [ChipScaleReview.com]