Page 13 - Chip Scale Review_May June_2022-digital

P. 13

The next frontier: Enabling Moore’s Law using

heterogeneous integration

By Raja Swaminathan [AMD]

T he explosion of connected by innovations outside of the raw silicon. costs are not just a result of inflationary

devices over the last 40 years

rights of being in the top 500 supercomputers.

and complexity of these new nodes.

in our industry has driven an The demand for HPC is not simply bragging pressure but based on the underlying physics

explosion of semiconductor content riding These devices are solving problems that The next aspect of the slowdown in node

the back of Moore’s Law. Starting with the are pressing for humanity including drug introductions is that scaling factors are

personal computer cycle then continuing with discovery, climate models, new energy diverging between different intellectual

smartphones and Internet of Things (IoT) exploration and many more. Today’s best property (IP) types, with static random-

devices, silicon has permeated every aspect compute platforms only whet our appetite for access memory (SRAM) and especially

of our lives. This explosion of semiconductor more as the possibilities for solution finding analog circuits lagging well behind the

content in everything from devices in our become more compelling. scale factors of logic. This leads to the chip-

pockets to integrated into our clothing has led level view of area scaling where, with a

to the birth and growth of a new era of high- Demand for computation is mix of logic, SRAM and analog content,

performance computing (HPC), as all the outpacing Moore’s Law we will not be able to shrink chip designs

data being generated is processed into useful The next bit of sobering data regards appreciably toward the end of this decade.

information to improve our lives. the much-discussed cracks in Moore’s This illustrates that the irresistible force

From the cloud to the edge, and Law. As we know, silicon technology node of compute demand is colliding with the

from artificial intelligence (AI) to 5G introductions have been slowing down, and immovable object of device physics, creating

communications, the insatiable demand for simultaneously delivering less benefit, while an environment where new architecture

HPC has become a driving force within the at the same time, the costs per yielded mm approaches and non-device innovations are

2

microelectronics industry and it will shape of silicon are going up. This is particularly critical for our ecosystem.

the next several generations of technology challenging because the semiconductor It is now recognized that conventional

and design innovation. The demand for industry has thrived on delivering more computing is approaching fundamental limits

compute is accelerating rapidly with the performance and features in each generation in energy efficiency. Historical trends show

doubling of HPC system performance every by adding transistors. With these trends, the that general purpose CPU energy efficiency

1.2 years. This trend is much faster than cost per transistor will stop scaling in the next worsens with higher performance, so new

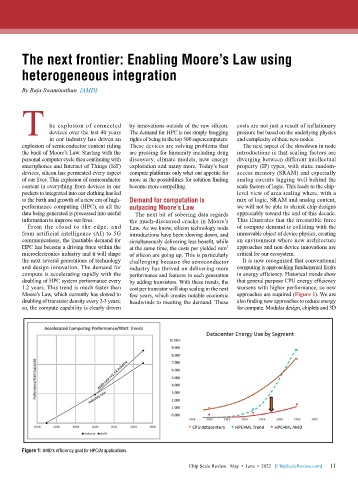

Moore’s Law, which currently has slowed to few years, which creates notable economic approaches are required (Figure 1). We are

doubling of transistor density every 2-3 years; headwinds to meeting the demand. These also finding new approaches to reduce energy

so, the compute capability is clearly driven for compute. Modular design, chiplets and 3D

Figure 1: AMD’s efficiency goal for HPC/AI applications.

Chip Scale Review May • June • 2022 [ChipScaleReview.com] 11 11