Page 26 - Chip Scale Review_November December_2021-digital

P. 26

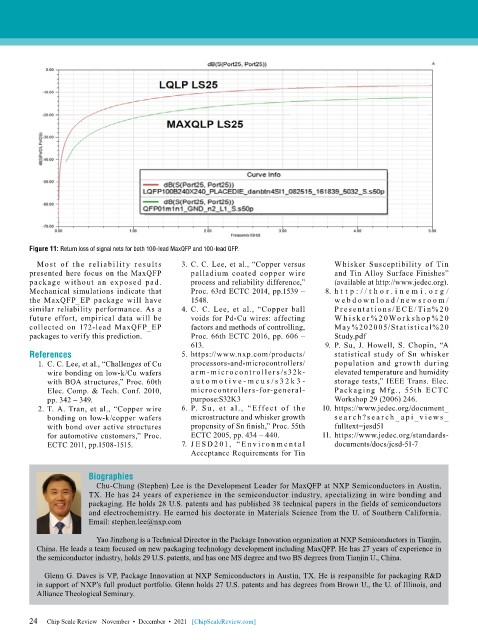

Figure 11: Return loss of signal nets for both 100-lead MaxQFP and 100-lead QFP.

Most of t he reliabilit y result s 3. C. C. Lee, et al., “Copper versus Whisker Susceptibility of Tin

presented here focus on the MaxQFP palladium coated copper wire and Tin Alloy Surface Finishes”

package without an exposed pad. process and reliability difference,” (available at http://www.jedec.org).

Mechanical simulations indicate that Proc. 63rd ECTC 2014, pp.1539 – 8. h t t p :/ / t ho r . i n e m i . o r g /

the MaxQFP_EP package will have 1548. w e b d o w n l o a d / ne ws r o om /

similar reliability performance. As a 4. C. C. Lee, et al., “Copper ball P r e s e nt at ion s / E C E / Ti n% 2 0

future effort, empirical data will be voids for Pd-Cu wires: affecting W h i s k e r % 20Wo r k s ho p % 20

collected on 172-lead MaxQFP_EP factors and methods of controlling, May%202005/Statistical%20

packages to verify this prediction. Proc. 66th ECTC 2016, pp. 606 – Study.pdf

613. 9. P. Su, J. Howell, S. Chopin, “A

References 5. https://www.nxp.com/products/ statistical study of Sn whisker

1. C. C. Lee, et al., “Challenges of Cu processors-and-microcontrollers/ population and growth during

wire bonding on low-k/Cu wafers a r m -m ic ro c ont rol le r s /s32k- elevated temperature and humidity

with BOA structures,” Proc. 60th a ut o mo t i v e - m c u s / s 3 2 k 3 - storage tests,” IEEE Trans. Elec.

Elec. Comp. & Tech. Conf. 2010, microcontrollers-for-general- Packaging Mfg., 55th ECTC

pp. 342 – 349. purpose:S32K3 Workshop 29 (2006) 246.

2. T. A. Tran, et al., “Copper wire 6. P. Su , et al., “Ef fect of t he 10. https://www.jedec.org/document_

bonding on low-k/copper wafers microstructure and whisker growth se a r c h? se a r c h _ ap i _v i e w s _

with bond over active structures propensity of Sn finish,” Proc. 55th fulltext=jesd51

for automotive customers,” Proc. ECTC 2005, pp. 434 – 440. 11. https://www.jedec.org/standards-

ECTC 2011, pp.1508-1515. 7. J E S D 201, “ E n v i r o n m e n t a l documents/docs/jesd-51-7

Acceptance Requirements for Tin

Biographies

Chu-Chung (Stephen) Lee is the Development Leader for MaxQFP at NXP Semiconductors in Austin,

TX. He has 24 years of experience in the semiconductor industry, specializing in wire bonding and

packaging. He holds 28 U.S. patents and has published 38 technical papers in the fields of semiconductors

and electrochemistry. He earned his doctorate in Materials Science from the U. of Southern California.

Email: stephen.lee@nxp.com

Yao Jinzhong is a Technical Director in the Package Innovation organization at NXP Semiconductors in Tianjin,

China. He leads a team focused on new packaging technology development including MaxQFP. He has 27 years of experience in

the semiconductor industry, holds 29 U.S. patents, and has one MS degree and two BS degrees from Tianjin U., China.

Glenn G. Daves is VP, Package Innovation at NXP Semiconductors in Austin, TX. He is responsible for packaging R&D

in support of NXP’s full product portfolio. Glenn holds 27 U.S. patents and has degrees from Brown U., the U. of Illinois, and

Alliance Theological Seminary.

24 Chip Scale Review November • December • 2021 [ChipScaleReview.com]

24