Page 29 - Chip Scale Review_November December_2022-digital

P. 29

1. Automatically-generated tests that

leverage consistent tool sets provide

the most value for the least amount of

effort.

2. Clean, consistent hardware setups

produce solid results.

3. SLT provides solid value—finding

errors not seen elsewhere.

4. Technology does not sit still, and

there is no end in sight to the device

complexity that will need to be tested.

st

Test moving into the 21 century

Device validation/characterization,

functional test at ATE, structural test,

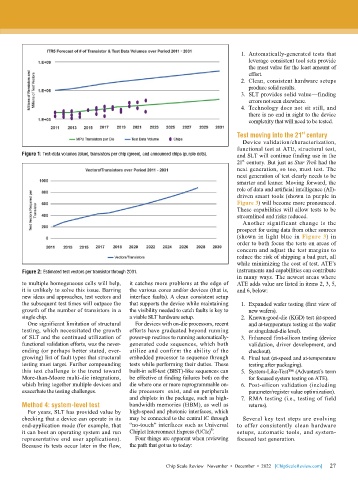

Figure 1: Test-data volumes (blue), transistors per chip (green), and announced chips (purple dots). and SLT will continue finding use in the

st

21 century. But just as Star Trek had the

next generation, so too, must test. The

next generation of test clearly needs to be

smarter and leaner. Moving forward, the

role of data and artificial intelligence (AI)-

driven smart tools (shown in purple in

Figure 3) will become more pronounced.

These capabilities will allow tests to be

streamlined and risks reduced.

Another significant change is the

prospect for using data from other sources

(shown in light blue in Figure 3) in

order to both focus the tests on areas of

concern and adjust the test margins to

reduce the risk of shipping a bad part, all

while minimizing the cost of test. ATE’s

Figure 2: Estimated test vectors per transistor through 2031. instruments and capabilities can contribute

in many ways. The newest areas where

to multiple homogeneous cells will help, it catches more problems at the edge of ATE adds value are listed in items 2, 3, 5,

it is unlikely to solve this issue. Barring the various cores and/or devices (that is, and 6, below:

new ideas and approaches, test vectors and interface faults). A clean consistent setup

the subsequent test times will outpace the that supports the device while maintaining 1. Expanded wafer testing (first view of

growth of the number of transistors in a the visibility needed to catch faults is key to new wafers).

single chip. a viable SLT hardware setup. 2. Known-good-die (KGD) test (at-speed

One significant limitation of structural For devices with on-die processors, recent and at-temperature testing at the wafer

testing, which necessitated the growth efforts have graduated beyond running or singulated-die level).

of SLT and the continued utilization of power-up routines to running automatically- 3. Enhanced first-silicon testing (device

functional validation efforts, was the never- generated code sequences, which both validation, driver development, and

ending (or perhaps better stated, ever- utilize and confirm the ability of the checkout).

growing) list of fault types that structural embedded processor to sequence through 4. Final test (at-speed and at-temperature

testing must target. Further compounding tests while performing their duties. These testing after packaging).

this test challenge is the trend toward built-in self-test (BIST)-like sequences can 5. System-Like-Test™ (Advantest’s term

More-than-Moore multi-die integrations, be effective at finding failures both on the for focused system testing on ATE).

which bring together multiple devices and die where one or more reprogrammable on- 6. Post-silicon validation (including

exacerbate the testing challenges. die processors exist, and on peripherals parameter/register value optimization).

and chiplets in the package, such as high- 7. RMA testing (i.e., testing of field

Method 4: system-level test bandwidth memories (HBM), as well as returns).

For years, SLT has provided value by high-speed and photonic interfaces, which

checking that a device can operate in its may be connected to the central IC through Several key test steps are evolving

end-application mode (for example, that “no-touch” interfaces such as Universal to offer consistently clean hardware

®

it can boot an operating system and run Chiplet Interconnect Express (UCIe) . setups, automatic tools, and system-

representative end user applications). Four things are apparent when reviewing focused test generation.

Because its tests occur later in the flow, the path that got us to today:

27

Chip Scale Review November • December • 2022 [ChipScaleReview.com] 27