Page 21 - Chip Scale Review_January February_2022-digital

P. 21

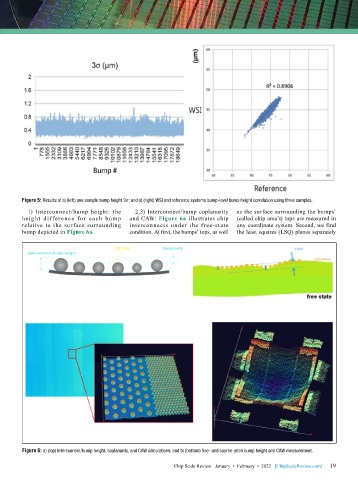

Figure 5: Results of a) (left) one sample bump height 3σ; and b) (right) WSI and reference systems bump-level bump height correlation using three samples.

1) Interconnect/bump height: the 2,3) Interconnect/bump coplanarity as the surface surrounding the bumps’

height difference for each bu mp and CAW: Figure 6a illustrates chip (called chip area’s) tops are measured in

relative to the surface surrounding interconnects under the free-state any coordinate system. Second, we find

bump depicted in Figure 6a. condition. At first, the bumps’ tops, as well the least squares (LSQ) planes separately

Figure 6: a) (top) Interconnect/bump height, coplanarity, and CAW calculations; and b) (bottom) fine- and coarse-pitch bump height and CAW measurement.

19

Chip Scale Review January • February • 2022 [ChipScaleReview.com] 19