Page 11 - Chip Scale Review_May June_2023-digital

P. 11

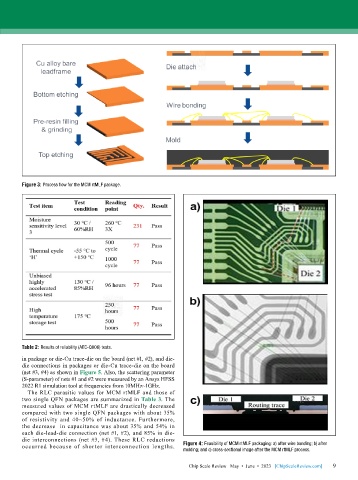

Figure 3: Process flow for the MCM rtMLF package.

Table 2: Results of reliability (AEC-Q006) tests.

in package or die-Cu trace-die on the board (net #1, #2), and die-

die connections in packages or die-Cu trace-die on the board

(net #3, #4) as shown in Figure 5. Also, the scattering parameter

(S-parameter) of nets #1 and #2 were measured by an Ansys HFSS

2022 R1 simulation tool at frequencies from 10MHz~1GHz.

The RLC parasitic values for MCM rtMLF and those of

two single QFN packages are summarized in Table 3. The

measured values of MCM rtMLF are drastically decreased

compared with two single QFN packages with about 35%

of resistivity and 40~50% of inductance. Furthermore,

the decrease in capacitance was about 35% and 54% in

each die-lead-die connection (net #1, #2), and 85% in die-

die interconnections (net #3, #4). These RLC reductions

occurred because of shorter interconnection lengths. Figure 4: Feasibility of MCM rtMLF packaging: a) after wire bonding; b) after

molding; and c) cross-sectional image after the MCM rtMLF process.

Chip Scale Review May • June • 2023 [ChipScaleReview.com] 9 9