Page 56 - Chip Scale Review Sep Oct_2022-digital

P. 56

®

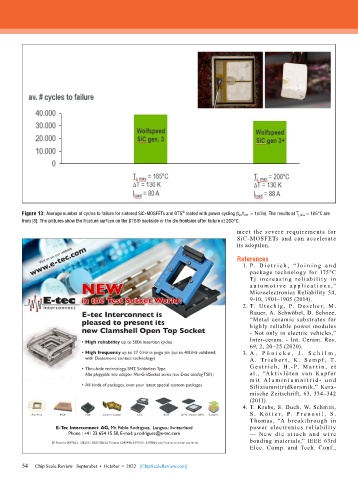

Figure 13: Average number of cycles to failure for sintered SiC-MOSFETs and DTS tested with power cycling (t on /t off = 1s/2s). The results at T j,max = 165°C are

from [8]. The pictures show the fracture surface on the DTS® backside or the die frontside after failure at 200°C.

meet the severe requirements for

SiC-MOSFETs and can accelerate

its adoption.

References

1. P. D i e t r i c h , “ J o i n i ng a n d

package technology for 175°C

Tj i n c r e a si ng r el ia bi l it y i n

a ut omo t i v e a p p l i c a t i o n s ,”

Microelectronics Reliability 54,

9-10, 1901–1905 (2014).

2. T. Ut s c h ig , P. D e s c h e r, M .

Rauer, A. Schwöbel, D. Schnee,

“Metal ceramic substrates for

highly reliable power modules

- Not only in electric vehicles,”

Inter-ceram. - Int. Ceram. Rev.

69, 2, 20–25 (2020).

3. A . P ö n i c k e , J . S c h i l m ,

A . Tr i e b e r t , K . S e m p f , T.

G e s t r i c h , H .- P. M a r t i n , e t

al., “A k t ivlöt e n von Kupfe r

mi t A l u mi ni u m ni t r i d - u n d

Siliziumnitridkeramik,” Kera-

mische Zeitschrift, 63, 334–342

(2011).

4. T. Krebs, S. Duch, W. Schmitt,

S . K ö t t e r , P. P r e n o s i l , S .

Thomas, “A breakthrough in

E-Tec Interconnect AG, Mr. Pablo Rodriguez, Lengnau Switzerland power elect ronics reliabilit y

Phone : +41 32 654 15 50, E-mail: p.rodriguez@e-tec.com — New d ie at t a ch a nd w i re

bonding materials,” IEEE 63rd

Elec. Comp. and Tech. Conf.,

54 Chip Scale Review September • October • 2022 [ChipScaleReview.com]

54