Page 28 - Chip Scale Review_January February_2022-digital

P. 28

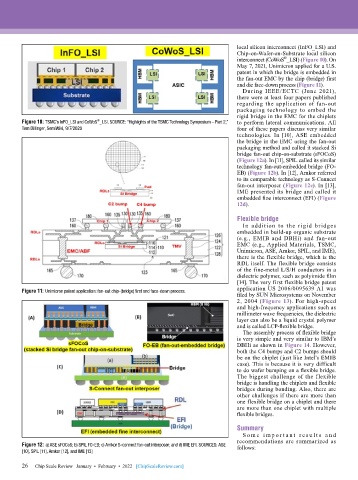

local silicon interconnect (InFO_LSI) and

Chip-on-Wafer-on-Substrate local silicon

®

interconnect (CoWoS _LSI) (Figure 10). On

May 7, 2021, Unimicron applied for a U.S.

patent in which the bridge is embedded in

the fan-out EMC by the chip (bridge) first

and die face-down process (Figure 11).

During IEEE/ECTC (June 2021),

there were at least four papers published

regarding the application of fan-out

packaging technology to embed the

rigid bridge in the EMC for the chiplets

®

Figure 10: TSMC’s InFO_LSI and CoWoS _LSI. SOURCE: “Highlights of the TSMC Technology Symposium – Part 2,” to perform lateral communications. All

Tom Dillinger, SemiWiki, 9/7/2020 four of these papers discuss very similar

technologies. In [10], ASE embedded

the bridge in the EMC using the fan-out

packaging method and called it stacked Si

bridge fan-out chip-on-substrate (sFOCoS)

(Figure 12a). In [11], SPIL called its similar

technology fan-out-embedded bridge (FO-

EB) (Figure 12b). In [12], Amkor referred

to its comparable technology as S-Connect

fan-out interposer (Figure 12c). In [13],

IME presented its bridge and called it

embedded fine interconnect (EFI) (Figure

12d).

Flexible bridge

In addition to the rigid bridges

embedded in build-up organic substrate

(e.g., EMIB and DBHi) and fan-out

EMC (e.g., Applied Materials, TSMC,

Unimicron, ASE, Amkor, SPIL, and IME),

there is the flexible bridge, which is the

RDL itself. The flexible bridge consists

of the fine-metal L/S/H conductors in a

dielectric polymer, such as polyimide film

[14]. The very first flexible bridge patent

application US 2006/0095639 A1 was

Figure 11: Unimicron patent application: fan-out chip-(bridge) first and face-down process.

filed by SUN Microsystems on November

2, 2004 (Figure 13). For high-speed

and high-frequency applications such as

millimeter wave frequencies, the dielectric

layer can also be a liquid crystal polymer

and is called LCP-flexible bridge.

The assembly process of flexible bridge

is very simple and very similar to IBM’s

DBHi as shown in Figure 14. However,

both the C4 bumps and C2 bumps should

be on the chiplet (just like Intel’s EMIB

case). This is because it is very difficult

to do wafer bumping on a flexible bridge.

The biggest challenge of the flexible

bridge is handling the chiplets and flexible

bridges during bonding. Also, there are

other challenges if there are more than

one flexible bridge on a chiplet and there

are more than one chiplet with multiple

flexible bridges.

Summary

S o m e i m p o r t a n t r e s u l t s a n d

recommendations are summarized as

Figure 12: a) ASE sFOCoS; b) SPIL FO-EB; c) Amkor S-connect fan-out interposer; and d) IME EFI. SOURCES: ASE follows:

[10], SPIL [11], Amkor [12], and IME [13]

26

26 Chip Scale Review January • February • 2022 [ChipScaleReview.com]