Page 30 - Chip Scale Review_January February_2022-digital

P. 30

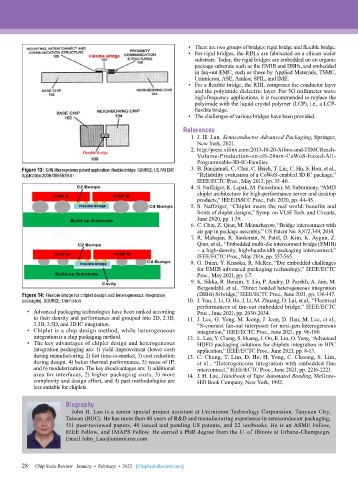

• There are two groups of bridges: rigid bridge and flexible bridge.

• For rigid bridges, the RDLs are fabricated on a silicon wafer

substrate. Today, the rigid bridges are embedded on an organic

package substrate such as the EMIB and DBHi, and embedded

in fan-out EMC, such as those by Applied Materials, TSMC,

Unimicron, ASE, Amkor, SPIL, and IME.

• For a flexible bridge, the RDL comprises the conductor layer

and the polyimide dielectric layer. For 5G millimeter wave

high-frequency applications, it is recommended to replace the

polyimide with the liquid crystal polymer (LCP), i.e., a LCP-

flexible bridge.

• The challenges of various bridges have been provided.

References

1. J. H. Lau, Semiconductor Advanced Packaging, Springer,

New York, 2021.

2. http://press.xilinx.com/2013-10-20-Xilinx-and-TSMCReach-

Volume-Production-on-all-28nm-CoWoS-based-All-

Programmable-3D-IC-Families

Figure 13: SUN Microsystems patent application: flexible bridge. SOURCE: US PATENT 3. B. Banijamali, C. Chiu, C. Hsieh, T. Lin, C. Hu, S. Hou, et al.,

Application 2006/0095639 A1 “Reliability evaluation of a CoWoS-enabled 3D IC package,”

IEEE/ECTC Proc., May 2013, pp. 35-40.

4. S. Naffziger, K. Lepak, M. Paraschour, M. Subramony, “AMD

chiplet architecture for high-performance server and desktop

products,” IEEE/ISSCC Proc., Feb. 2020, pp. 44-45.

5. S. Naffziger, “Chiplet meets the real world: benefits and

limits of chiplet designs,” Symp. on VLSI Tech. and Circuits,

June 2020, pp. 1-39.

6. C. Chiu, Z. Qian, M. Manusharow, “Bridge interconnect with

air gap in package assembly,” US Patent No. 8,872,349, 2014.

7. R. Mahajan, R. Sankman, N. Patel, D. Kim, K. Aygun, Z.

Qian, et al., “Embedded multi-die interconnect bridge (EMIB)

– a high-density, high-bandwidth packaging interconnect,”

IEEE/ECTC Proc., May 2016, pp. 557-565.

8. G. Duan, Y. Knaoka, R. McRee, “Die embedded challenges

for EMIB advanced packaging technology,” IEEE/ECTC

Proc., May 2021, pp. 1-7.

9. K. Sikka, R. Bonam, Y. Liu, P. Andry, D. Parekh, A. Jain, M.

Bergendahl, et al., “Direct bonded heterogeneous integration

Figure 14: Flexible bridge for chiplet design and heterogeneous integration (DBHi) Si bridge,” IEEE/ECTC Proc., June 2021, pp. 136-147.

packaging. SOURCE: Unimicron 10. J. You, J. Li, D. Ho, J. Li, M. Zhuang, D. Lai, et al., “Electrical

performances of fan-out embedded bridge,” IEEE/ECTC

• Advanced packaging technologies have been ranked according Proc., June 2021, pp. 2030-2034.

to their density and performance and grouped into 2D, 2.1D, 11. J. Lee, G. Yong, M. Jeong, J. Jeon, D. Han, M. Lee, et al.,

2.3D, 2.5D, and 3D IC integration. “S-connect fan-out interposer for next-gen heterogeneous

• Chiplet is a chip design method, while heterogeneous integration,” IEEE/ECTC Proc., June 2021, pp. 96-100.

integration is a chip packaging method. 12. L. Lee, Y. Chang, S. Huang, J. On, E. Lin, O. Yang, “Advanced

• The key advantages of chiplet design and heterogeneous HDFO packaging solutions for chiplets integration in HPC

integration packaging are: 1) yield improvement (lower cost) application,” IEEE/ECTC Proc., June 2021, pp. 8-13.

during manufacturing, 2) fast time-to-market, 3) cost reduction 13. C. Chong, T. Lim, D. Ho, H. Yong, C. Choong, S. Lim,

during design, 4) better thermal performance, 5) reuse of IP, et al., “Heterogeneous integration with embedded fine

and 6) modularization. The key disadvantages are: 1) additional interconnect,” IEEE/ECTC Proc., June 2021, pp. 2216-2221.

area for interfaces, 2) higher packaging costs, 3) more 14. J. H. Lau, Handbook of Tape Automated Bonding, McGraw-

complexity and design effort, and 4) past methodologies are Hill Book Company, New York, 1992.

less suitable for chiplets.

Biography

John H. Lau is a senior special project assistant at Unimicron Technology Corporation, Taoyuan City,

Taiwan (ROC). He has more than 40 years of R&D and manufacturing experience in semiconductor packaging,

511 peer-reviewed papers, 40 issued and pending US patents, and 22 textbooks. He is an ASME Fellow,

IEEE Fellow, and IMAPS Fellow. He earned a PhD degree from the U. of Illinois at Urbana-Champaign.

Email John_Lau@unimicron.com

28

28 Chip Scale Review January • February • 2022 [ChipScaleReview.com]