Page 39 - ChipScale_Jul-Aug_2020-Digital

P. 39

High-throughput, high-accuracy flip-chip bonding

By Horst Clauberg [Kulicke & Soffa Industries Inc.]

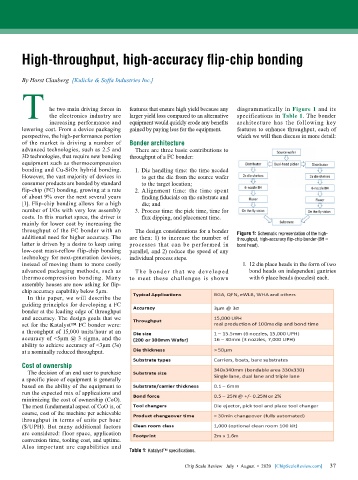

T he two main driving forces in features that ensure high yield because any diagrammatically in Figure 1 and its

the electronics industry are

equipment would quickly erode any benefits

increasing performance and larger yield loss compared to an alternative specifications in Table 1. The bonder

architecture has the following key

lowering cost. From a device packaging gained by paying less for the equipment. features to enhance throughput, each of

perspective, the high-performance portion which we will then discuss in more detail:

of the market is driving a number of Bonder architecture

advanced technologies, such as 2.5 and There are three basic contributions to

3D technologies, that require new bonding throughput of a FC bonder:

equipment such as thermocompression

bonding and Cu-SiOx hybrid bonding. 1. Die handling time: the time needed

However, the vast majority of devices in to get the die from the source wafer

consumer products are bonded by standard to the target location;

flip-chip (FC) bonding, growing at a rate 2. Alignment time: the time spent

of about 9% over the next several years finding fiducials on the substrate and

[1]. Flip-chip bonding allows for a high die; and

number of I/Os with very low assembly 3. Process time: the pick time, time for

costs. In this market space, the driver is flux dipping, and placement time.

mainly for lower cost by increasing the

throughput of the FC bonder with an The design considerations for a bonder

additional need for higher accuracy. The are then: 1) to increase the number of Figure 1: Schematic representation of the high-

throughput, high-accuracy flip-chip bonder (BH =

latter is driven by a desire to keep using processes that can be performed in bond head).

low-cost mass-reflow flip-chip bonding parallel, and 2) reduce the speed of any

technology for next-generation devices, individual process steps.

instead of moving them to more costly 1. 12 die place heads in the form of two

advanced packaging methods, such as T he bonder t hat we developed bond heads on independent gantries

thermocompression bonding. Many to meet these challenges is shown with 6 place heads (nozzles) each.

assembly houses are now asking for flip-

chip accuracy capability below 5μm.

In this paper, we will describe the

guiding principles for developing a FC

bonder at the leading edge of throughput

and accuracy. The design goals that we

set for the Katalyst™ FC bonder were:

a throughput of 15,000 units/hour at an

accuracy of <5μm @ 3 sigma, and the

ability to achieve accuracy of <3μm (3s)

at a nominally reduced throughput.

Cost of ownership

The decision of an end user to purchase

a specific piece of equipment is generally

based on the ability of the equipment to

run the expected mix of applications and

minimizing the cost of ownership (CoO).

The most fundamental aspect of CoO is, of

course, cost of the machine per achievable

throughput in terms of units per hour

($/UPH). But many additional factors

are considered: floor space, application

conversion time, tooling cost, and uptime.

Also important are capabilities and

Table 1: Katalyst™ specifications.

37

Chip Scale Review July • August • 2020 [ChipScaleReview.com] 37