Page 11 - Chip Scale Review_January February_2022-digital

P. 11

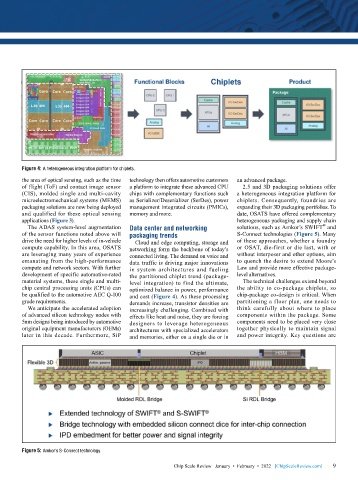

Figure 4: A heterogeneous integration platform for chiplets.

the area of optical sensing, such as the time technology then offers automotive customers an advanced package.

of flight (ToF) and contact image sensor a platform to integrate these advanced CPU 2.5 and 3D packaging solutions offer

(CIS), molded single and multi-cavity chips with complementary functions such a heterogeneous integration platform for

microelectromechanical systems (MEMS) as Serializer/Deserializer (SerDes), power chiplets. Consequently, foundries are

packaging solutions are now being deployed management integrated circuits (PMICs), expanding their 3D packaging portfolios. To

and qualified for these optical sensing memory and more. date, OSATS have offered complementary

applications (Figure 3). heterogeneous packaging and supply chain

®

The ADAS system-level augmentation Data center and networking solutions, such as Amkor’s SWIFT and

of the sensor functions noted above will packaging trends S-Connect technologies (Figure 5). Many

drive the need for higher levels of in-vehicle Cloud and edge computing, storage and of these approaches, whether a foundry

compute capability. In this area, OSATS networking form the backbone of today’s or OSAT, die-first or die last, with or

are leveraging many years of experience connected living. The demand on voice and without interposer and other options, aim

emanating from the high-performance data traffic is driving major innovations to quench the desire to extend Moore’s

compute and network sectors. With further in system architectures and fueling Law and provide more effective package-

development of specific automotive-rated the partitioned chiplet trend (package- level alternatives.

material systems, these single and multi- level integration) to find the ultimate, The technical challenges extend beyond

chip central processing units (CPUs) can optimized balance in power, performance the ability to co-package chiplets, so

be qualified to the automotive AEC Q-100 and cost (Figure 4). As these processing chip-package co-design is critical. When

grade requirements. demands increase, transistor densities are partitioning a floor plan, one needs to

We anticipate the accelerated adoption increasingly challenging. Combined with think carefully about where to place

of advanced silicon technology nodes with effects like heat and noise, they are forcing components within the package. Some

5nm designs being introduced by automotive designers to leverage heterogeneous components need to be placed very close

original equipment manufacturers (OEMs) architectures with specialized accelerators together physically to maintain signal

later in this decade. Furthermore, SiP and memories, either on a single die or in and power integrity. Key questions are

Figure 5: Amkor’s S-Connect technology.

Chip Scale Review January • February • 2022 [ChipScaleReview.com] 9 9