# Chip Scale Review®

ChipScaleReview.com

*The Future of Semiconductor Packaging*

Volume 30, Number 1

Winter 2026

## Heterogeneous wafer-scale integration: The new front line of semiconductor scaling

- Co-packaged optics: Heterogeneous integration of chiplets in switches, PICs, and EICs

- Evaluation of indium TIM cross-sectioning methods high-performance microprocessors

- Impact of die-attach voids on the thermal performance of clip-bonded packages

- Impact of wave front phase imaging on semiconductor metrology challenges

- Using polynomial regression for heterogeneous package stress modeling

- Wafer-level testing of TMR sensors using 3D magnetic field excitation

10K Pins

in 7 Days

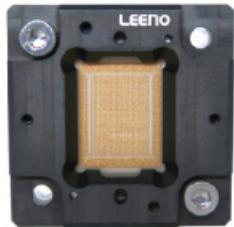

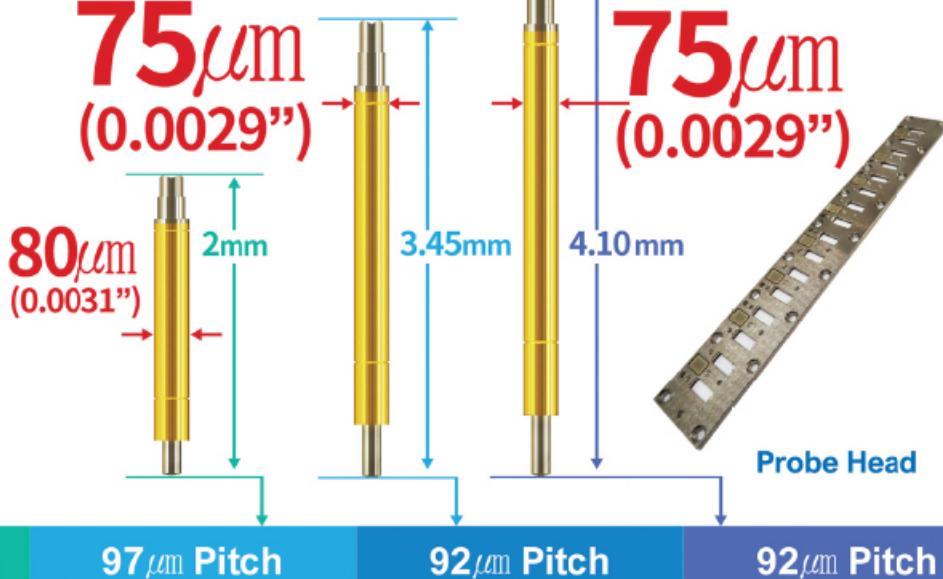

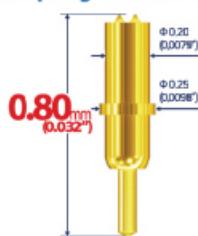

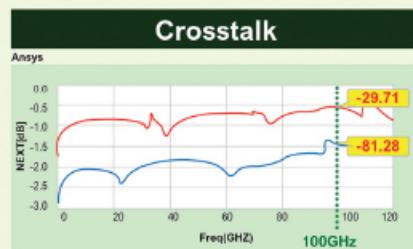

## Fine Pitch Probe &amp; Probe Head

Proven Mass Production Capability

## High Speed RF

Short Signal Path 0.80mm

with Spring Contact Probe!

## 5G MP 100GHz Coaxial Socket

▪ Pitch: 0.35mm, Array

5 Sockets

in 10 Days

# CONTENTS

Volume 30, Number 1

Winter 2026

## FEATURE ARTICLES

**5** **Heterogeneous wafer-scale integration:

The new front line of semiconductor scaling**

By Krutikesh Sahoo, Subramanian S. Iyer

[Samueli School of Engineering, University of California, Los Angeles]

**12** **Evaluation of indium TIM cross-sectioning methods on lidded

high-performance microprocessors**

By Neo Shao Ming, Song Mei Hui, Kevin Tan Bo Lin, Lee Xi Wen, Oh Zi-Ying, Foo Fang-Jie

[Advanced Micro Devices (Singapore) Pte Ltd]

**26** **Using polynomial regression for heterogeneous package stress modeling**

By Kart Leong Lim, Ji Lin

[Institute of Microelectronics (IME), Agency for Science, Technology and Research (A\*STAR)]

invent

innovate

implement

[www.EVGroup.com](http://www.EVGroup.com)

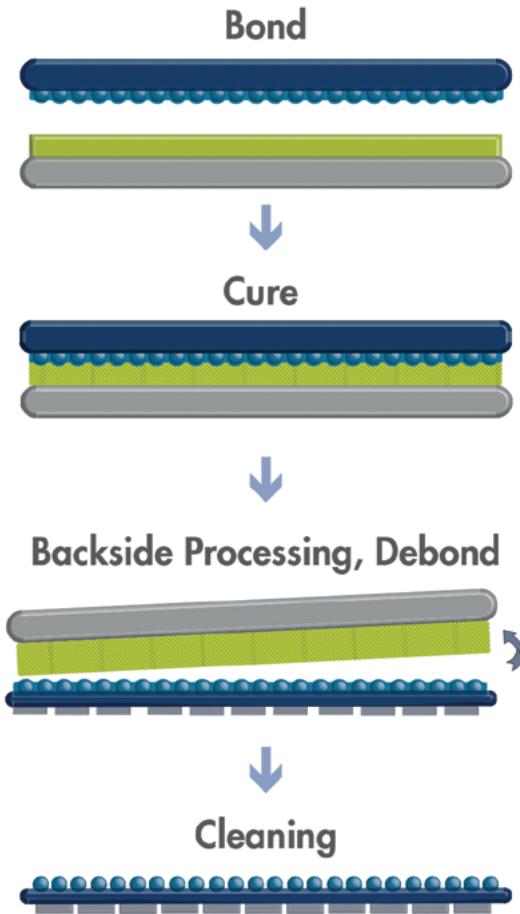

# FUSION AND HYBRID BONDING FOR HETEROGENEOUS INTEGRATION

- Enabling advanced 3D device stacking and chiplet integration for CMOS image sensors, memory and 3D system-on-chip (SoC)

- High-volume production equipment and process technology for Wafer-to-Wafer (W2W) and Die-to-Wafer (D2W) hybrid bonding

- GEMINI® FB Automated Production Wafer Bonding System delivers industry leading alignment accuracy and bonding performance

- New, unique EVG®40 D2W system provides 100% die overlay measurement with high precision and throughput for HVM

GET IN TOUCH to discuss your manufacturing needs

[www.EVGroup.com](http://www.EVGroup.com)

[\[ChipScaleReview.com\]](http://ChipScaleReview.com)

# CONTENTS

## Chip Scale Review®

ChipScaleReview.com

The Future of Semiconductor Packaging

### STAFF

**Kim Newman**

Publisher

[knewman@chipscalereview.com](mailto:knewman@chipscalereview.com)

**Lawrence Michaels**

Managing Director

Editor-in-Chief

[lmichaels@chipscalereview.com](mailto:lmichaels@chipscalereview.com)

**Debra Vogler**

Senior Technical Editor

[debravogler@me.com](mailto:debravogler@me.com)

### SUBSCRIPTION—INQUIRIES

Chip Scale Review

All subscription changes, additions, deletions to any and all subscriptions should be made by email only to [subsc@chipscalereview.com](mailto:subsc@chipscalereview.com)

Advertising Production Inquiries:

**Lawrence Michaels**

[lmichaels@chipscalereview.com](mailto:lmichaels@chipscalereview.com)

Copyright © 2026 Haley Publishing Inc.

Chip Scale Review is a registered trademark of Haley Publishing Inc. All rights reserved.

Subscriptions in the U.S. are available without charge to qualified individuals in the electronics industry.

Chip Scale Review is published four times a year with issues in Winter, Spring, Summer and Fall.

P.O. Box 2165

Morgan Hill, CA 95038

E-Mail: [info@chipscalereview.com](mailto:info@chipscalereview.com)

Printed in the United States

## FEATURE ARTICLES (continued)

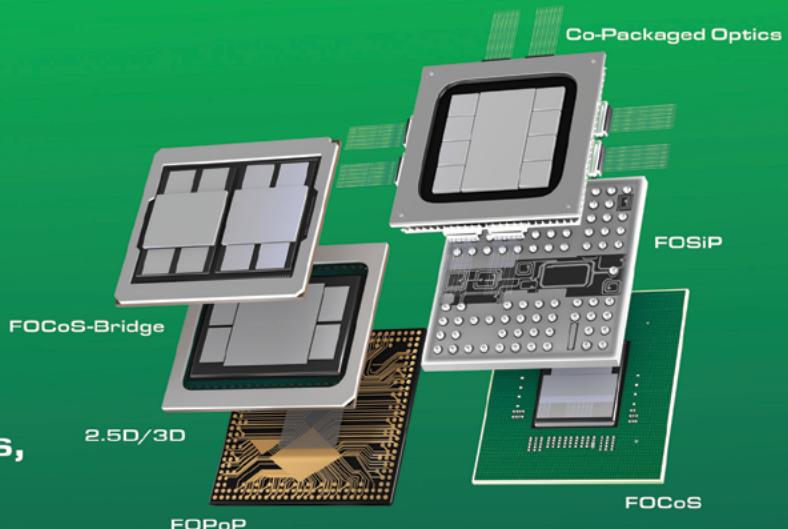

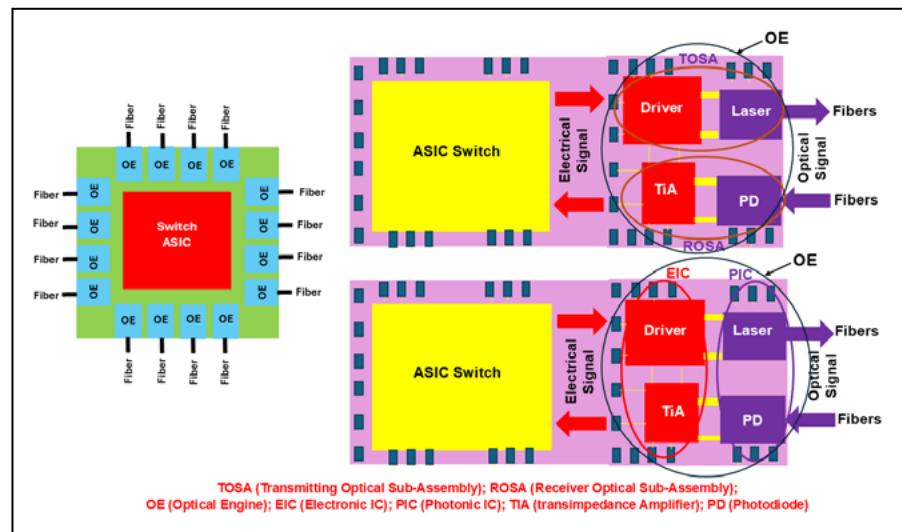

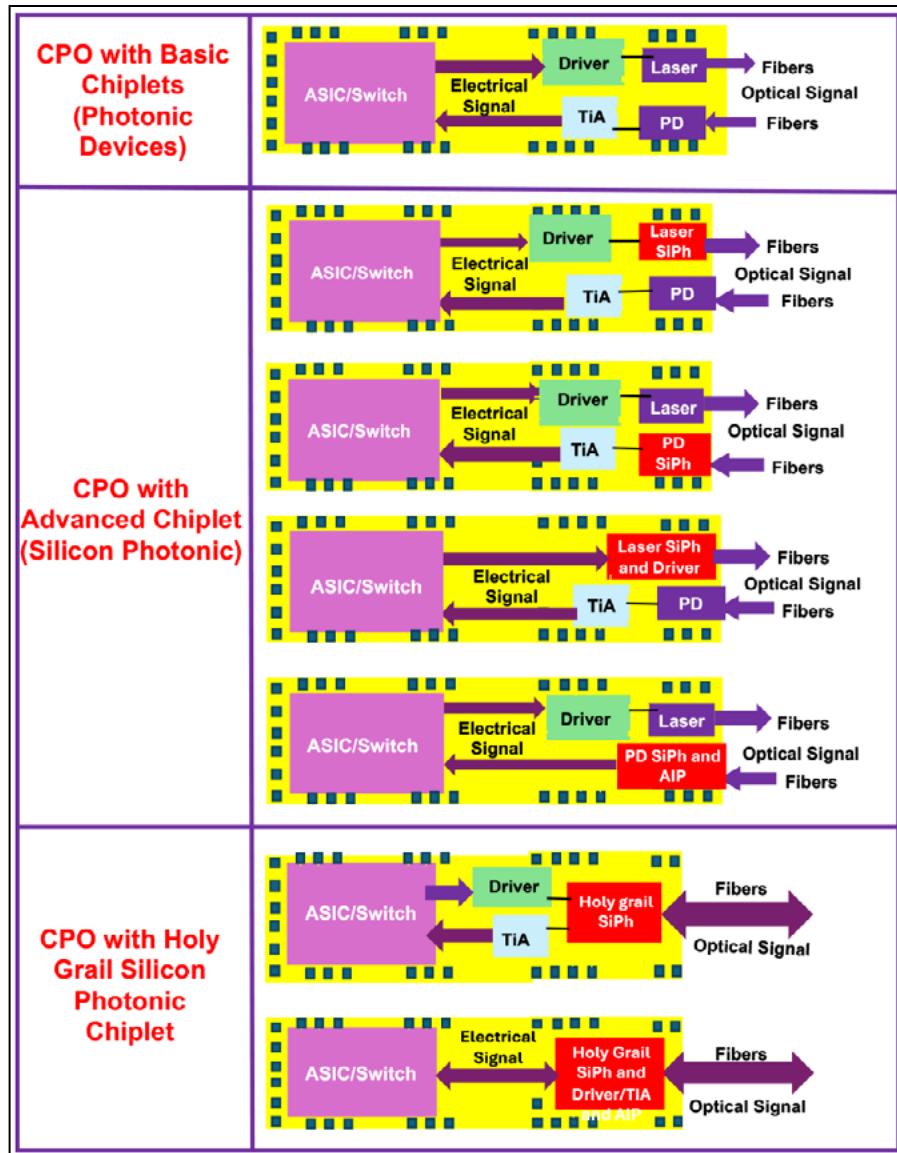

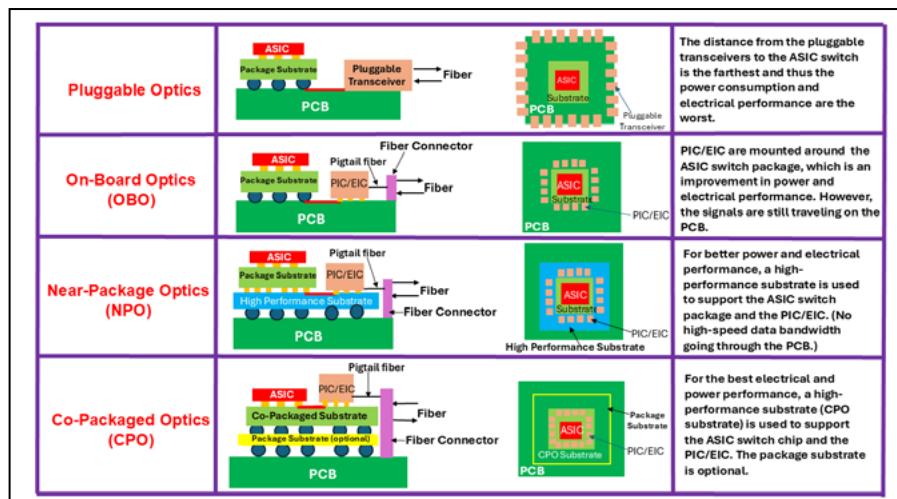

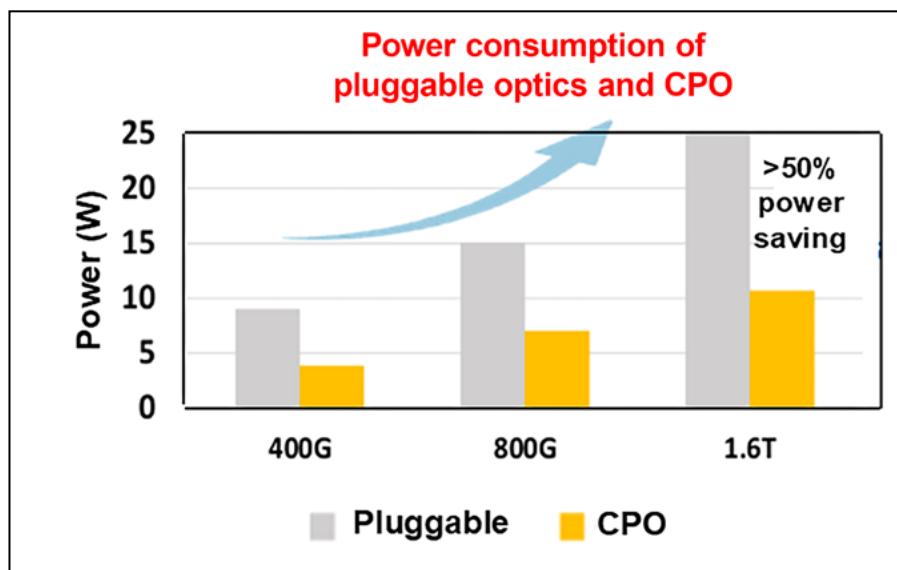

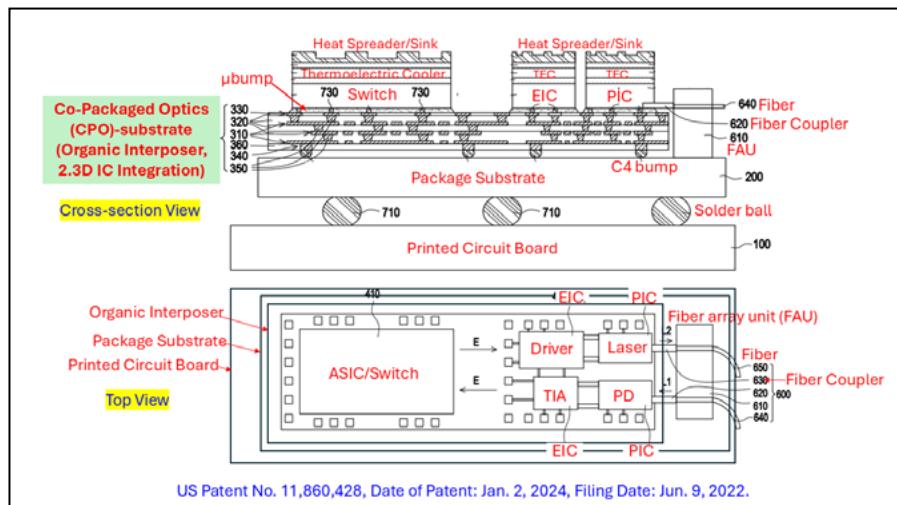

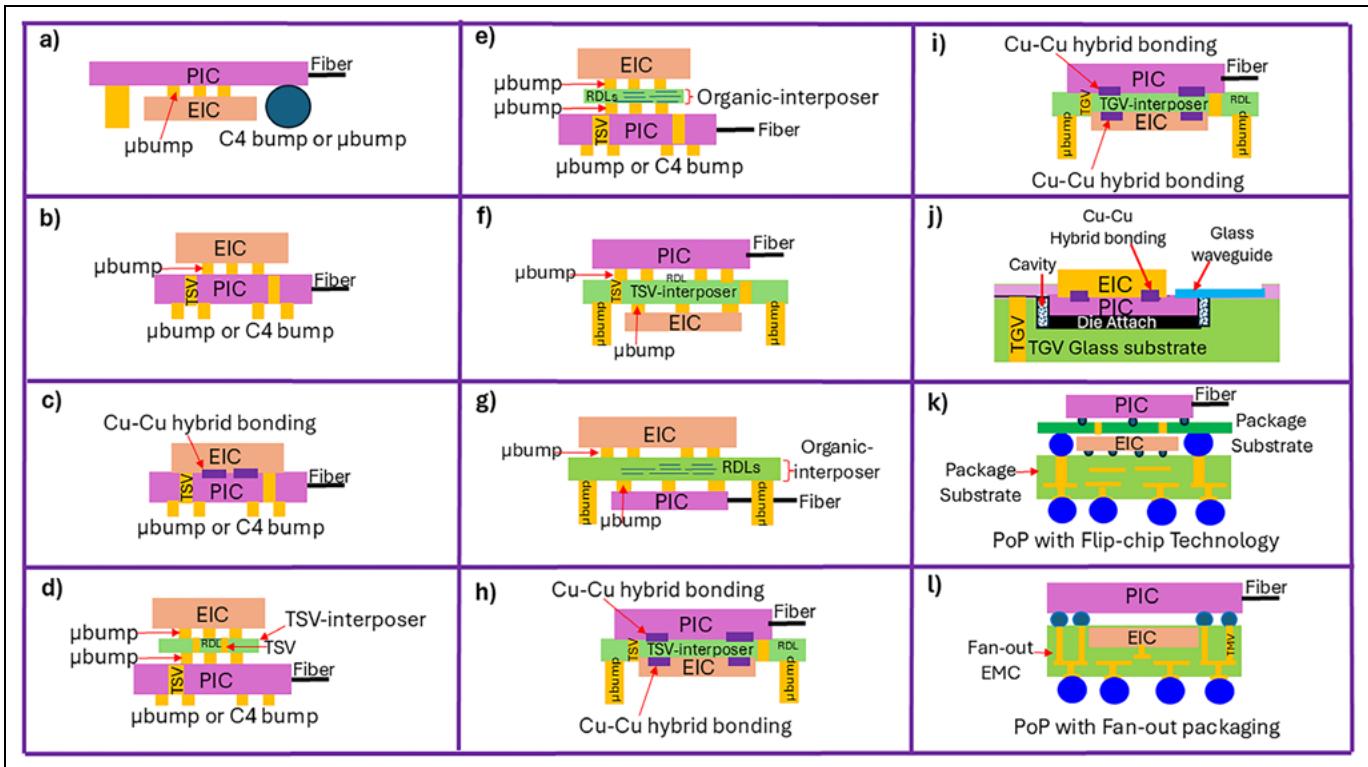

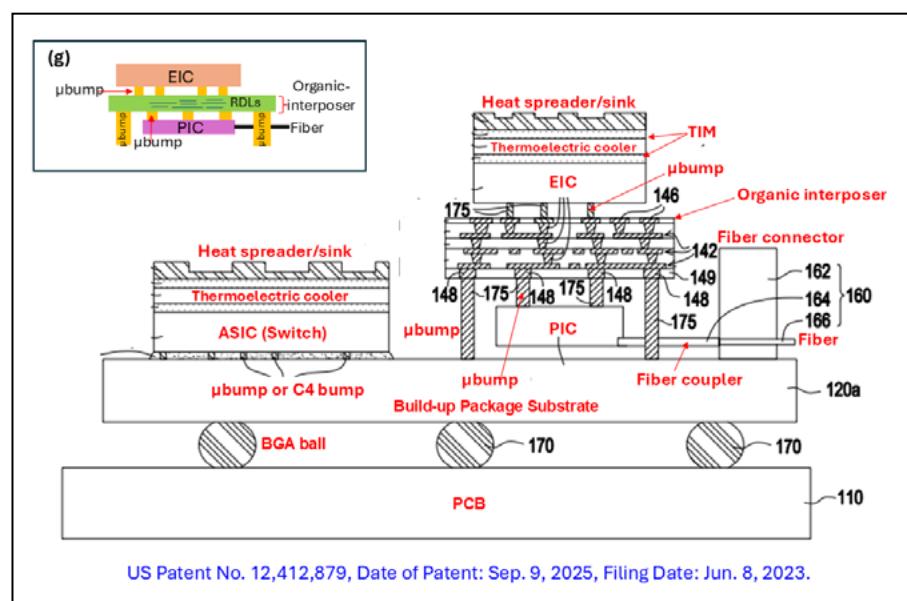

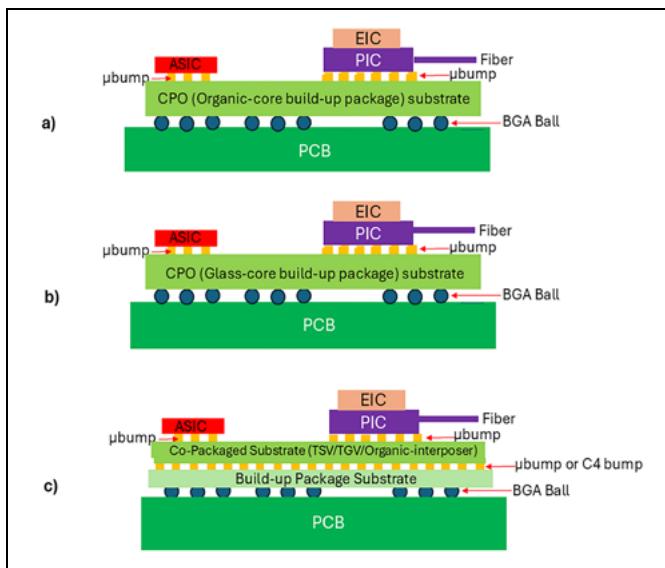

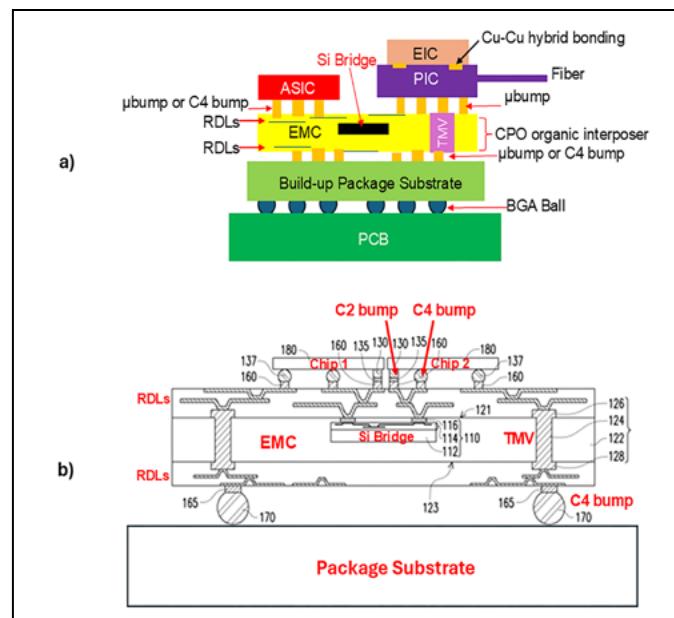

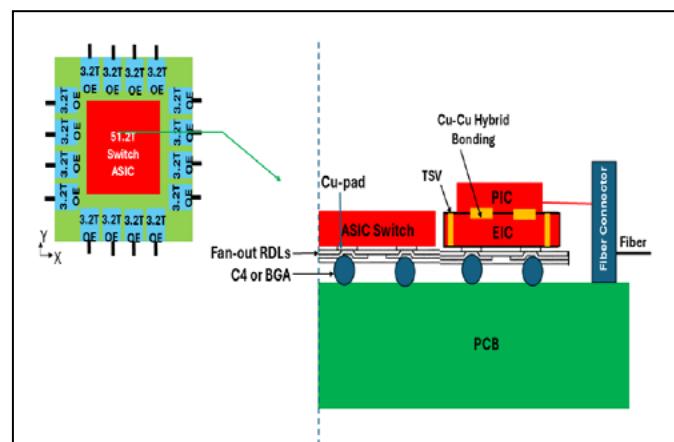

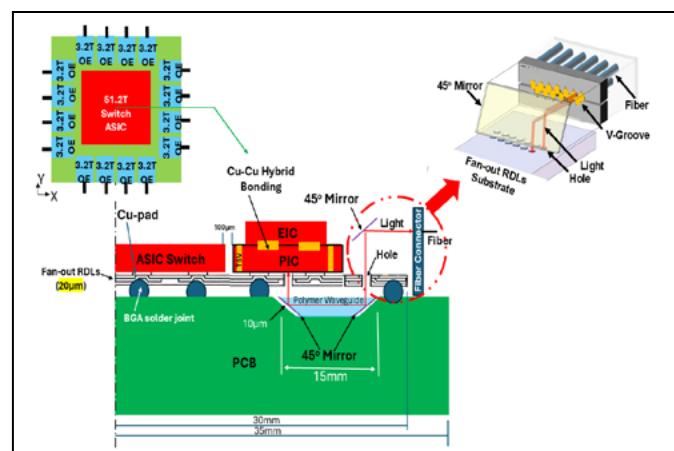

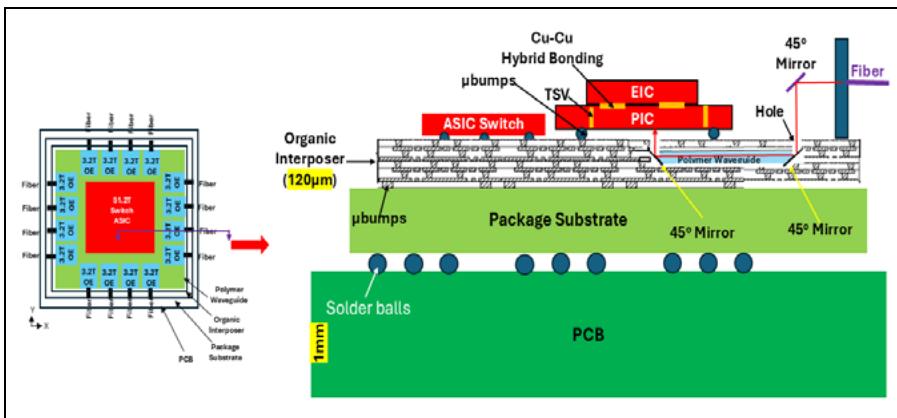

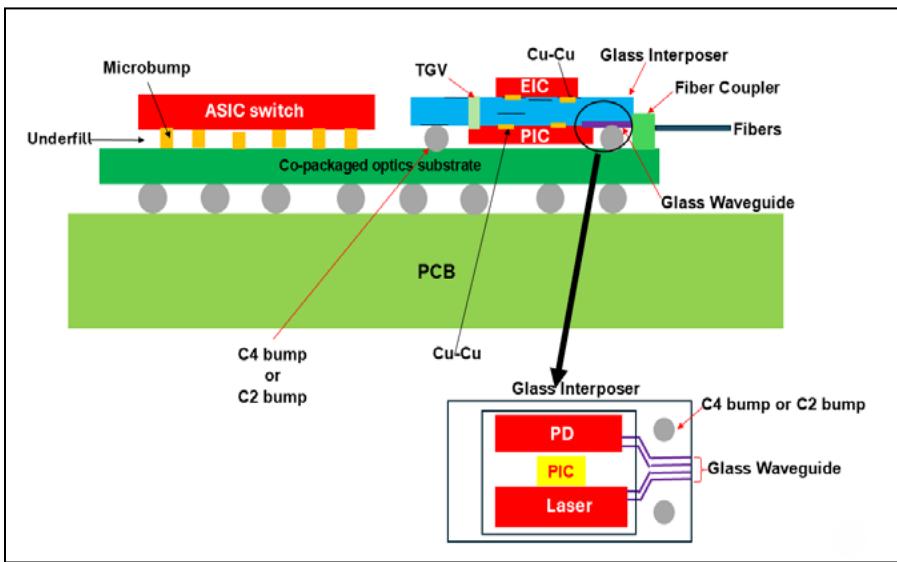

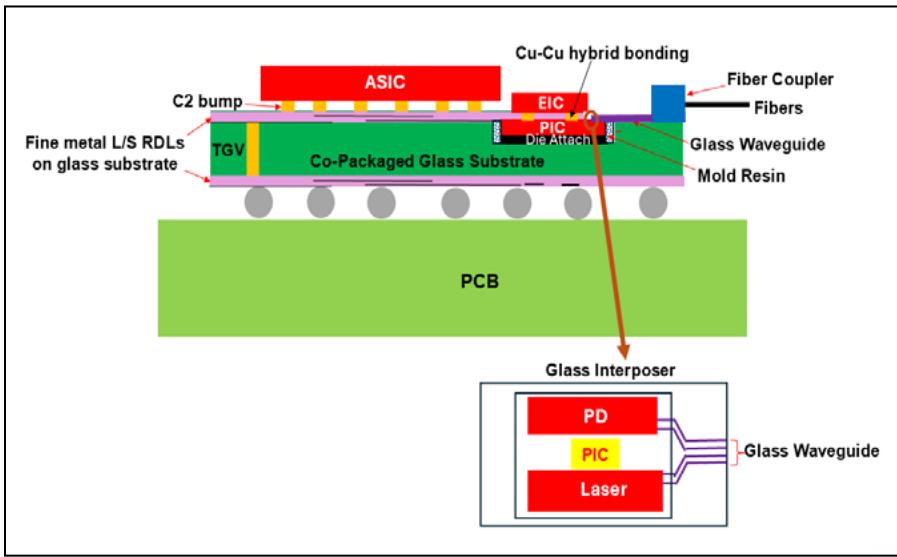

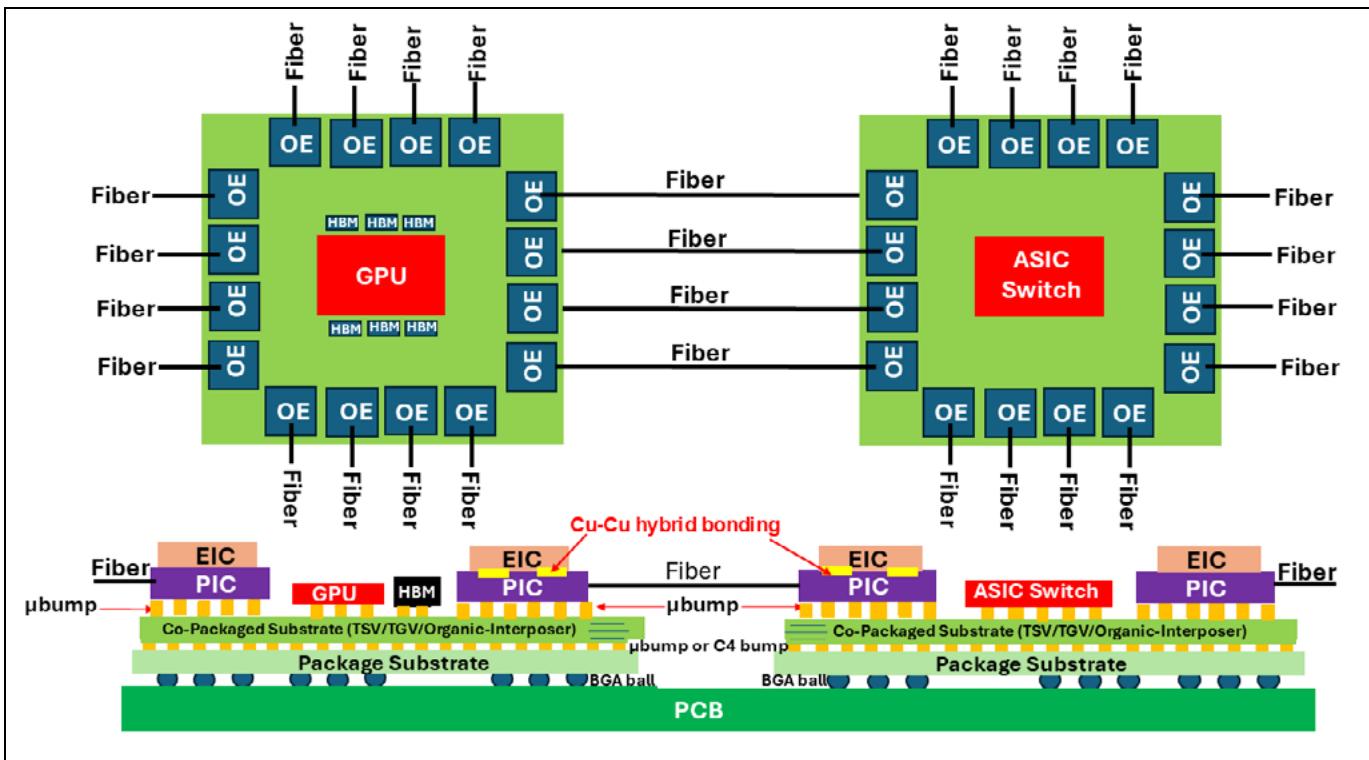

### 32 Co-packaged optics: Heterogeneous integration of chiplets in switches, PICs, and EICs

By John H. Lau *[Unimicron Technology Corporation]*

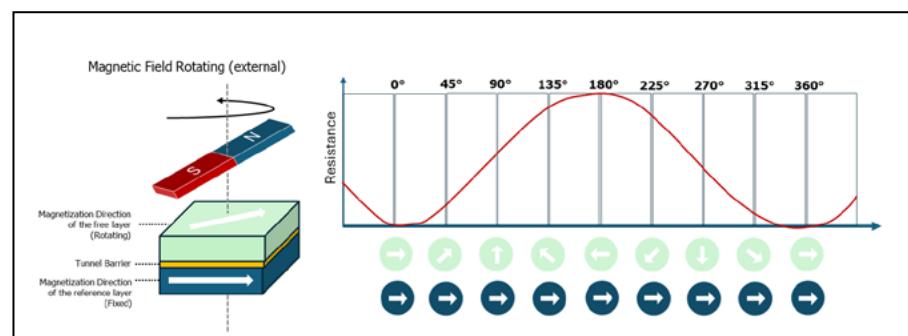

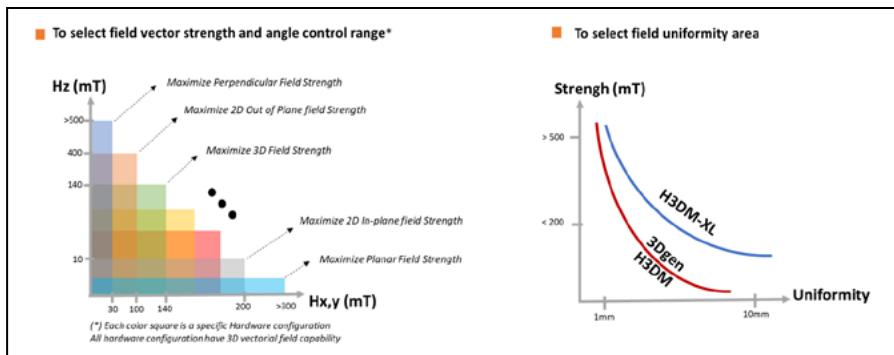

### 42 Wafer-level testing of TMR sensors using 3D magnetic field excitation

By Siamak Salimy *[Hprobe]*

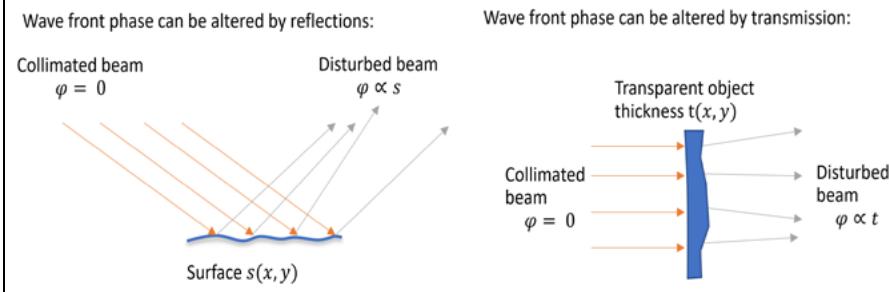

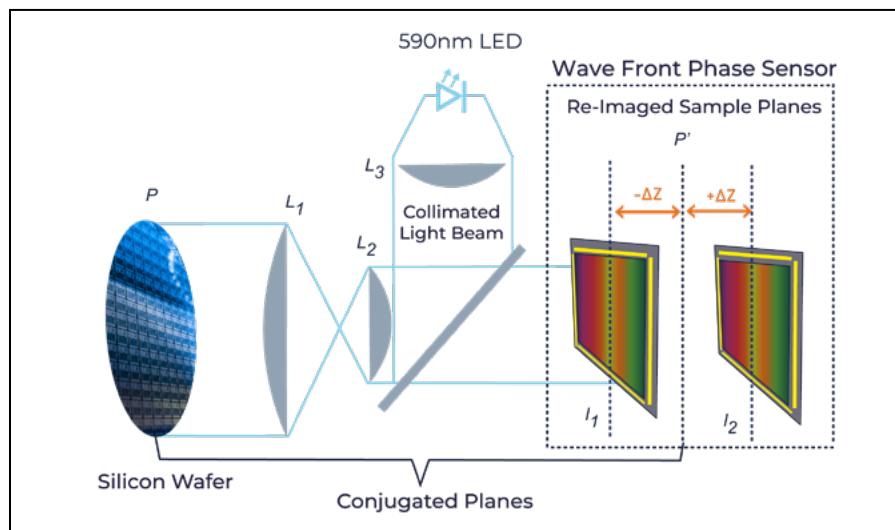

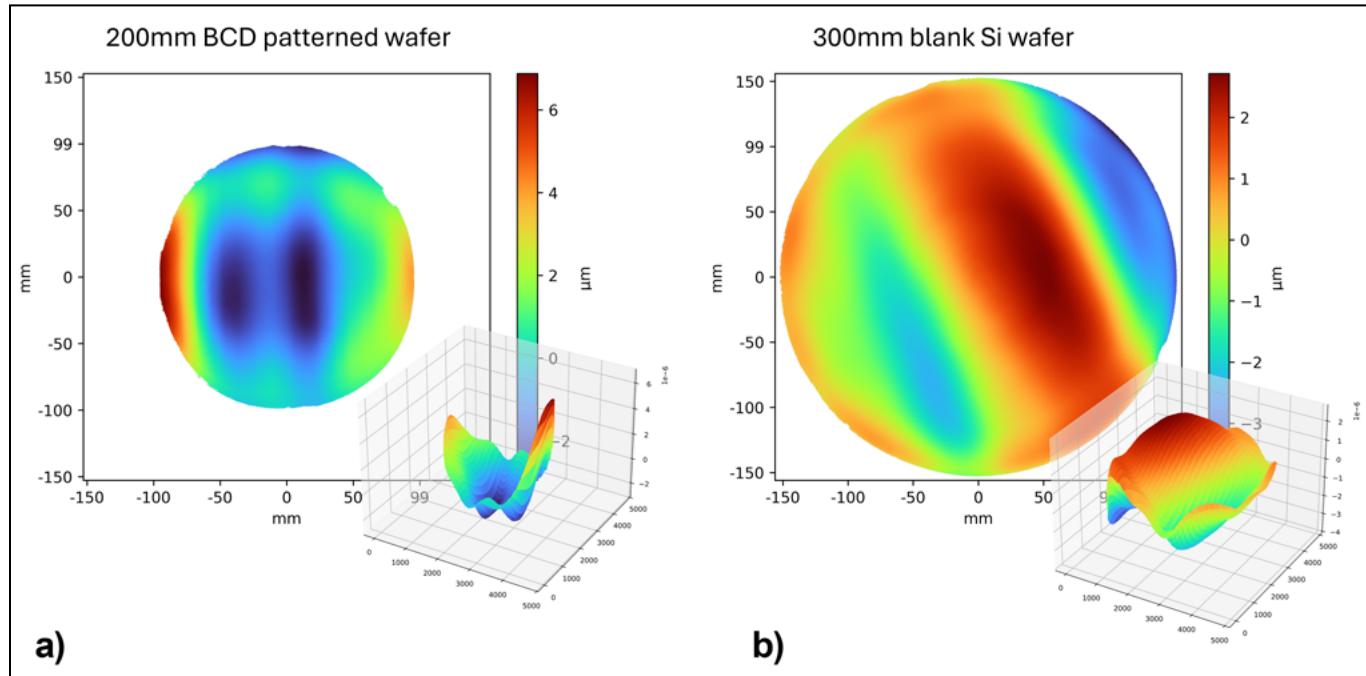

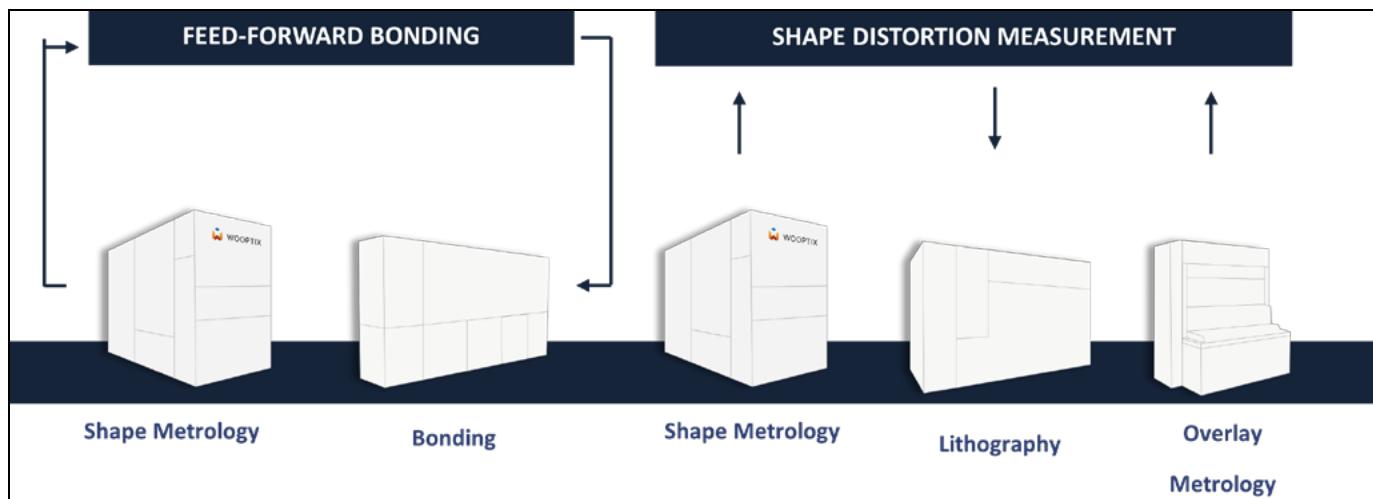

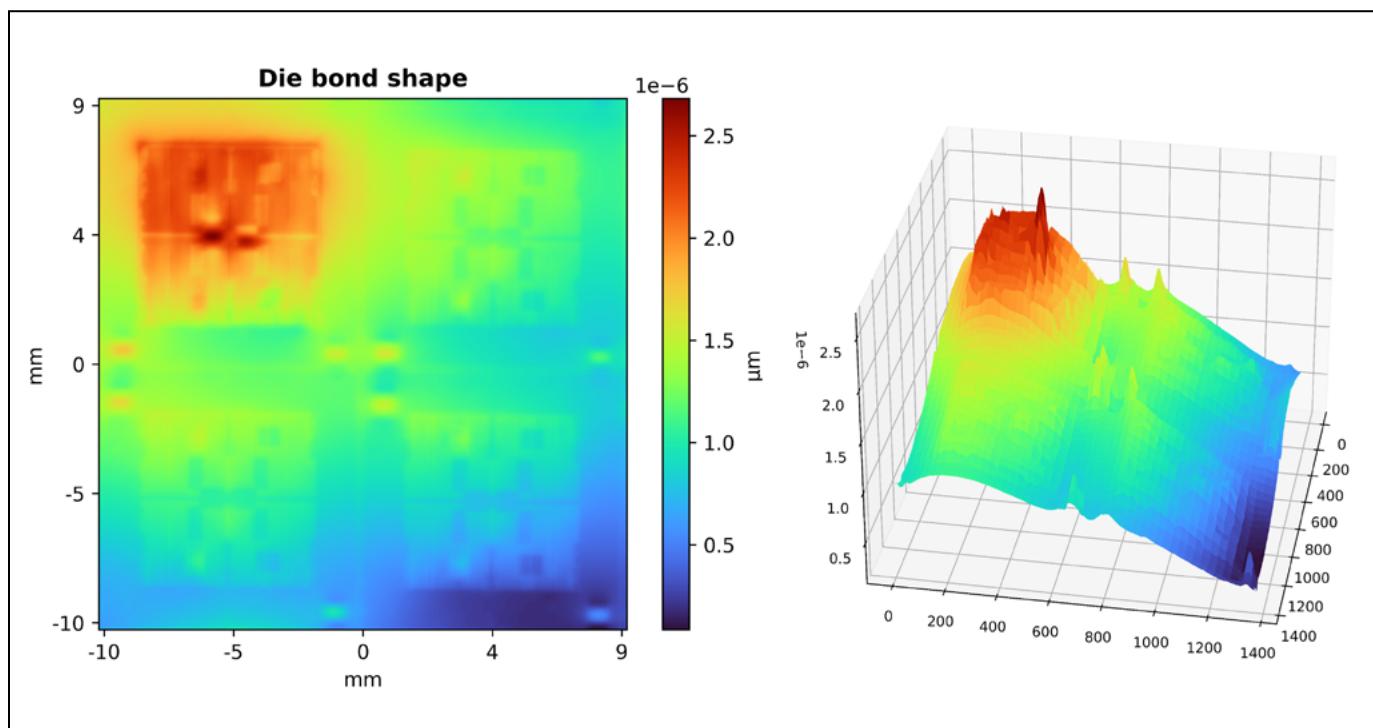

### 46 Impact of wave front phase imaging on semiconductor metrology challenges

By Miguel Jimenez-Gomis, Marco Franchi *[Wooptix]*

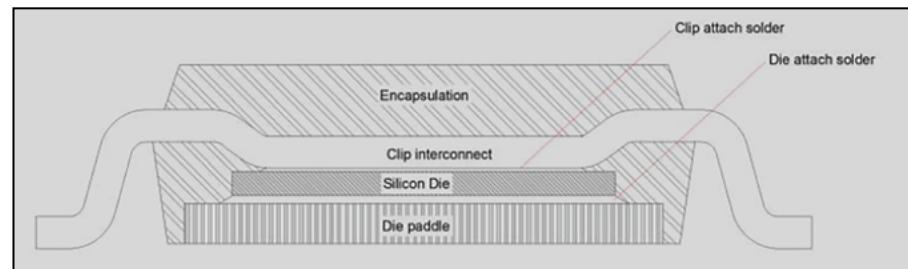

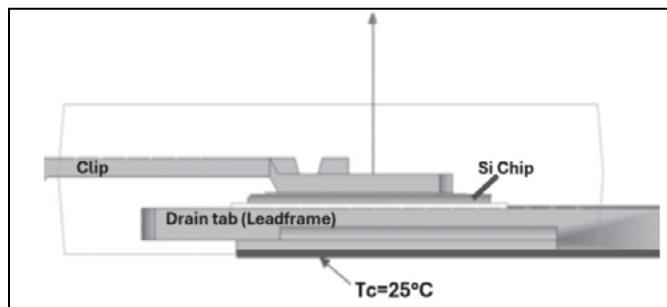

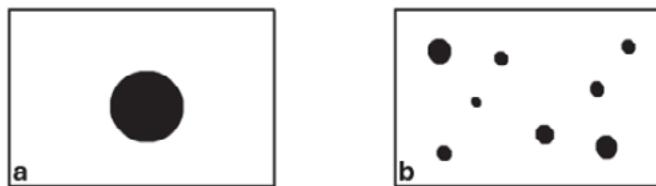

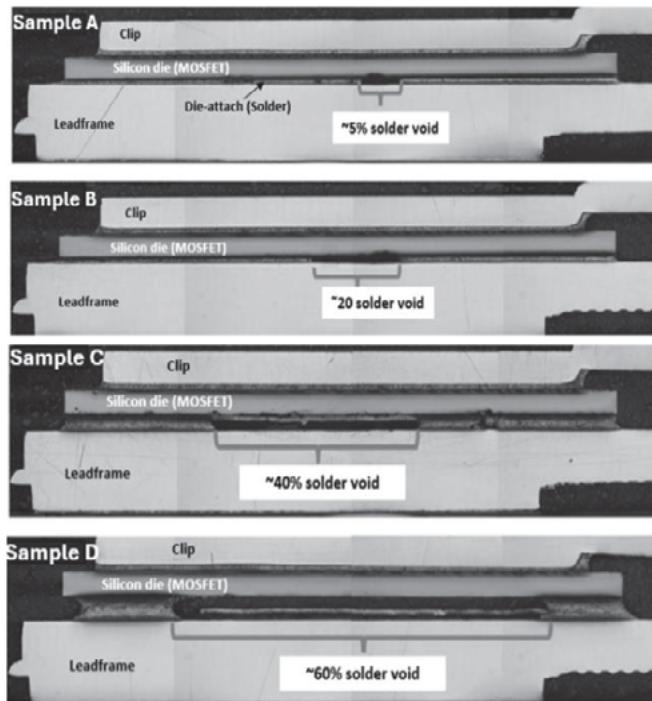

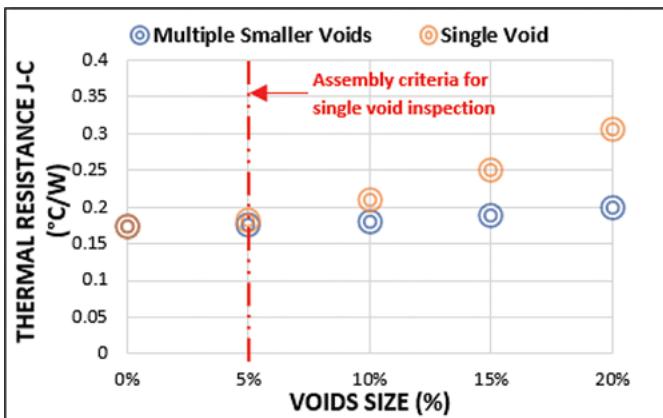

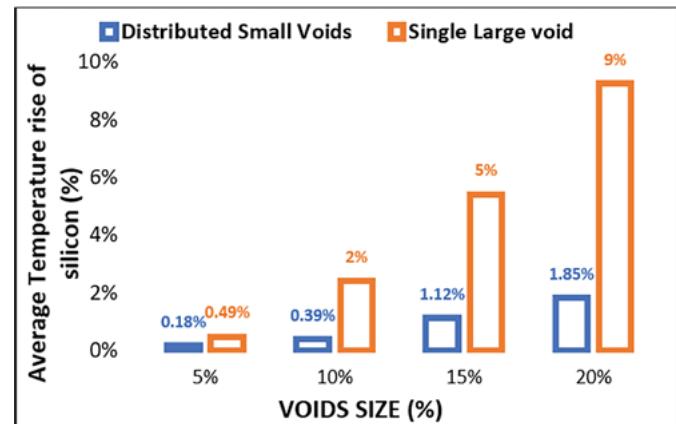

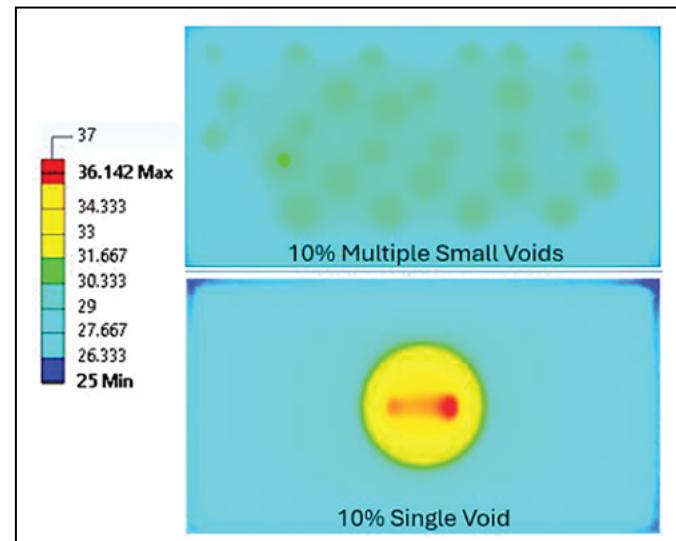

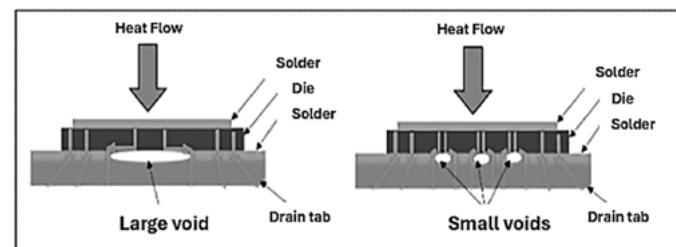

### 50 Impact of die-attach voids on the thermal performance of clip-bonded packages

By Ilyas Dchar, Ding Yandoc *[Nexperia]*

## DEPARTMENTS

### INDUSTRY EVENTS

### 56 Summary of the ECTC 2025 special session on hybrid bonding

By Mariia Gorchichko *[Applied Materials, Inc./IEEE]*

Dishit P. Parekh *[AMD/IEEE]*

Benson Chan *[Binghamton University/IEEE]*

Srinidhi Ramamoorthy *[Applied Materials, Inc./IEEE]*

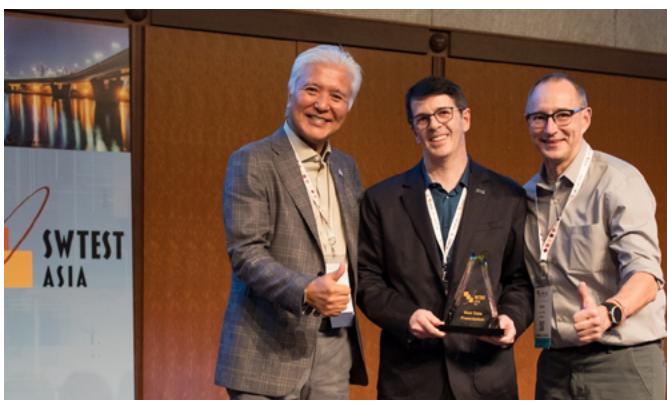

### 62 The 6th SWTest Asia Conference and EXPO was an overwhelming success!

By Jerry Broz *[General Chair, SWTest US and SWTest Asia Conferences, and Delphon Industries]*

**From electrons to photons,

ASE is innovating for

performance advantage

and energy efficiency.**

**ASE is enabling the heterogeneous integration

and chiplets era through VIPack™

while delivering sustainable

advanced packaging innovations for:**

**AI • HPC • DATA CENTER • ROBOTICS

AUTOMOTIVE • IoT • 6G • AEROSPACE • And more.**

X [@aseglobal" data-bbox="43 521 180 538">@aseglobal](https://twitter.com/aseglobal)    In [@aseglobal" data-bbox="205 521 340 538">@aseglobal](https://www.linkedin.com/company/ase-global)    [@aseglobal.com](https://www.aseglobal.com)

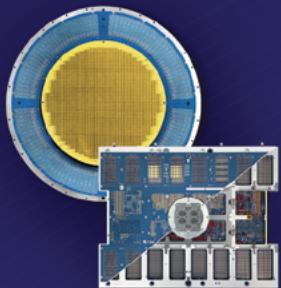

# Heterogeneous wafer-scale integration: The new front line of semiconductor scaling

By Krutikesh Sahoo, Subramanian S. Iyer [*Samueli School of Engineering, University of California, Los Angeles*]

**F**or over five decades, the semiconductor industry lived by a simple, powerful rule: Moore's Law [1]. By shrinking the transistor, we gained speed, reduced power, and lowered costs. An equally important, but somewhat lesser known law that relates to the economics of Moore's Law, is Rock's Law [1]. However, as we navigate the sub-5nm era, the economic and physical foundations of monolithic scaling are fracturing. The reticle limit—the maximum size of a single chip—has become a wall that artificial intelligence (AI) and high-performance computing (HPC) workloads are crashing into. AI machines emphasize bandwidth while conventional HPC focuses on latency. But both are important at the system level.

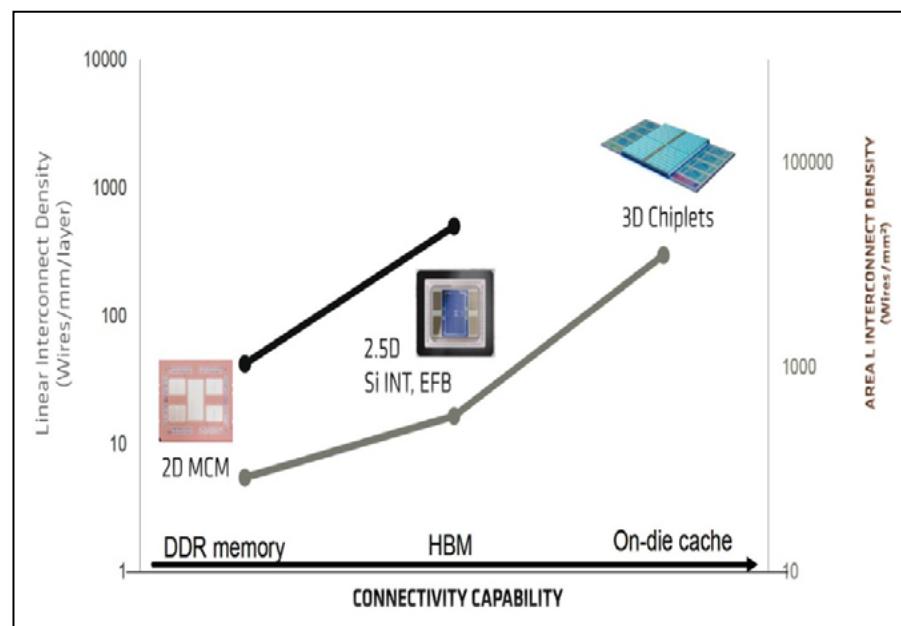

To bridge the gap between the exponential demand for compute and the physical limits of silicon, the industry is pivoting. The focus has shifted from the transistor to the package [2]. We are entering the era of heterogeneous integration (HI), where the system is no longer a single piece of silicon, but a collection of optimized “dielets” or chiplets. It should be pointed out that there is some confusion between the terms chip and die. A circuit designer designs a chip—it is an abstraction of the design. The foundry converts that abstraction via masks and processes into hard wafers. The wafers are tested and diced into dies. Known good dies are then packaged and retransformed into chips. Chiplets and dielets have the same connotation, but chiplets and dielets are not merely small chips or dies. They are nonfunctional by themselves and need to be connected to other chiplets and dielets to exhibit functionality. To reiterate, chiplets are designed, dielets are assembled onto advanced packages—but this time, the assembly of packaged dielets is called a module or sub-assembly.

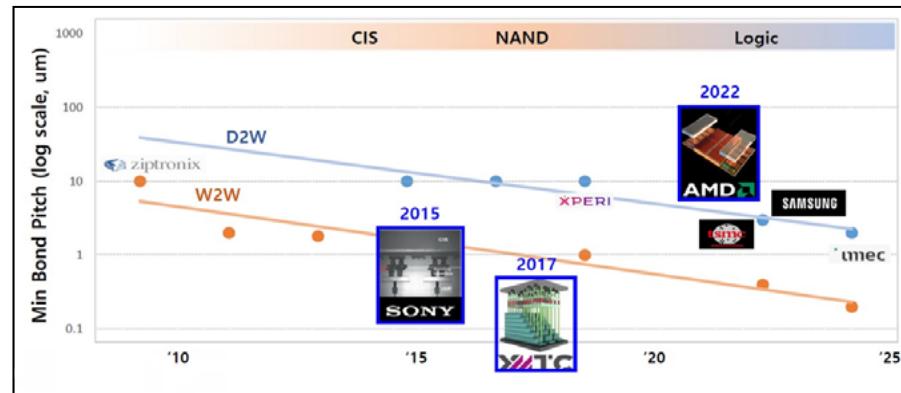

The transition to heterogeneous wafer-scale integration requires a fundamental rethinking of how we connect chips. In this article, we review the landscape of modern interconnect technologies—from traditional solder to cutting-edge hybrid bonding—and present a deep dive into a high-throughput copper-to-copper (Cu-Cu) thermal compression bonding (TCB) scheme that enables true wafer-scale integration.

## The architectural pivot: Scale down vs. scale out

To understand the current state of advanced packaging, one must understand two primary scaling philosophies: scale down and scale out.

**Scale down: The pursuit of density.** Scale down is the packaging equivalent of traditional Moore's Law. The goal is to shrink every dimension: finer bump pitches, thinner dielectrics, and narrower metal lines. This approach is epitomized by direct metal-to-metal bonding such as thermal compression bonding (TCB), which targets pitches well below 10 $\mu$ m, eventually aiming for sub-micron levels [3]. Scale down is essential for 3D-IC stacks where vertical bandwidth between stacked dielets is being addressed.

**Scale out: The pursuit of reach.** Scale out, by contrast, is about area. It involves expanding the footprint of the scaled-down entity to the scale of a system or sub-system—potentially an entire 300mm wafer, or even a 600mm panel to accommodate massive amounts of memory and thousands of processing cores—all intimately connected at almost monolithic levels. This mimics the functionality of a giant monolithic chip but uses smaller, high-yield heterogeneous dielets (meaning dielets from different technologies, material systems and nodes). The challenge here isn't just pitch—it is the mechanical stability, warpage control, and the throughput and system functionality required to assemble thousands of dielets on a single substrate.

## Navigating the interconnect landscape

The industry currently relies on four primary methods to join dies or dielets to substrates or wafers. Each comes with a specific “sweet spot” in terms of pitch and manufacturing complexity.

**Solder-based flip chip.** Mass reflow of solder bumps has been the workhorse of the industry for 30 years. However, as pitches shrink below 40 $\mu$ m, solder encounters physical limits. The risk of solder bridging (shorts) increases, and the intermetallic compounds (IMCs) that form the bond become brittle, thereby compromising performance and reliability. Furthermore, the volume of solder required at fine pitches is so small that it becomes difficult to control the joint's consistency.

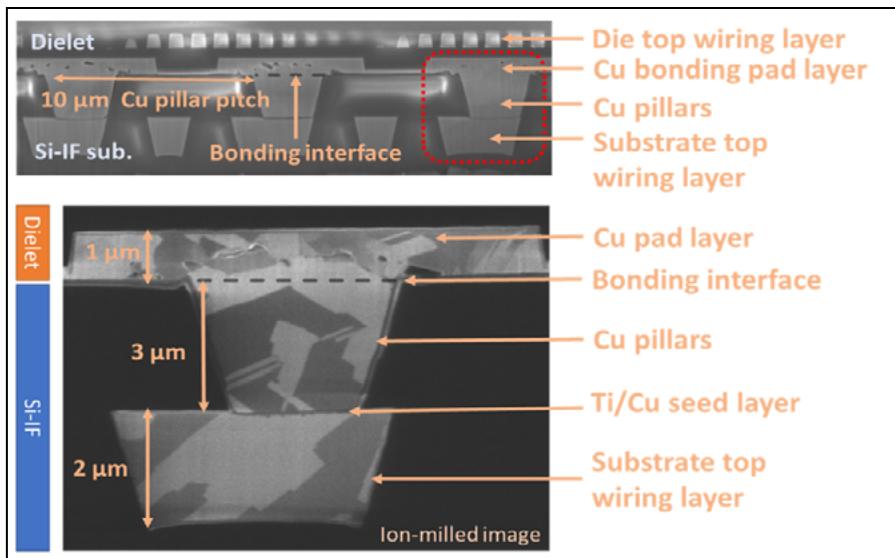

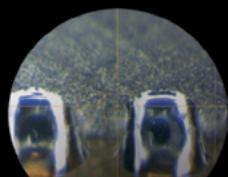

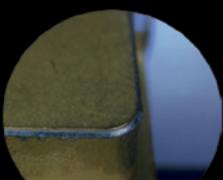

**Thermal compression bonding (TCB).** TCB was developed to extend solder life. By applying heat and pressure simultaneously via a bond-head, TCB allows for finer control than just thermally-assisted mass reflow. While often used with solder-tipped microbumps, the industry is increasingly looking at solderless Cu-Cu TCB. By bonding copper pillars directly to copper pads, we eliminate the risks of solder bridging and IMC formation. Furthermore, copper-copper interdiffusion results in a robust metallurgical bond—basically acting like a continuous piece of metal so long as any surface films can be removed by pretreatment. **Figure 1** shows such a solder-less Cu-Cu contact.

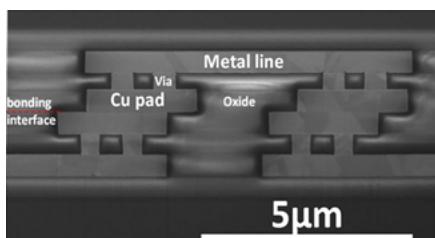

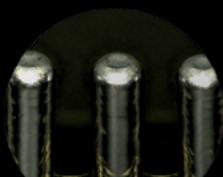

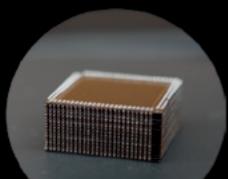

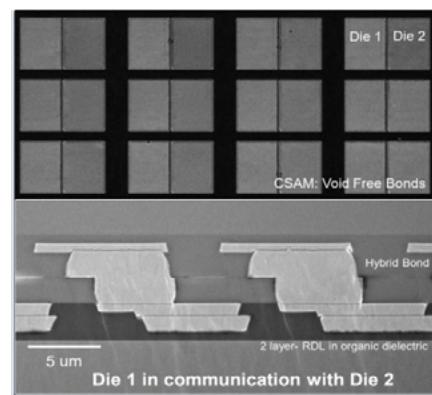

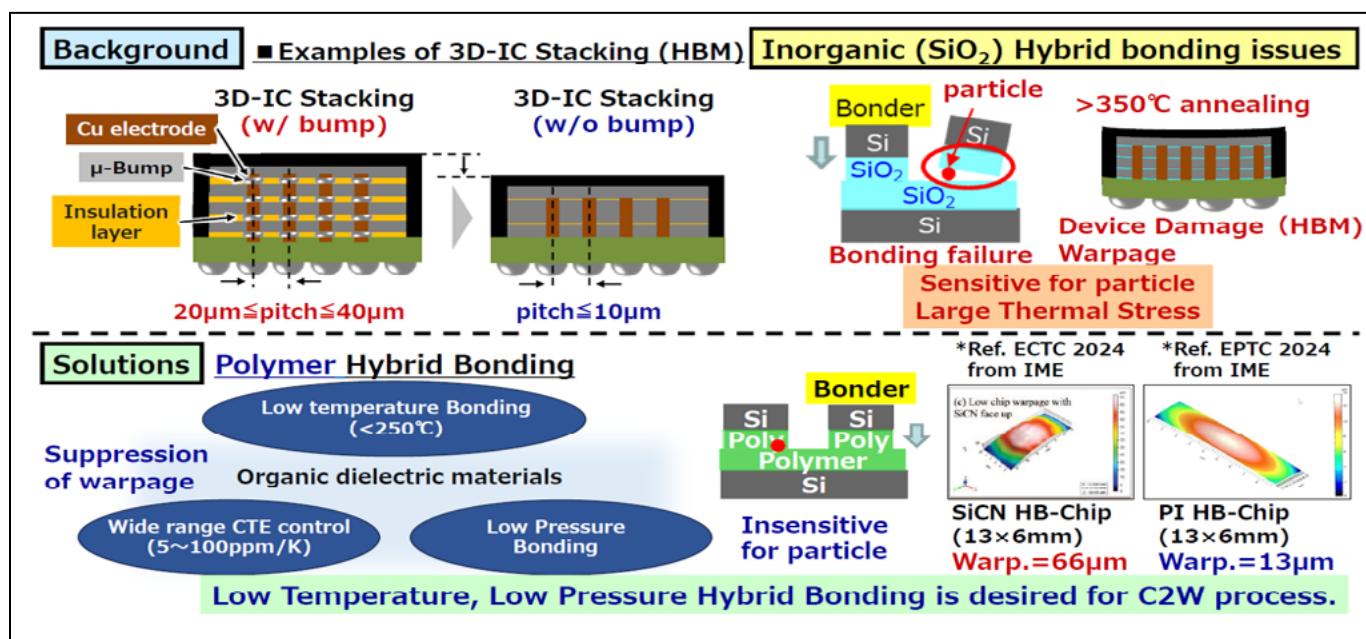

**Hybrid bonding (HB).** Hybrid bonding represents another approach to “scale down.” It involves a perfectly flat surface where both the copper interconnects and the surrounding dielectric (usually SiO<sub>2</sub> or SiCN) are bonded together (**Figure 2**). The dielectric is bonded first and a thermal cycle is used to expand the recessed copper to connect. While HB has the potential to offer the highest interconnect density, its requirements

**Figure 1:** Cross section of solderless Cu-Cu thermal compression bonding interconnects from [5]. The micrograph shows grain growth across the bonding interface.

are extreme: Class 1 cleanroom environments, sub-nanometer surface roughness, and expensive chemical mechanical polishing (CMP) steps. The nature and strength of the dielectric bond is just as important as the Cu-Cu bond. This puts restrictions on the nature of the dielectric and processes need to be optimized for a specific dielectric. This makes the realization of heterogeneous hybrid bonding more difficult, especially if multiple foundries and material sets are involved. Hybrid bonding does have an advantage in alignment and overlay tolerance as the initial dielectric bond is performed at room temperature.

**Fan-out wafer-level packaging (FOWLP).** FOWLP is another approach that uses molding compounds. It has the potential to reach fine pitch as well as panel scale. In this method, dies are embedded in an epoxy matrix and connected—typically lithographically—to wiring layers. We mention this for completeness and will discuss it in a forthcoming article.

### The wafer-scale vision: Silicon interconnect fabric (Si-IF)

To achieve true scale out, the substrate itself must evolve. Traditional organic substrates (like FR4 or build-up films) suffer from high coefficients of thermal expansion (CTE) mismatch with silicon, leading to significant warpage.

At UCLA CHIPS, we have pioneered the silicon interconnect fabric (Si-IF) [4]. The Si-IF is an active or passive silicon wafer used as a high-density wiring platform. Because the substrate is silicon and the dielets are also silicon, the CTE is perfectly matched. This eliminates warpage issues during thermal cycling and allows for incredibly tight integration. On the Si-IF, we can achieve interconnect pitches of 7 μm and below across an entire wafer [5].

### Engineering the perfect bond: The physics of Cu-Cu TCB

The heart of our recent research involves optimizing the Cu-Cu TCB process to make it viable for high-volume manufacturing. Direct Cu-Cu bonding relies on solid-state diffusion. When two copper surfaces are pressed together under heat, atoms migrate across the interface, eliminating the boundary and forming a continuous metallic grain. (This happens in hybrid bonding as well, but the force is internally generated by thermal expansion of the copper.) The pressure in TCB is externally impressed and independent of the material system, and therefore, more controllable and process tolerant.

**The challenge of oxidation.** The big enemy of Cu-Cu bonding is oxide. Copper oxidizes almost instantly in air, forming a stable Cu<sub>2</sub>O film layer, the thickness of which can increase and eventually saturate with increasing temperature. This oxide acts as a barrier to diffusion. To achieve a successful bond, this oxide must be removed or bypassed. Historically, this required bonding in a vacuum or using reducing gases like formic acid, both of which slow down the manufacturing process.

**Surface preparation and roughness.** Before bonding, we employ a pre-bond treatment. This typically involves an ion beam or plasma clean to remove the native oxide and activate the surface. We have found that the root mean square (RMS) roughness of the copper pillars must be kept below 3 nm to ensure sufficient contact area for diffusion to occur at reasonable temperatures (300°C–400°C). During bonding, an in situ reducing atmosphere of formic acid is provided locally within the bonding tool to remove oxide residues and prevent oxidation at higher bonding temperatures. This step can be removed so long as a low-oxygen environment can be created within the bonding tool, such as by continuous purging with nitrogen.

### Solving the throughput problem: The two-step process

In a trade environment, “cool technology” is useless if it is not “profitable technology.” Traditional TCB Cu-Cu is notoriously slow [6]. A single-step TCB cycle—including die transfer, alignment, and the time the bond head holds the die in place while heating it to 300°C and cooling it back down—takes roughly 30 to 60 seconds. If a wafer-scale system requires 1,000 dielets, a single-step process would take over 16 hours to populate one wafer. This is commercially nonviable.

### The breakthrough: Tacking and batch annealing

To solve the issues discussed above, we developed a two-step TCB process [5] that decouples the alignment from the permanent bonding. The two-step process is discussed below.

**Step 1: High-speed tacking.** A high-precision flip-chip bonder picks the dielet, aligns it to the Si-IF, and applies a low-temperature (120°C), low-force pulse. This “tacks” the dielet in place. The tacking force is sufficient to overcome initial surface roughness and keep the

**Figure 2:** Cross section of a hybrid bonded interface based on [6].

## M-Series™ with Adaptive Patterning® a world of possibilities

### MDQFN®

Free of leadframe limitations

Standard & custom footprints

10X scale with 600mm panels

### MDx™

Eliminates capture pads on all layers

Ultra-high-density interconnects

Unlimited scaling potential

### MCSP™

Fan-in and Fan-out

Adaptive Alignment™

Fully encapsulated with superior reliability

### MFIT™

Molded fan-out interposer technology

Chips last processor & memory

Embedded bridge die & 3D interconnects

### M2CM™

Multi-die or chiplet integration

Adaptive Routing™

Passive integration

### MPoP™

Dual-sided RDL interconnect

Copper post vias (CPV) through body

Ideal for memory integration on processor

[www.thinkdeca.com](http://www.thinkdeca.com)

dielet from moving during transport. This step takes less than 10 seconds.

**Step 2: Batch annealing.** Once the entire 300mm wafer is populated with tacked dielets, the whole assembly is placed in a furnace. The entire wafer is annealed at 300°C–400°C for 30 to 60 minutes. Because thousands of bonds are being finalized simultaneously in the furnace, the effective throughput jumps to over 1,100 dielets per hour (DPH). This brings Cu-Cu TCB into the realm of high-volume manufacturing.

## Manufacturing yield and self alignment

In wafer-scale systems, yield is everything. If you have 1,000 dielets and one fails due to a bonding defect, the entire wafer-scale system may be compromised. Discussion of some of these issues follows below.

**The tooling factor.** Our research utilized a KNS APAMA [7] flip-chip bonder. We identified that the planarity of the bond head is the most critical tool parameter. If the head is tilted by even a fraction of a degree, the pressure across the dielet becomes nonuniform, leading to cold joints on one side and deformed pillars on the other. Clean particle-free die edges (determined by dicing strategy) are also critical to ensure reliable contact, especially in metal-metal TCB and HB where the gap between die pads and substrate pads/pillars is usually small or nonexistent. Newer models such as the KNS Aptura allow for much greater control, alignment capability, and throughput with Cu-Cu TCB as the go-to process for heterogeneous 3D integration.

**Solder-assisted TCB?** While our primary focus is solderless, we also evaluated a hybrid approach using a thin (2 $\mu$ m) cap of tin (Sn) on the copper pillars. This solder-capped TCB is much more forgiving of surface roughness and planarity issues because the liquid solder fills the gaps. However, for the highest performance and the tightest pitches, the industry consensus is moving toward the “pure” Cu-Cu approach to avoid the Kirkendall voiding associated with solder. Eliminating solder enables a simpler foundry-friendly process.

## Reliability: Passing the JEDEC gauntlet

For the Si-IF and Cu-Cu TCB to be adopted by industry leaders, they must survive extreme environmental stress. We subjected our wafer-scale assemblies to a series of rigorous tests described below.

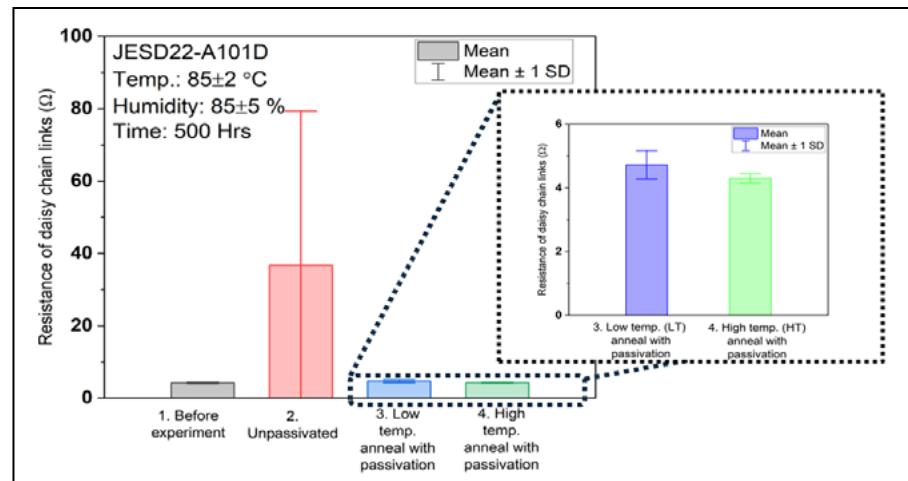

**Figure 3:** Steady-state humidity tests (JESD22-A101D) for passivated and unpassivated samples, showing passivated samples have <10% resistance change. LT and HT refer to Cu-Cu annealing done at 300°C and 400°C, respectively. This shows the effectiveness of alumina in passivating Cu-Cu interconnections after bonding. SOURCE: [9] (available online after 2/12/26)

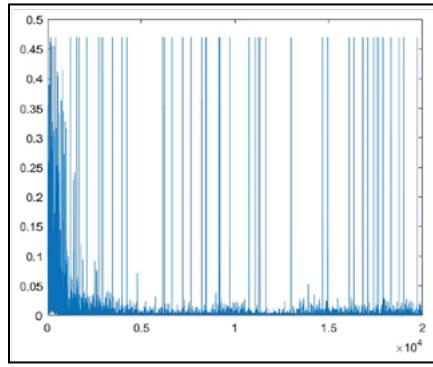

**Humidity and passivation.** Copper is prone to corrosion. To protect the wafer-scale system, we implemented atomic layer deposition (ALD) of alumina [8]. By coating the entire assembly in a nanometer-thin layer of alumina ( $\text{Al}_2\text{O}_3$ ), we created a moisture barrier that effectively “hermetically seals” the interconnects. **Figure 3** shows results of resistance change of daisy chains bonded using Cu-Cu TCB, where one set of samples was passivated with alumina after TCB, and another set of samples was not passivated after TCB [9]. Results of our evaluation are as follows: 1) Without passivation: Samples failed the 85°C/85% relative

humidity test within 100 hours; and 2) With ALD passivation: Samples maintained their electrical resistance and mechanical integrity for over 500 hours.

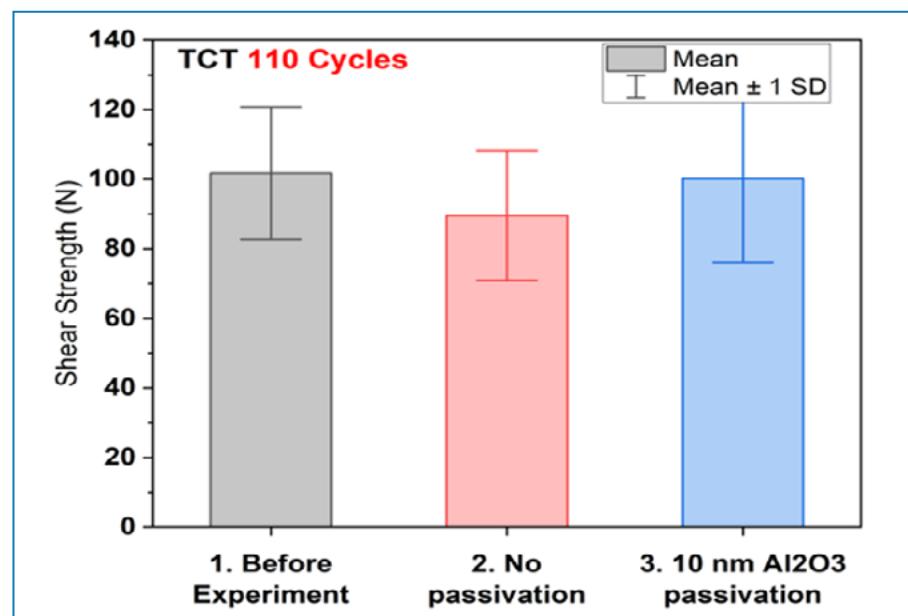

**Thermal cycling (TC).** We cycled the assemblies from 0°C to 125°C. Thanks to the CTE-matched nature of the Si die and Si substrate, we saw zero bond failures after 110 cycles. The shear strength of the bonds actually increased slightly after cycling because the additional heat prompted further grain growth. **Figure 4** shows results of shear strength after temperature cycling of samples, with and without passivation.

**Figure 4:** Temperature cycling test (TCT) for 110 cycles showing no change in shear strength in case of  $\text{Al}_2\text{O}_3$  passivated samples. SOURCE: [9] (available online after 2/12/26)

## The road ahead: 2025 and beyond [11]

The transition to heterogeneous wafer-scale integration is no longer a research project—it is a manufacturing necessity. As we look toward the next five years, several trends will dominate the chip-scale landscape in three main areas discussed below.

**Standardization of chiplet interfaces.** For the scale-out model to work, dielets from different vendors must be able to “talk” to each other. Simple, protocol-independent communication methods such as the simple universal parallel interface for chips (SuperCHIPS), or bunch of wires (BoW), will be critical.

**The rise of direct Cu-Cu bonding.** Thermal compression bonding—the mainstay of today’s advanced packaging assembly methods—will continue to make progress and potentially extend to the 5 $\mu$ m-pitch regime. Hybrid bonding is also a contender, especially when all the dielets are from the same foundry.

**Thermal management.** Packing thousands of dielets on a single wafer generates immense heat. We are seeing a move toward integrated liquid and two-phase cooling and micro-channel heat sinks intimately bonded to the assembly, preferably without the use of thermal interface material.

## Summary

Heterogeneous integration on the silicon interconnect fabric represents the most viable path to maintaining the trajectory of system-level scaling. By utilizing a high-throughput, two-step Cu-Cu TCB process, we have demonstrated that wafer-scale systems can be potentially manufactured with the speed and reliability the industry demands.

The scale-out revolution is here. It is no longer about how many transistors we

can fit on a chip, but how many chips we can weave into a single, seamless, wafer-scale fabric. A deep dive into bonding mechanisms and influencing parameters for solder-based flip-chip, metal-metal TCB and hybrid bonding have been published in our previous work in IEEE Electron Device Reviews [10]. The reader is highly encouraged to read the document for deeper insight into how these bonding schemes fit with the interconnect roadmap.

## References

1. P. E. Ross, “5 Commandments [technology laws and rules of thumb],” IEEE Spectrum, vol. 40, no. 12, pp. 30-35, Dec. 2003, doi: 10.1109/MSPEC.2003.1249976.

2. S. S. Iyer, “Heterogeneous integration for performance and scaling,” IEEE Trans. on Components, Packaging and Manufacturing Tech. 6, no. 7 (2016): 973-982.

3. S. Jangam, S. S. Iyer, “Silicon-interconnect fabric for fine-pitch ( $\leq 10\mu$ m) heterogeneous integration,” IEEE Trans. on Components, Packaging and Manufacturing Tech. 11, no. 5 (2021): 727-738.

4. S. S. Iyer, S. Jangam, B. Vaisband, “Silicon interconnect fabric: A versatile heterogeneous integration platform for AI systems,” IBM Journal of Research and Development, vol. 63, no. 6, p. 5:1-5:16, Nov. 2019, doi: 10.1147/JRD.2019.2940427.

5. K. Sahoo, H. Ren, S. S. Iyer, “A high throughput two-stage die-to-wafer thermal compression bonding scheme for heterogeneous integration,” IEEE 73rd Electronic Components and Technology Conf. (ECTC), 2023, pp. 362–366. doi: 10.1109/ECTC51909.2023.000067.

6. E. Bourjot, et al., “10 $\mu$ m and 5 $\mu$ m die-to-wafer direct hybrid bonding,” IEEE 9th Electronics System-Integration Technology Conf. (ESTC), Sep. 2022, pp. 31–38. doi: 10.1109/ESTC55720.2022.9939476.

7. Kulicke and Soffa APAMA C2W bonder, online available: [https://www.kns.com/Products/Equipment/Advanced-Packaging-\(TCB\)/APAMA-C2W](https://www.kns.com/Products/Equipment/Advanced-Packaging-(TCB)/APAMA-C2W)

8. N. Shakoorzadeh Chase, K. Sahoo, Y. Tao Yang, S. S. Iyer, “Atomic layer deposited Al<sub>2</sub>O<sub>3</sub> encapsulation for the silicon interconnect fabric,” IEEE 70th ECTC, Jun. 2020, pp. 1241–1246. doi: 10.1109/ECTC32862.2020.00198.

9. K. Sahoo, “High throughput fine-pitch ( $\leq 10\mu$ m) assembly using Cu-Cu thermal compression bonding and protocol integration strategies for wafer-scale systems,” 2025, Accessed: Jan. 07, 2026. [Online]. Available: <https://escholarship.org/uc/item/13w5h0wq>

10. K. Sahoo, V. Harish, H. Ren, S. S. Iyer, “A review of die-to-die, die-to-substrate and die-to-wafer heterogeneous integration,” IEEE Electron Devices Reviews, vol. 2, pp. 6–31, 2025, doi: 10.1109/EDR.2024.3501214.

11. “Manufacturing Roadmap for Heterogeneous Integration and Electronics Packaging (MRHIEP),” available at <http://chips.ucla.edu/page/MRHIEP/MRHIEP%20Final%20Report>

## Biographies

Krutikesh Sahoo recently graduated with a PhD in Electrical Engineering from UCLA-CHIPS, focusing on advanced assembly and reliability. He is currently with Micron Technology, Inc.

Contact author: Subramanian S. Iyer (Subu) is Distinguished Professor and holds the Charles P. Reames Endowed Chair in the Electrical Engineering Department and a joint appointment in the Materials Science and Engineering Department at the University of California at Los Angeles. He is Director of the Center for Heterogeneous Integration and Performance Scaling (UCLA CHIPS). He is a fellow of IEEE, APS, iMAPS and NAI, as well as a Distinguished Lecturer of IEEE EDS and EPS. He is a Distinguished Alumnus of IIT Bombay. He received the IEEE Daniel Noble Medal for Emerging Technologies in 2012, and the 2020 iMAPS Daniel C. Hughes Jr. Memorial award, and the iMAPS Distinguished Educator Award in 2021. In 2023-2024, he was the Director of the NAPMP program. Email [s.s.iyer@ucla.edu](mailto:s.s.iyer@ucla.edu)

# Think Fast. See Small.

## SQ7000™+

### Multi-Function AOI, SPI & CMM

## SQ7000™ + All-in-One Solution

Next-gen multi-process inspector with paramount speed, accuracy and higher resolution for improved yields and processes.

Powered by Multi-Reflection Suppression® (MRS®) sensor technology, the new 5 micron Ultra-High Resolution MRS sensor offers unmatched accuracy by meticulously identifying and rejecting reflection based distortions caused by shiny components and surfaces. The result is ultra-high quality 3D images, high-speed inspection and metrology, and improved yields and processes.

Count on the Nordson SQ7000+ for superior performance for next-generation applications including advanced packaging, advanced SMT, mini/micro LED, 008004/0201 solder paste, and other next-gen applications.

**Save Time. Save Expense. Improve Yields.**

[nordson.com/testinspect](http://nordson.com/testinspect) | +1 760.918.8471

Copyright © Nordson Corporation. All rights reserved.

**Nordson**

*Test & Inspection*

Transmission image

Slice 1

Slice 2

Slice 3

## Look Past The Impossible.

# Dynamic Planar CT

Superior Software for Next Generation 3D Planar X-ray Inspection

### Revealing Incredible Details for Nordson's Zero Defects Strategy

Accelerated Image Acquisition and UPH > 2x faster than Planar CT.

Enhanced data quality with clear layer separation and new 3D reconstruction algorithm.

Larger FoV for increased coverage and shorter cycle times.

Reduced complexity and cost with no special clamping needed.

**Save Time. Save Expense. Improve Yields.**

[nordson.com/testinspect](http://nordson.com/testinspect) | +1 760.918.8471

Copyright © Nordson Corporation. All rights reserved.

**Nordson**

*Test & Inspection*

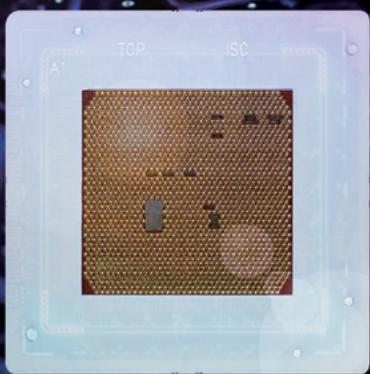

# Evaluation of indium TIM cross-sectioning methods on lidded high-performance microprocessors

By Neo Shao Ming, Song Mei Hui, Kevin Tan Bo Lin, Lee Xi Wen, Oh Zi-Ying, Foo Fang-Jie [Advanced Micro Devices (Singapore) Pte Ltd]

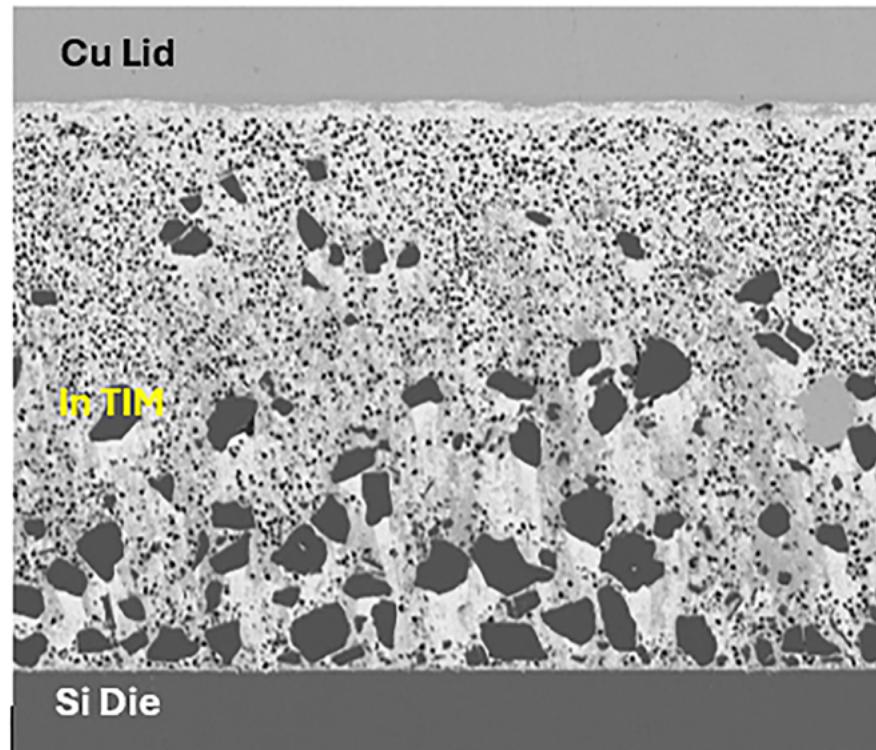

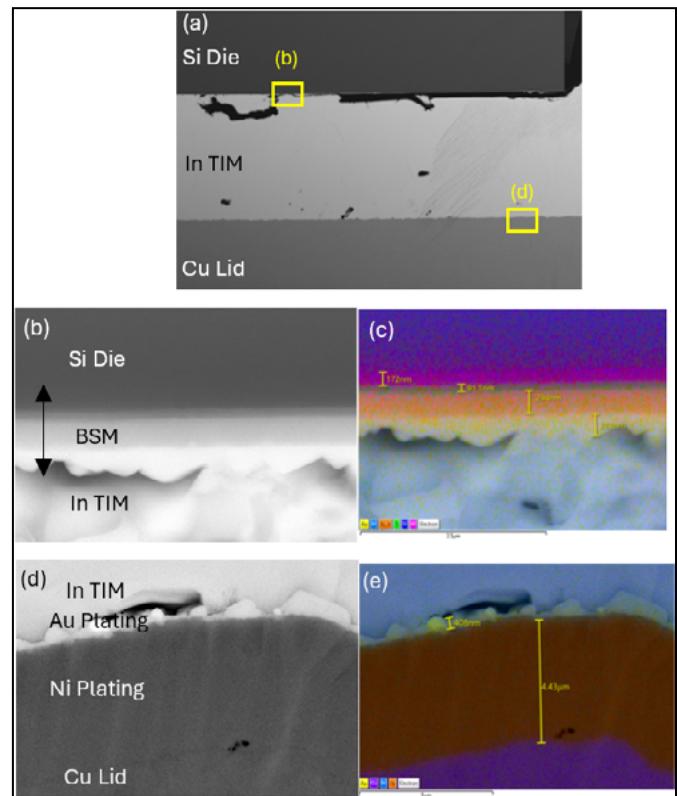

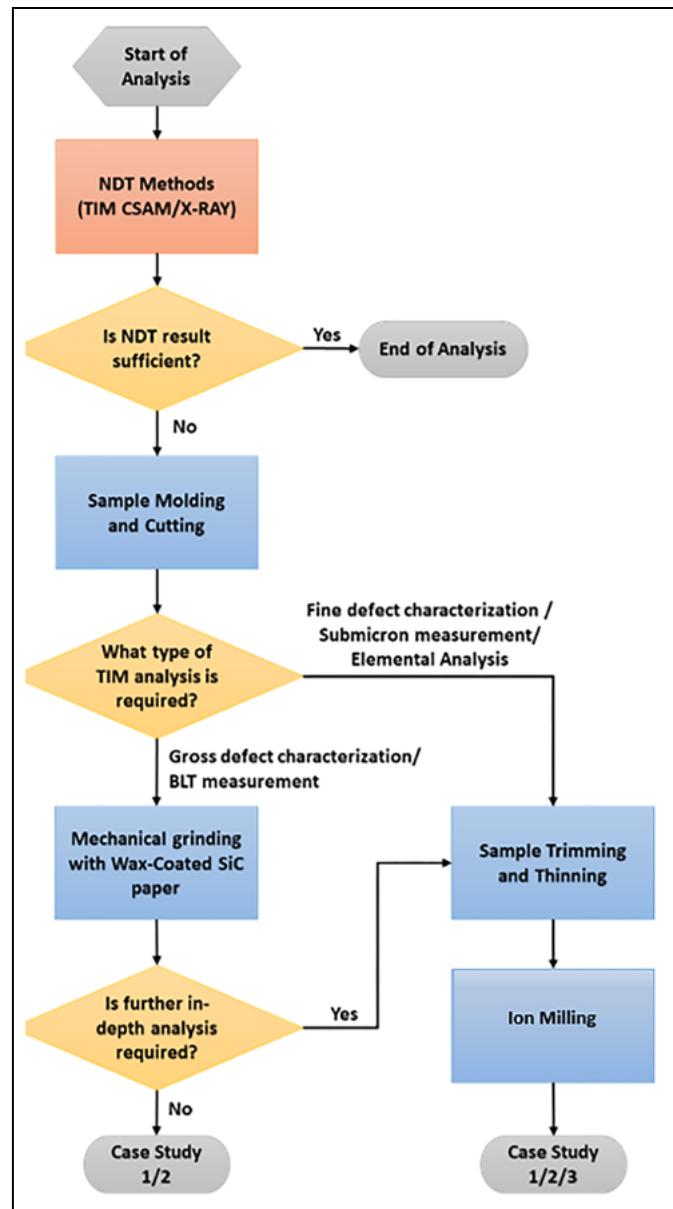

**V**oids, cracks, and insufficient thermal interface material (TIM) volume hinder heat dissipation and jeopardize reliability of lidded high-performance microprocessors. Nondestructive tests can effectively be used to inspect voiding conditions in TIMs, but destructive cross sectioning is imperative for in-depth analysis. A soft indium (In) TIM is sandwiched between the hard silicon die and the copper lid. Artifacts are, therefore, inevitably induced on the TIM during mechanical cross sectioning. In this paper, two cross-sectioning techniques were evaluated for an In TIM in lidded microprocessors: 1) Mechanical grinding with wax-coated silicon carbide papers, and 2) Ion milling. A thorough investigation on the pros and cons of each technique was conducted in order to conclusively select the most appropriate technique with respect to the requirements of turnaround time, area exposed and surface finish quality.

## Introduction

High-performance computing (HPC) microprocessors such as servers, artificial intelligence (AI) chips, and machine learning solutions tend to demand more power, and therefore, they tend to generate more heat as well. Without proper thermal dissipation, there is a high likelihood that a catastrophic failure could occur to the device, such as thermal overstress and thermal runaway [1]. There is a significant interest, therefore, to look at ways to improve on the thermal dissipation from such HPC microprocessors [2].

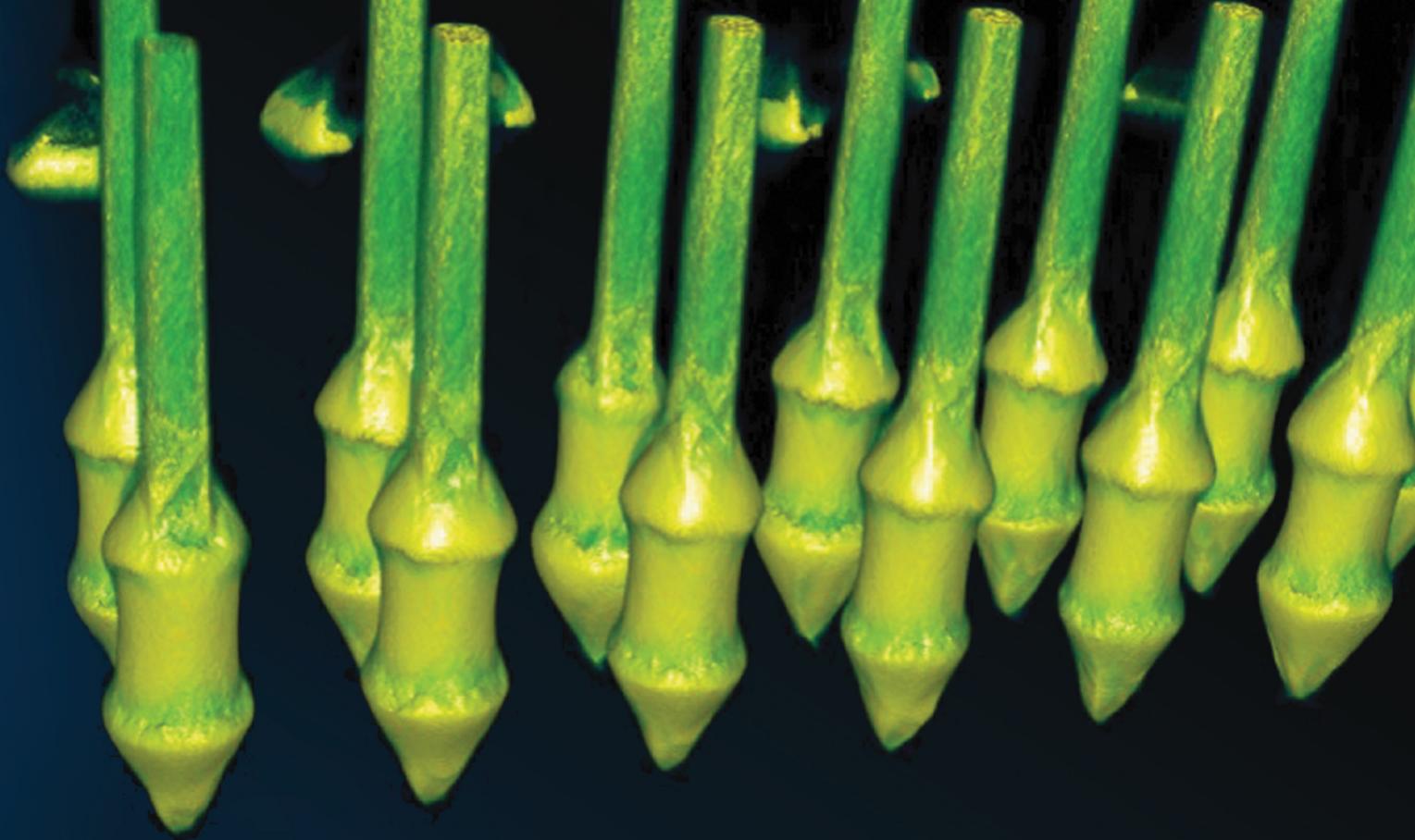

There are two main types of microprocessors as illustrated in Figure 1: 1) Lidless, and 2) Lidded. The lidless design in Figure 1a is typically used in laptop or embedded applications, while the lidded design in Figure 1b is typically used in desktop and server applications.

**Figure 1:** Schematic cross-sectional illustration of two general microprocessor designs used: a) Lidless and b) Lidded. (Legend: I – lid, II – TIM, III – die, IV – underfill and interconnects, V – stiffener, VI – substrate, VII – ball grid array.)

More recently, the lidded design can also be found in AI graphics applications.

The TIM plays a vital role in thermal dissipation—it is sandwiched between the die and lid, which is also referred to as the bond line. A bond line of a material is used to describe where a material contacts between two components. The TIM is an integral part of the lidded design because it provides a direct path between the die and the lid for thermal dissipation away from the die.

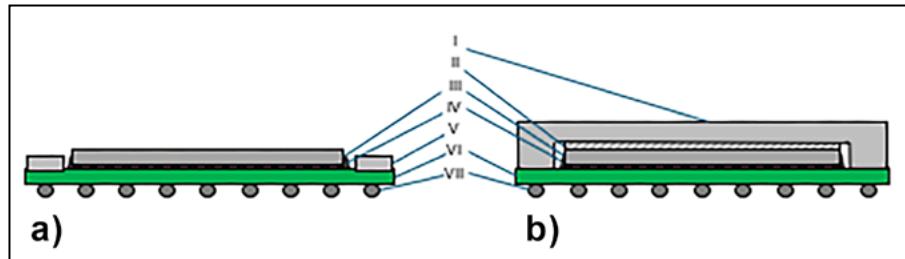

Traditionally, the TIM interface is analyzed via nondestructive testing (NDT) methods, such as a C-mode scanning acoustic microscope (CSAM), and two-dimensional (2D) X-ray. The working principle of the CSAM is based on the

reflection of acoustic signals at a set interface to detect materials of differing densities [3]. The acoustic signal will be fully reflected in the presence of air, so the analysis will have to take place in a liquid medium—usually water. At every material interface, some signal will be reflected. The working principle is further illustrated in Figure 2. CSAM helps with detecting voids and delamination at a set interface. X-rays utilize electromagnetic energy at the X-ray wavelength to generate an image with the image contrast being determined by the difference in absorption of X-rays by the different components in the materials [4]. Such NDTs help provide information on the presence of voids and the state of degradation of the TIM after various

**Figure 2:** Illustration of the basic working principle of CSAM to analyze a TIM interface with the device submerged in water: a) Full reflection of an acoustic signal upon contact with a void; and b) Partial reflection of an acoustic signal at material interfaces.

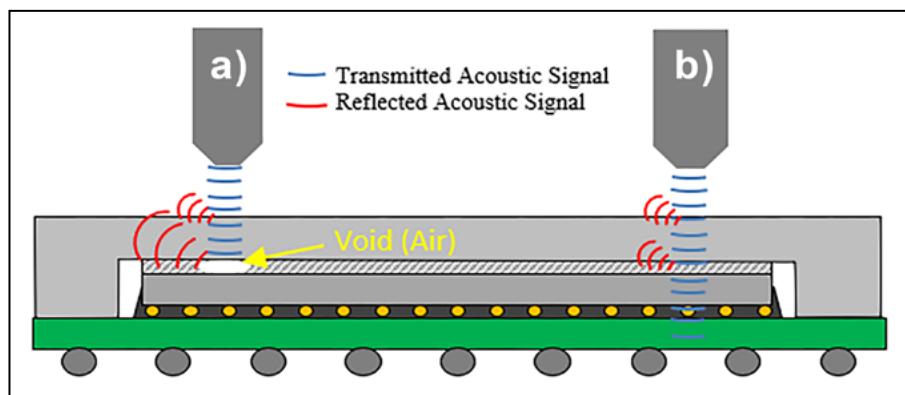

**Figure 3:** a) Cross-section image of a TIM void captured under scanning electron microscope (SEM); and b) TIM CSAM image of the sample with an indication of the cross-section location.

package reliability stress testing conditions, such as temperature cycling (TC) and high-temperature storage (HTS) tests.

Because NDTs only provide useful information from a planar perspective—a physically-destructive cross section must be performed on the device to collect cross-sectional information, such as bond line thickness (BLT) measurements and elemental analysis. For example, in Figure 3a we can see a void that was revealed via a physical cross section. The TIM CSAM image in Figure 3b was only able to detect the presence of the void, but the physical cross section was able to characterize the severity of the void.

### Problem statement

Currently, the complexity of microprocessors poses challenges when performing a physical cross section. In the above-mentioned high-performance applications, In TIM is sandwiched between the silicon (Si) die and copper (Cu) lid. The Mohs hardness values of these three materials are shown in Table 1, as well as typical abrasives used, such as silicon carbide (SiC) and alumina ( $\text{Al}_2\text{O}_3$ ). Mohs hardness is a measure of the resistance of a smooth surface to scratching or abrasion, expressed on an ordinal scale from 1-10 [5-6].

Physical cross sectioning is traditionally done by using a mechanical sample preparation method via grinding and polishing of the device. This is done using SiC sandpapers, followed by polishing

using an alumina polishing suspension to obtain a mirror surface finish. However, the broad range of Mohs hardness values of the three materials (1.2–6.5) made it difficult to prepare the sample for further analysis because grinding debris accumulate and become embedded in the In because In is softer compared to Cu and Si (see Figure 4). The presence of such embedded materials will affect the surface finish quality and will hinder elemental composition or microstructural analysis.

With the recent rise in interest to study In TIM reliability and the behavior of degradation for HPC products, there is also a growing interest in the refinement of sample preparation methods to achieve better surface finishing quality for such analyses.

The ability to perform such analyses will help to better understand the bond line interactions with the die and lid, which in turn, will help in improving the overall HPC product performance and reliability.

### Procedures

In general, sample preparation must be done prior to performing the cross section. The sample must be molded with epoxy to fill the gaps between the lid and substrate, as well as to encapsulate the full device. Encapsulation provides more structural support to the soft In TIM and prevents any alterations to the initial structural integrity of the sample. For lids without cutouts, the sides of the lid will have to be sawed off to create an opening into which the epoxy can flow. Afterwards, besides mechanical grinding, the sample must be trimmed down by cutting and parallel lapping due to equipment size limitations. The sections below discuss the new mechanical grinding and ion milling processes used in sample preparation.

**Mechanical grinding with wax-coated SiC grinding papers.** This method is a modification to the current mechanical grinding and polishing process. Instead of using a regular SiC grinding paper, a novel wax-coated SiC grinding paper is used.

**Table 1:** Mohs hardness values of the main materials present at the bond line interface, and abrasives used.

| Material Name            | Symbol                  | Mohs Hardness [6][7][8] |

|--------------------------|-------------------------|-------------------------|

| Indium                   | In                      | 1.2                     |

| Copper                   | Cu                      | 3.0                     |

| Silicon                  | Si                      | 6.5                     |

| Aluminum Oxide (Alumina) | $\text{Al}_2\text{O}_3$ | 9                       |

| Silicon Carbide          | SiC                     | 9.5                     |

**Figure 4:** Image of embedded particles in In TIM captured under SEM after mechanical grinding and polishing.

Before using the grinding paper, candle wax is first coated on the grinding paper surface. Wax has a Mohs hardness value of less than 1 [6], which is softer than In with a value of 1.2. This means that grinding debris will tend to get embedded in the wax instead of in the In during cross sectioning, which will then help to improve on the surface finish. The polishing step using the alumina polishing suspension was excluded to prevent alumina particles with a Mohs hardness of 9 from being embedded into the soft In TIM.

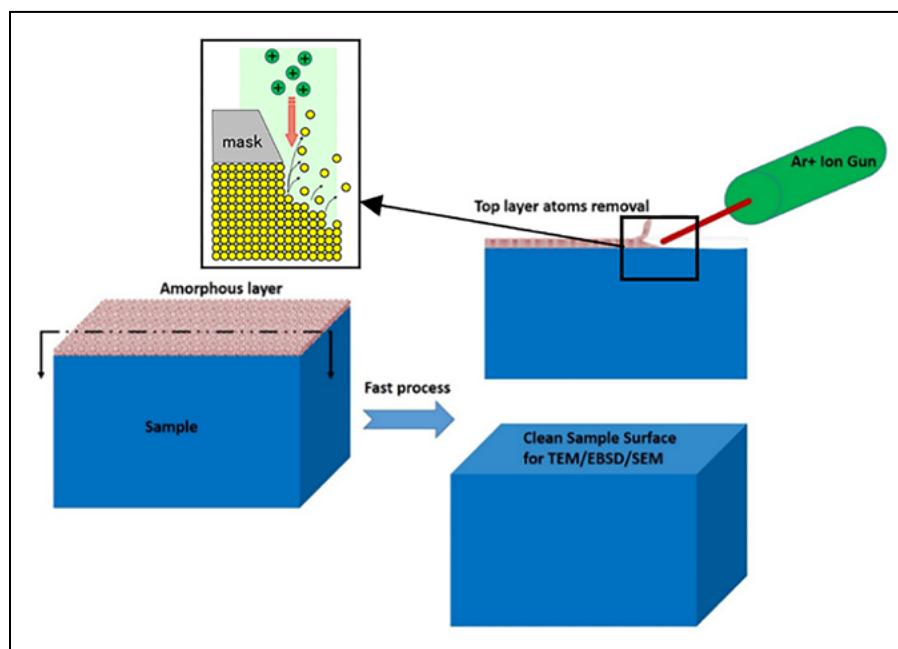

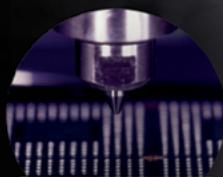

**Ion milling.** Ion milling is a process involving the removal of the top amorphous layer on a material to reveal the pristine sample surface for high-resolution imaging and post processing. It is typically used for transmission electron microscopy (TEM)

and electron back-scattered diffraction (EBSD) studies [9]. The removal of the top layer material is achieved via the physical bombardment of high-energy noble ions, usually argon ions ( $\text{Ar}^+$ ) across the surface. **Figure 5** is a schematic diagram showing the basic working principle.

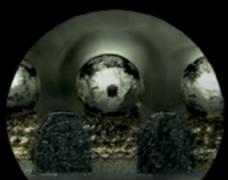

Although the scope of this project does not cover TEM and EBSD analyses specifically, a defect-free sample surface is still beneficial to providing accurate analysis results, especially for material characterization. However, In has a relatively low melting point of 156.6°C. Peak temperatures during ion milling can reach up to 376.9°C [10] and induce heat-affected zones, which are areas that have undergone changes in the microstructures of the material due to exposure to high

heat. As such, a cooling stage that uses liquid nitrogen as the cooling agent is utilized to mitigate the formation of the heat-affected zones. A comparison can be found in **Figure 6**. **Figure 6a** shows what happened without a cooling stage: the results were heating [11] and a curtaining effect [12]. These occurrences are largely mitigated when using a cooling stage, as demonstrated in **Figure 6b**.

After removing the top layer of material to expose the cross-sectional surface, a physical inspection and characterization in a SEM, were done, including TIM BLT and backside metallization (BSM) thickness measurements, and subsequently, material characterization using energy dispersive X-ray (EDX) spectroscopy or EBSD.

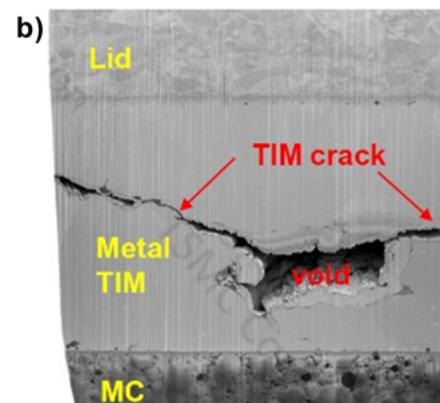

### Case study 1: TIM defect characterization on temperature cycling units

TIM cracks were reported on samples that were subjected to 3,000 cycles of temperature cycling at condition J (TCJ

**Figure 5:** Basic working principle of an ion miller.

**Figure 6:** Image of a sample that underwent ion milling: a) Without a cooling stage; and b) With a cooling stage.

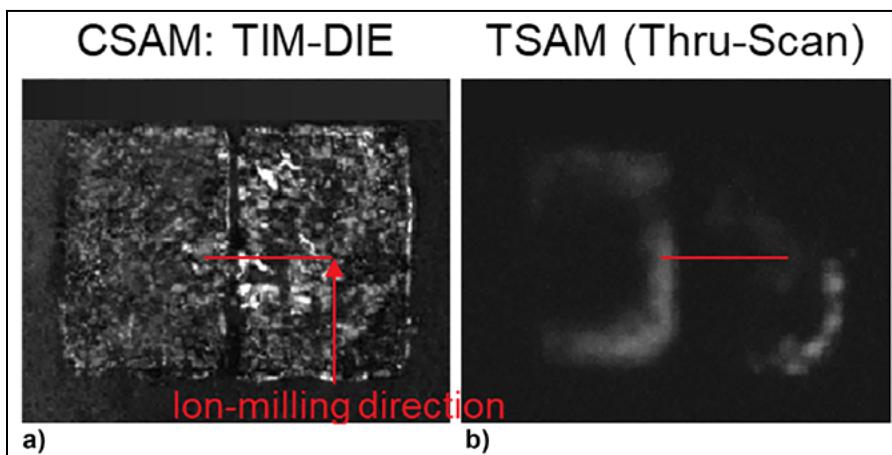

**Figure 7:** a) An acoustic through-scan micrograph after TCJ3000 showing TIM cracks; and b) FIB cross section at an acoustic through-scan dark area [red boxed area in **Figure 7a**] showing a metal TIM crack and void.

## BALL PLACEMENT & LASER SOLDERING

3D-Soldering

Solder Stacking

Wire Soldering

BGA Soldering

Pre-Soldering of SMD Connector Elements

Lid Sealing for Connectors & IR-Sensors

Flex to Chip Soldering

Through Hole Soldering

## LASER ASSISTED BONDING (LAB, LCB, LAR)

3D Multi Layer Stacked Packaging

Optoelectronic Device Assembly

CPU on Interposer Assembly

SMD Capacitor Assembly

## SOLDER & CHIP REPAIR

BGA Rework

Interconnects of Camera Module

BGA Package Assembly onto Substrate

Flex to Flex Separation

**WE MANUFACTURE

EQUIPMENT FOR

YOUR NEEDS**

3,000 cycles) based on JEDEC JESD22-A104D standards, where the temperature conditions are from 0-100°C.

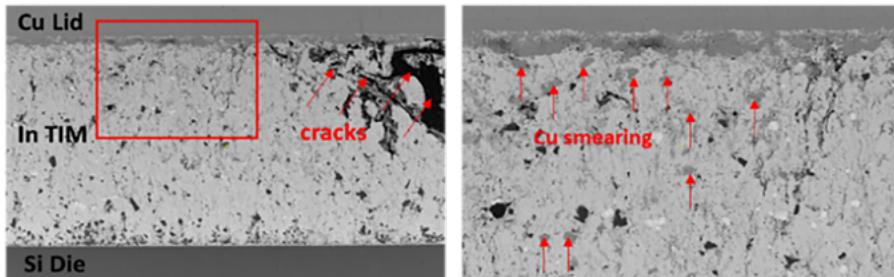

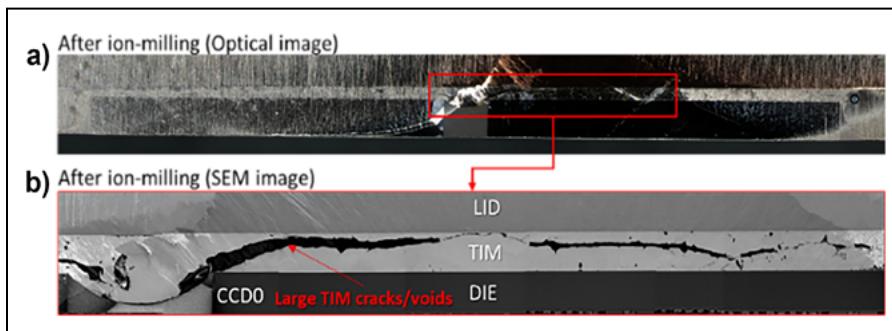

Acoustic through-scanning was employed to inspect for TIM anomalies as seen in **Figure 7a**, where they showed up as dark areas. Through-scanning detects the transmitted acoustic signals instead of the reflected ones from CSAM [13]. The dark areas were subsequently verified with focused ion beam (FIB) cross sectioning to be TIM cracks (**Figure 7b**). FIB milling is similar to ion milling, but instead of low energy Ar+ ions, high energy Ga+ ions were used [9].

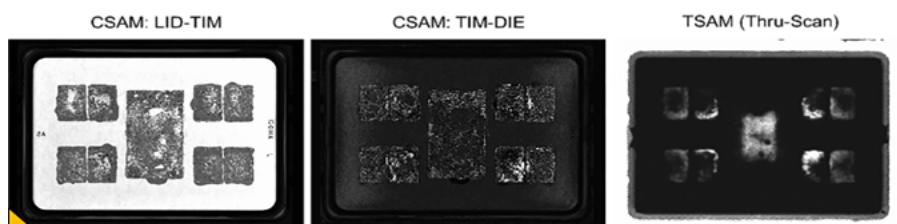

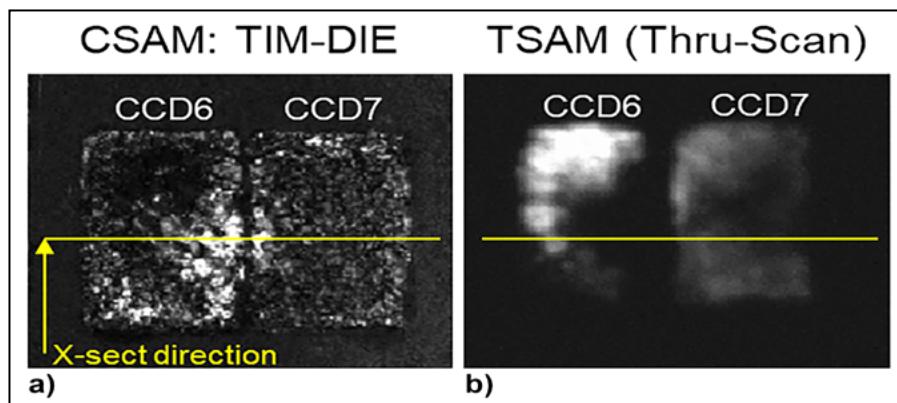

The inspection window of the FIB cross section revealed was only about 300µm wide and therefore, could not fully characterize this TIM anomaly and represent the TIM condition across its full length. We were then tasked to characterize the TIM condition across its full length. CSAM and through-scanning were first performed to inspect the TIM conditions on these units.

The sections below discuss the details with respect to mechanical grinding and ion milling.

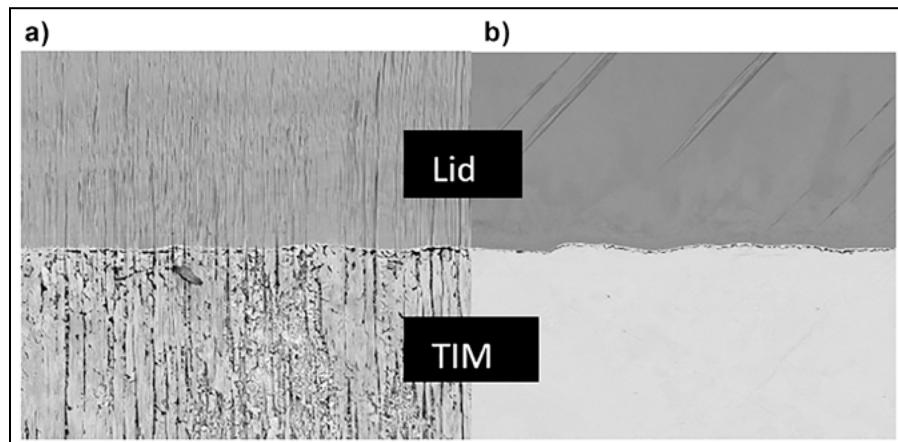

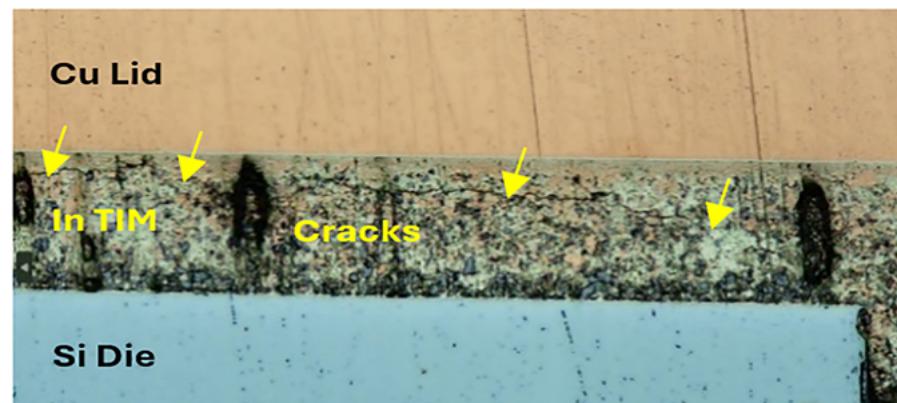

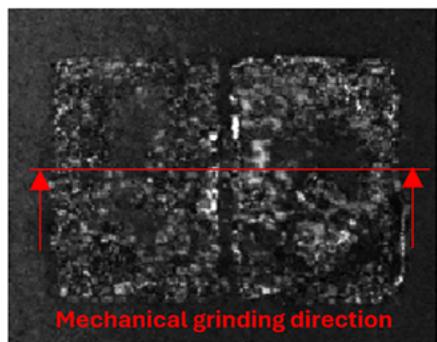

**Mechanical grinding.** Dark areas were first observed on the through-scan micrograph as seen in **Figure 8**. These areas also showed up as bright patches in CSAM micrographs at the TIM-die interface. The first attempt to characterize these acoustic signatures was via the traditional cross-sectioning method of mechanical grinding using SiC papers, followed by polishing with an alumina suspension. The cross section was performed at the location as shown in **Figure 9**.

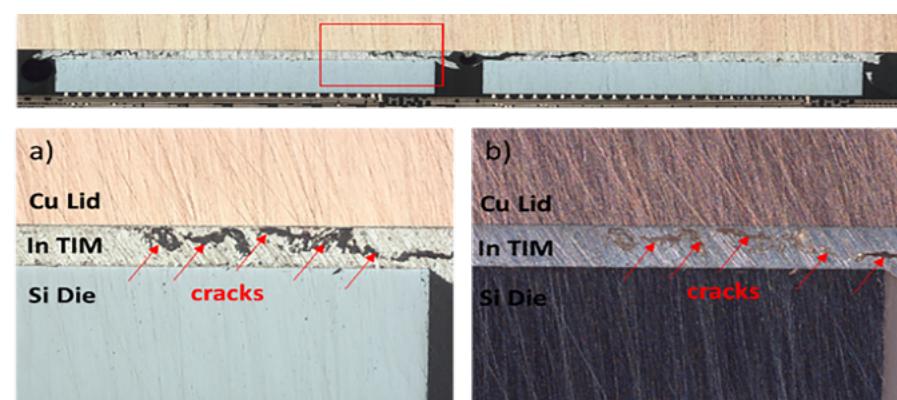

Large cracks were observed under an optical microscope (**Figure 10**) after mechanical grinding and polishing. However, embedded polishing debris and mechanically-induced artifacts were present after performing this method, as well as smearing of Cu from the lid into the In TIM. This smearing obstructs the view of In TIM cracks.

To minimize polishing debris and artifacts embedded in the In TIM interface, the mechanical grinding was subsequently performed using the wax-coated SiC grinding paper. A significant reduction in the amount of embedded debris was observed on the In TIM interface as seen from an optical microscope and SEM (**Figures 11-12**).

**Figure 8:** Acoustic CSAM and through-scan micrographs of a sample after TCJ3000 cycles.

**Figure 9:** a) An acoustic CSAM; and b) A through-scan micrograph zoom-in view of the sample, while indicating the cross-section location and direction.

**Figure 10:** Optical image showing embedded debris in a TIM of sample after mechanical grinding and polishing as seen under an optical microscope with bright-field illumination.

**Figure 11:** Optical overview at the TIM interface after performing mechanical grinding using wax-coated SiC grinding paper as seen under an optical microscope with zoom-in images under: a) Bright-field; and b) Dark-field illumination.

**Figure 12:** SEM Image of In TIM captured: a) After mechanical grinding with wax-coated SiC paper; and b) Zoomed-in with the focus on the presence of Cu smearing.

**Figure 13:** Acoustic CSAM micrograph zoom-in view showing the mechanical grinding location and direction.

Comparing the two mechanical grinding methods, the wax-coated SiC grinding paper helped in improving the overall surface finishing. TIM cracks appear clearer and more distinct due to much lesser embedded debris present at the In TIM cross-sectional surface. Although Cu smearing was still induced via this method, the smearing did not affect characterization of physical In TIM cracks to bright areas in the CSAM TIM-die interface across the full length as seen in **Figure 13**.

**Figure 14:** a) Acoustic CSAM; and b) Zoomed-in through-scan micrographs of Sample A denoting the ion-milling location and direction.

**Figure 15:** a) (top) Images showing the cross-section area exposed after ion milling under the optical microscope; and b) (bottom) In the SEM.

This case study successfully validated the inference of TIM cracks from through-scan observations and established that mechanical grinding with wax-coated SiC paper would be the best-known method for large area TIM cross-sectional analysis.

**Ion milling.** Alternatively, a cross-sectional surface exposed by mechanical grinding methods can be further improved using an ion milling method to achieve a clean surface finishing without surface defects. This is demonstrated on Sample A where the area with TIM cracks is subjected to ion milling (**Figure 14**). The exposed surface finish shows vast improvement, and is suitable for further material analysis such as EDX and EBSD. However, the cross-section surface exposed via this method is only limited to a small region (~4mm) as seen in **Figure 15**. Therefore, the reliability in understanding the cracks across the full length of TIM interface would be compromised. Furthermore, the ion milling method requires additional sample preparation compared to mechanical grinding. Coupled with the long milling time required, this significantly increases the turnaround time to achieve better finishing.

This successful characterization work helps to establish correlation between the CSAM signature on both the TIM-die interface and the through-scan to TIM cracks. This result simplifies future TIM crack screening via only CSAM, eliminating the need for constant cross-section verification. Details and outcomes of the various cross-section techniques used are summarized in **Table 2**.

| Method Criteria                             | Mechanical Grinding and Polishing                                                                    | Ion Milling                                                      |

|---------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Approx. Time Taken / day                    | 2 days (1 day molding +1 day grinding)                                                               | 5 days (1 day molding + 2 days sample prep + 2 days ion milling) |

| Length of TIM Cross-Section Surface Exposed | >50mm                                                                                                | 4.8mm                                                            |

| TIM Cross-Section Surface Finishing         | Poor (with embedded debris, scratches and smearing)                                                  | Good (artifact-free finishing)                                   |

| Remarks                                     | Wax coating on SiC paper improves cross-section finish. For overview inspection of gross TIM cracks. | For fine cracks inspection in TIM                                |

**Table 2:** Summary of cross-sectional methods used for the case study: TCJ3000 TIM characterization.

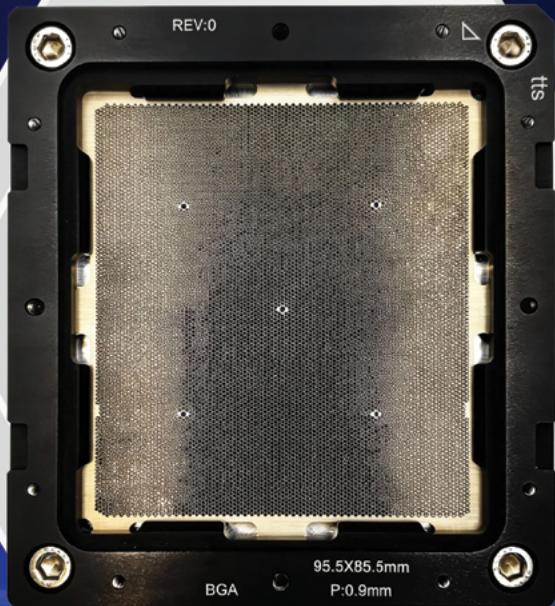

# HyperSocket™

*Your Ultimate Solution for*

## High-Speed

>224Gbps

## Large Package

>100X100mm<sup>2</sup>

## High-Power

>2000W

## Total Solution for Advanced Semiconductor Test

### Vertical Probe Card

Minimum pitch : 75 um

High pin count ≤ 40,000pins

### Coaxial Socket

SerDes 224Gbps PAM4

Supports up to 30,000 pins

### Functional Burn-in

High Power 1000W

High Speed PCIE Gen5 32Gbps

### Spring Probe

In-house manufacturing

### Optical Socket

SerDes 224Gbps PAM4

Optical alignment

### Thermal Product

3500W cooling capacity

Temperature : -40 to 150°C

## Case study 2: TIM analysis for VCL samples

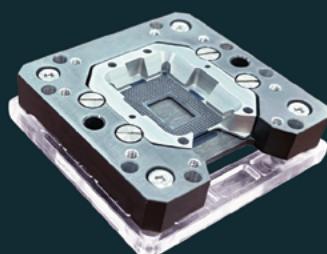

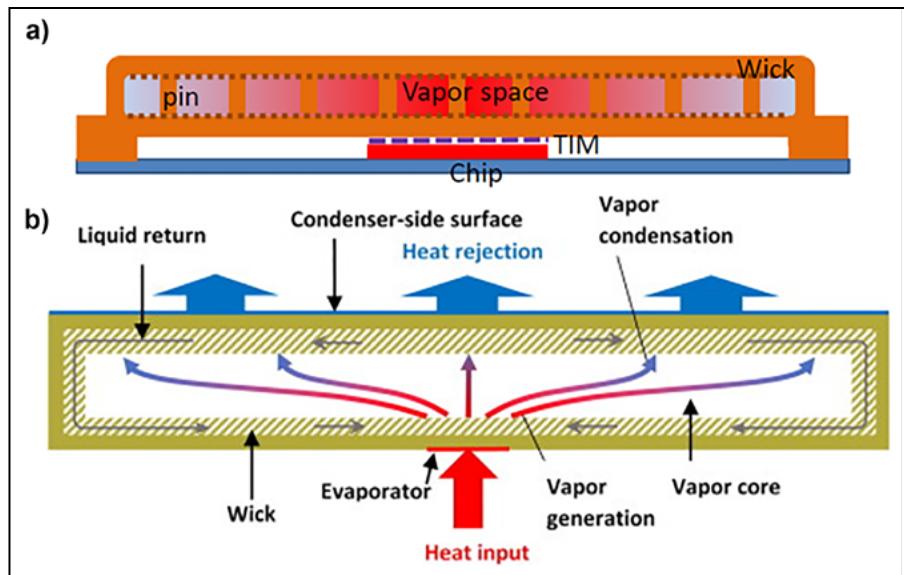

There is a new type of lid that is available on the market called a vapor chamber lid (VCL). A VCL utilizes a two-phase evaporative cooling system to provide higher thermal conductivity as compared to commonly used heat spreading materials. The working principle is illustrated in Figure 16, as well as a sample cross-section schematic of a microprocessor using VCL.

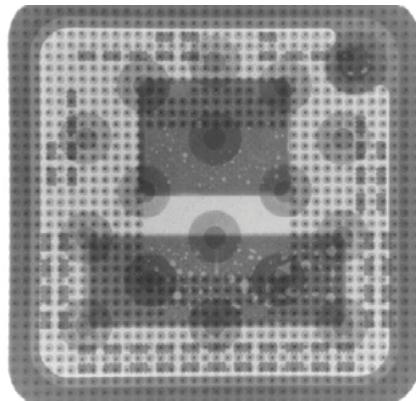

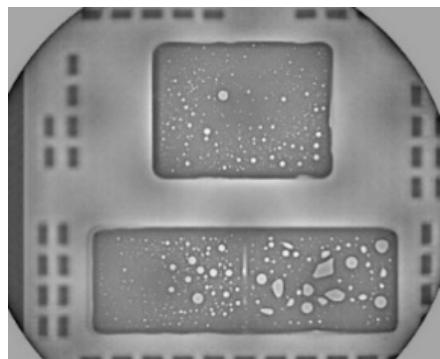

To analyze the TIM condition in VCL design, CSAM is not a suitable technique because acoustic signals are unable to penetrate through vapor and will be reflected before reaching the TIM interface. As such, X-ray methodology is used instead to inspect the TIM void condition. Denser materials will appear darker in contrast, and the reverse is true for lighter materials. An example of an image captured using X-rays is shown in Figure 17.

As seen in Figure 17, information with respect to the entire stack of the sample is being revealed as the X-ray penetrates through the whole sample. This causes difficulty in inspecting the TIM void

Figure 17: X-ray image of a VCL sample.

Figure 18: X-ray laminography image of the TIM interface on the same VCL sample.

Figure 16: Illustration of: a) (top) Cross section of a package with VCL; and b) (bottom) Working principle of a VCL.

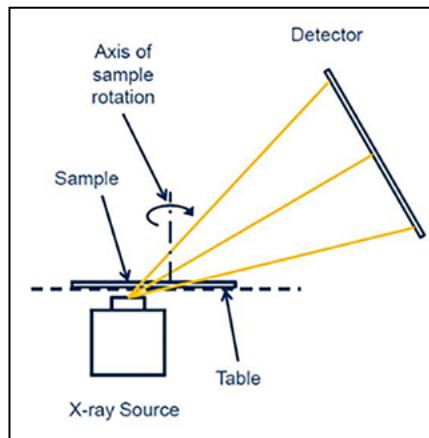

condition because the overlapping layers provide unwanted information. In this case, a special type of imaging technique known as X-ray laminography [14] was used to obtain the specific plane of the TIM interface as shown in Figure 18 for further TIM void characterization. For this technique, the detector is set at an oblique angle to the source (Figure 19). 2D projections are then captured 360° around the sample and the specific plane of the TIM interface can be obtained with the reconstructed data.

Figure 19: Schematic diagram showing the setup for X-ray laminography [15].

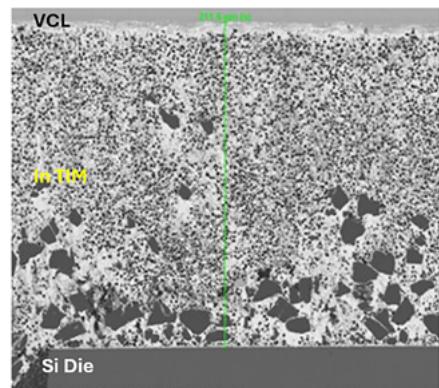

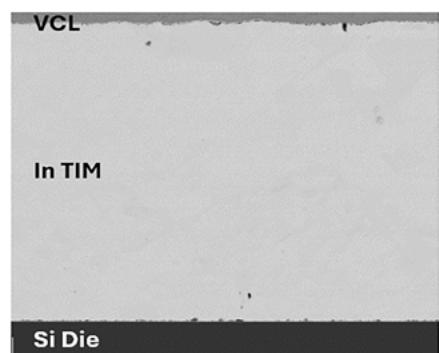

Subsequently, cross sections were performed on the samples via different methods for BLT measurement of the TIM interface, as well as to look for any potential delamination at both the VCL-TIM and TIM-die interfaces. The first

method was done via mechanical grinding and polishing, which can be seen in Figure 20. The embedded debris present did not inhibit the measurement of the TIM BLT.

Figure 20: SEM image of a VCL cross-section sample done via the traditional mechanical grinding and polishing method; the green line represents the BLT measurement taken.

Figure 21: SEM image of a VCL sample after performing an ion milling cross-section method.

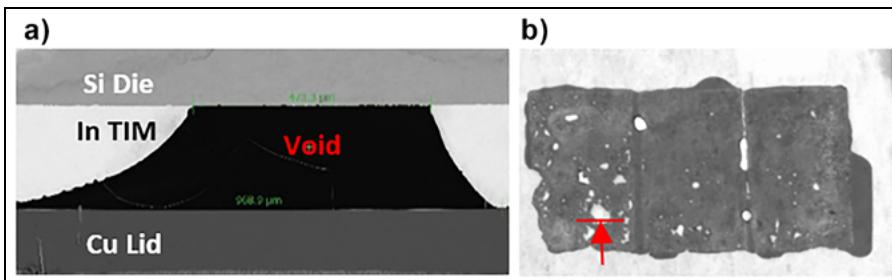

Inspection of fine-pitch delamination ( $<10\mu\text{m}$ ) demands a high-quality surface finish. As such, ion milling cross sectioning is done on the VCL sample. Results of the ion milling process can be seen in **Figure 21**, where the surface is free from defects and debris, aside from inherent voids that were present in the sample. Delamination was not observed in the milled sample.

For TIM BLT analysis, both methods can obtain results, but when fine-pitch delamination is of interest, only ion milling can be used for analysis because the artifact-free surface finishing that it can achieve. Any artifacts, such as debris embedment and metal smearing, may mask any inherent fine-pitch delamination observations. Details and outcome of the various cross-section techniques used are summarized in **Table 3**.

| Method Criteria                             | Mechanical Grinding and Polishing       | Ion Milling                                                       |

|---------------------------------------------|-----------------------------------------|-------------------------------------------------------------------|

| Approx. Time Taken / day                    | 2 days (1 day molding + 1 day grinding) | 7 days (1 day molding + 3 days sample prep + 3 days ion milling)  |

| Length of TIM Cross-Section Surface Exposed | >22 mm                                  | 2.5 mm                                                            |

| TIM Cross-Section Surface Finishing         | Poor (with embedded debris)             | Good (free from artifacts and debris)                             |

| Remarks                                     | For TIM BLT measurement                 | For inspection of TIM interfacial delamination (Preferred method) |

**Table 3:** Summary of cross-sectional methods used for TIM analysis for VCL samples.

### Case study 3: TIM analysis on power cycling units

The main objective for this case study is to compare the TIM degradation condition of a sample at  $T=0$  and after power-cycling 4,600 cycles, and to see if there is any difference in thermal resistance as a result of TIM degradation.

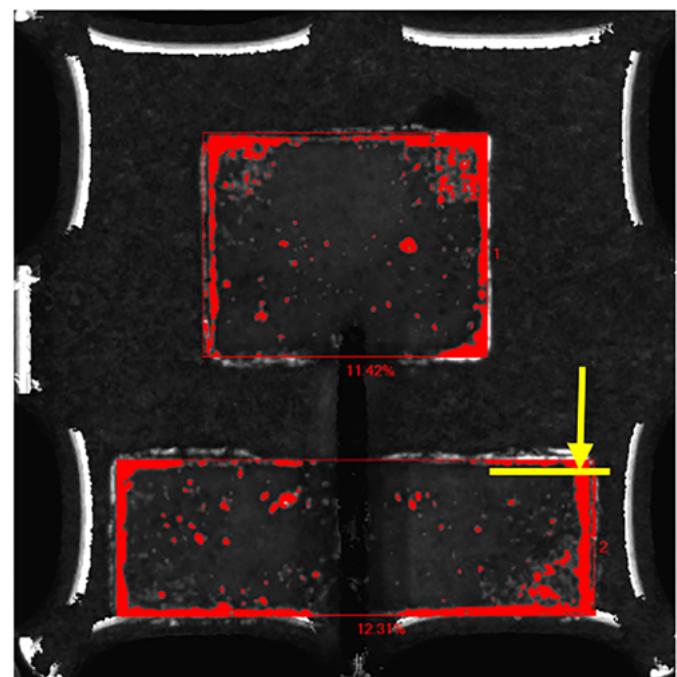

CSAM and through-scanning were done to first compare and characterize the TIM degradation condition. Subsequently, a cross section was performed at TIM non-contact regions based on CSAM results. An example can be seen in **Figure 22** where the CSAM's void detection software is used to determine areas where the In TIM has no contact with the lid or die. The areas highlighted in red are areas where the TIM has no contact at the TIM-die interface.

A physical correlation study of the TIM condition is then done by performing cross sectioning—more specifically by looking at the BSM—a complex layer comprising aluminum-titanium-nickel vanadium-gold (Al-Ti-NiV-Au). This complex layer is in contact with the Si die and the In TIM, as well as the nickel-gold (Ni-Au) lid plating that is in contact with the In TIM. As BSM is of sub-micron thickness, any irregularities or induced defects would make the measurement inaccurate. Hence, ion milling was the chosen method to perform this analysis, because a pristine surface finish can be achieved to minimize any defects that would affect the final measurement results (see **Figure 23a**). Delamination was observed at the TIM-die interface, which correlates to the TIM non-contact regions as seen from the CSAM results in **Figure 22**.

In **Figures 23b-c**, the SEM and EDX can effectively capture the different layers of the BSM, as well as make

**Figure 22:** CSAM image of a sample with TIM non-contact regions highlighted in red by the CSAM's void detection software at the TIM-DIE interface—while also showing the cross-section location and direction.

**Figure 23:** SEM images of a cross-section sample: a) After performing the ion milling cross-section method; b) With a focus on the BSM interface; c) After EDX was performed showing the breakdown of elements present at the BSM interface and their thickness measurements in yellow; d) With a focus on the Ni-Au plating interface; and e) After EDX was performed showing the breakdown of elements at the Ni-Au plating interface along with their thickness measurements in yellow.

measurements with a reasonable degree of accuracy due to the absence of cross-section-induced defects. Likewise, in Figures 23d-e, the Ni-Au lid plating thickness can be measured, along with the respective elemental compositions. Details and outcomes of the various cross-section techniques we used are summarized in Table 4.

| Method Criteria                             | Ion Milling                                                      |

|---------------------------------------------|------------------------------------------------------------------|

| Approx. Time Taken / day                    | 7 days (1 day molding + 3 days sample prep + 3 days ion milling) |

| Length of TIM Cross-Section Surface Exposed | 4mm                                                              |

| TIM Cross-Section Surface Finishing         | Good (without any artifacts and debris)                          |

| Remarks                                     | Elemental analysis at TIM interfaces (BSM and lid plating)       |

**Table 4:** Summary of cross-sectional methods used for TIM analysis on power cycling units.

| Method Criteria                             | Mechanical Grinding and Polishing                      | Ion Milling                                                               |

|---------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------|

| Approx. Time Taken / day                    | 2                                                      | 5-7                                                                       |

| Length of TIM Cross-Section Surface Exposed | Full length (Sample B TIM Length: 50mm)                | 4.8mm                                                                     |

| TIM Cross-Section Surface Finishing         | Poor (Embedment of grinding debris)                    | Good (Free from artifacts and debris)                                     |

| Type of Applications                        | For BLT measurements and gross TIM defect observations | For elemental studies, submicron measurements and fine defect observation |

**Table 5:** Comparison of the time taken, length of surface exposed, and surface finishing of the three cross-sectional methods, as well as the type of applications for each method.

Each method of sample preparation comes with its own pros and cons, which are listed in Table 5, where the time taken to perform the method, the surface area of the sample able to be prepared by the method, as well as the surface finishing quality are investigated and ranked. The two techniques complement each other by allowing all analyses to be done in-house, removing the need for outsourcing, thereby saving cost. Figure 24 serves as a comprehensive toolkit and guide to the optimized sample preparation techniques for various analysis requirements.

## Summary

From this evaluation, a comprehensive toolkit was developed to curate the best-known sample preparation method for various analysis requirements. This evaluation took place after thorough consideration of the time taken for cross sectioning, the size of area exposed, as well as the surface finish. The evaluation also showcased our ability to incorporate unconventional solutions such as common household items (in the case of candle wax), and nonstandard

**Figure 24:** Flowchart of the TIM cross-section sample preparation best-known method (BKM).

upgrades (in the case of cold stage in ion milling) to industry standard cross-sectional techniques to meet the ever-changing failure analysis demands for new products, especially in the server and AI segments. By deploying the appropriate cross-sectional methods, we can effectively characterize the samples and optimize the time taken based on the requirements—be it for failure analysis or construction analysis. This will help to determine the root cause of failure or facilitate the understanding of the buildup and interactions of the device, which will then help to provide the appropriate corrective action or improvements. To date, these cross-sectional methods have been effectively demonstrated in multiple reliability characterization studies, as well as with respect to customer returns within AMD.

## Acknowledgments

Many thanks to DA Lab Package Team members who have helped in one way or another, such as to collect valuable analysis data and providing their knowledge and expertise, which led to the completion of this evaluation. AMD, the AMD Arrow logo and combinations thereof are trademarks of Advanced Micro Devices, Inc. Portions of this article were presented at EPTC 2024—this version was edited for publication in *Chip Scale Review*.

## References

1. V. Lakshminarayanan, N. Sriraam, “Analyzing thermal runaway in semiconductor devices using the constrained method of optimization,” International Conf. on Circuits, Controls and Communications (CCUBE), 2013.

2. R. Mahajan, C. Chiu, R. Prasher, “Thermal interface materials: A brief review of design characteristics and materials,” *Electronics Cooling*, vol. 10, no. 1, p. 10, 2004.

3. F. J. A. Rebollo, “Working Process Of C-SAM In EEE Parts | doEEEt.com,” Alter Technology, 28 March 2019. [Online]. Available: <https://www.doeet.com/content/testing-eee-parts/inspection-electrical-verification/working-process-of-scanning-microscopy-c-sam/>. [Accessed 27 January 2023].

4. G. T. X Zhou, “Electron and Photon Based Spatially Resolved Techniques,” Reference Module in Materials Science and Materials Engineering, 2017.

5. The Editors of Encyclopaedia Britannica, “Mohs hardness,” Encyclopaedia Britannica, 15 September 2022. [Online]. Available: <https://www.britannica.com/science/Mohs-hardness>. [Accessed 21 November 2022].

6. Editorial Team, “Mohs Hardness Scale Meaning and How to Use It to Test Hardness | Science Drill,” 6 July 2022. [Online]. Available: <https://sciedrill.com/mohs-hardness-scale/>. [Accessed 3 May 2023].

7. G. V. Samsonov, Ed., “Mechanical properties of the elements,” in *Handbook of the Physicochemical Properties of the Elements*, New York: Plenum Publishing Corporation, 1968, pp. 387-446.

8. “Reade Advanced Materials - Mohs’ Hardness (Typical) of Abrasives,” Reade International Corp., 2022. [Online]. Available: <https://www.reade.com/reade-resources/reference-educational/reade-reference-chart-particle-property-briefings/mohs-hardness-typical-of-abrasives>. [Accessed 17 January 2023].

9. Nanoscience Instruments, “Ion Milling - Nanoscience Instruments,” 2023. [Online]. Available: <https://www.nanoscience.com/techniques/ion-milling/>. [Accessed 8 February 2023].

10. B. Viguier, A. Mortensen, “Heating of TEM specimens during ion milling,” *Ultramicroscopy*, vol. 87, pp. 123-133, April 2001.

11. A. W. Thompson, Z. D. Harris, J. T. Burns, “Examination of focused ion beam-induced damage during platinum deposition in the near-surface region of an aerospace aluminum alloy,” *Micron*, vol. 118, pp. 43-49, 2019.

12. K. Larsen, “The Effects of Ga FIB Milling on Analysis - Oxford Instruments,” 28 July 2021.

13. K. Mugunan, L. C. Ying, C. C. Fei, “Verification of delamination observed in SAM transmission mode (Thru-scan) using reflection mode (C-SAM Bottom Scan),” IEEE 38th International Electronics Manufacturing Technology Conf. (IEMT), Melaka, Malaysia, 2018.

14. M. Holler, M. Odstrčil, M. Guizar-Sicairos, M. Lebugle, U. Frommherz, T. Lachat, et al., “LamNI – an instrument for X-ray scanning microscopy in laminography geometry,” *Jour. of Synchrotron Radiation*, vol. 27, no. 3, pp. 730-736, 2020.

15. A. Gerwe, “Utilizing Computed Tomography (CT) for Printed Circuit Board (PCB) Inspections and Reverse Engineering - 3D Engineering Solutions,” 4 June 2020. [Online]. Available: <https://3d-engineering.net/ct-scanning-for-pcb-inspection-reverse-engineering/>. [Accessed 24 May 2023].

## Biographies

Neo Shao Ming is a Senior Product Development Engineer at Advanced Micro Devices (Singapore) Pte Ltd, Singapore. He specializes in semiconductor packaging failure analysis with a strong emphasis on advanced sample preparation of complex packaging technologies. His work focuses on enabling accurate defect localization, supporting root-cause investigations, and driving process optimizations and improvements. He is passionate about advancing analytical capabilities to improve product performance and reliability. Email [neo.shaoming@amd.com](mailto:neo.shaoming@amd.com)

Song Mei Hui is a Senior Product Development Engineer at Advanced Micro Devices (Singapore) Pte Ltd, Singapore. She brings extensive experience in nondestructive analysis techniques—specializing in thermal interface materials characterization and voiding studies. Her technical expertise encompasses advanced failure analysis methodologies for high-performance microprocessors, with a focus on material integrity assessment and process optimization. She has contributed significantly to developing cross-sectioning evaluation methods for indium TIM applications in lidded packages.

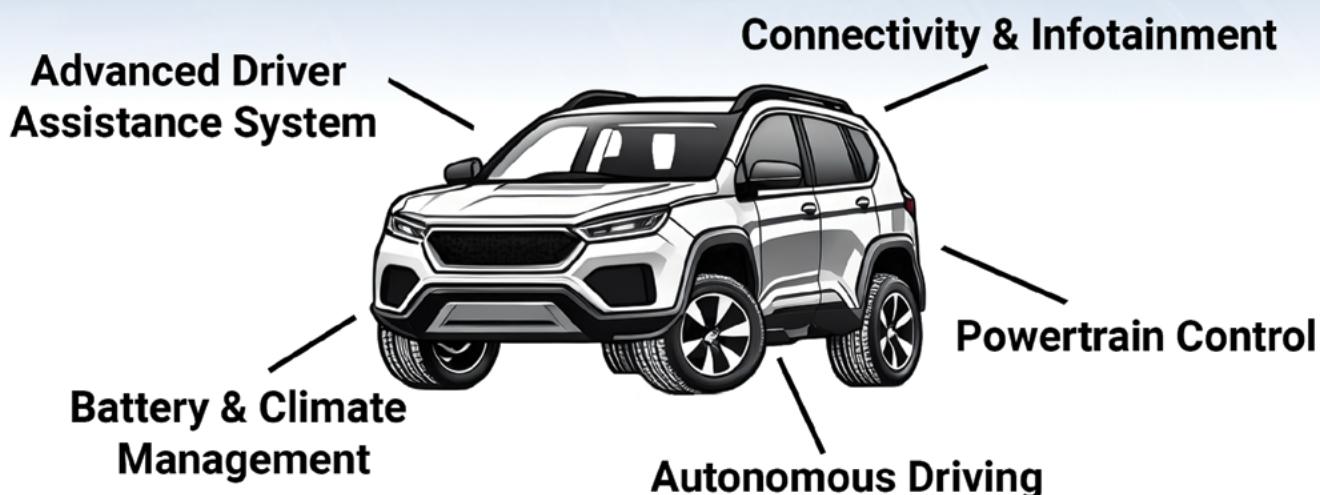

# Enjoy the Ride When Burn-In Has Been Applied

As automotive systems evolve, semiconductor reliability is critical to the enjoyment, safety, and comfort of the driver and passengers.

Semiconductor devices that complete a burn-in cycle in a Micro Control Company burn-in with test system are significantly more reliable for long-term use.

For the long road ahead, turn to Micro Control Company,

The Advanced Burn-In Solution Provider.

Enabling Tomorrow's Semiconductor

Optimized Advanced Interconnection Solution

**"Innovating Semiconductor Testing"**

Three-in-One integrated

**Interconnection**

Hardware

Probe Card

Test Interface Board

Test Socket

TSE's iBunify architecture integrates Probe Cards, Test Interface Boards, and Test Socket technology, providing an optimal integrated test solution that flexibly responds to various semiconductor chip test requirements. This solution combines integration and flexibility, integrating all components into one efficient system.

A revolutionary three-in-one integrated solution shaping the future of semiconductor testing

iBunify

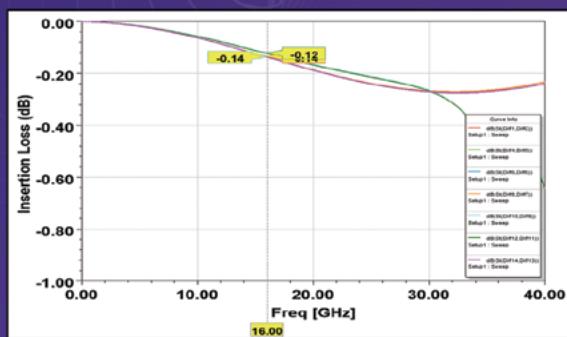

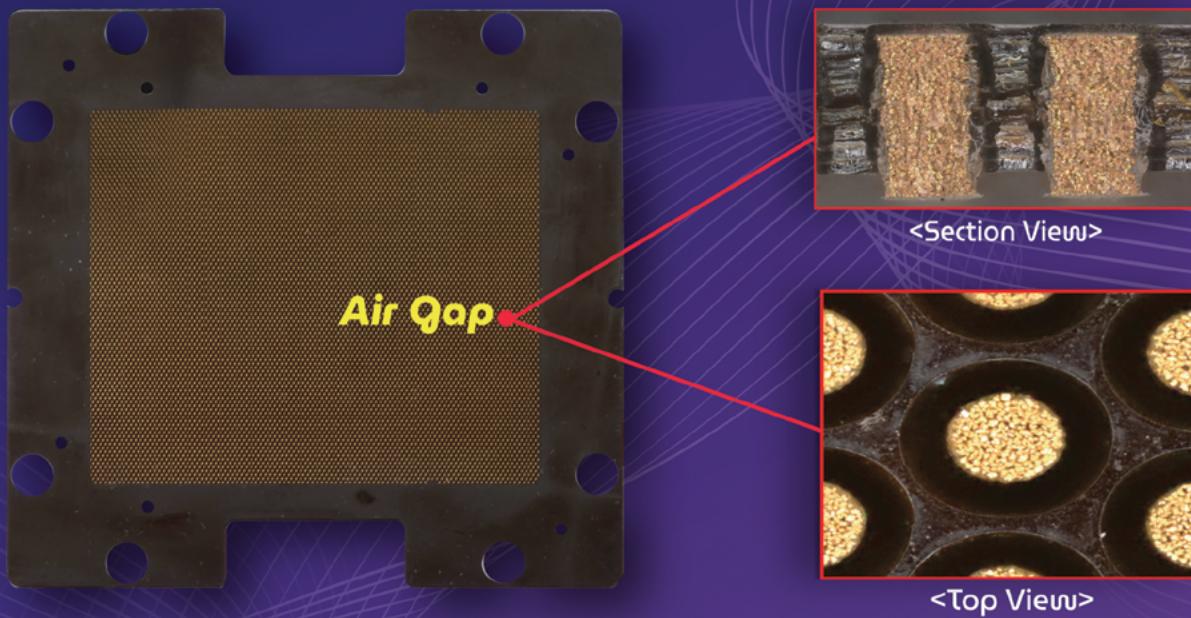

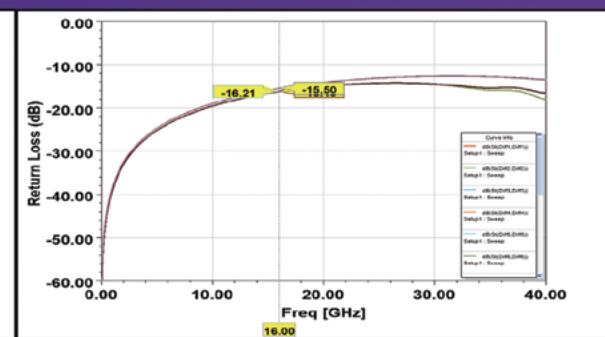

# ELTUNE-air™

## Independent Stroke and Enhanced SI Performance by air gap

### Insertion Loss(dB)

## Return Loss(dB)

# Using polynomial regression for heterogeneous package stress modeling

By Kart Leong Lim, Ji Lin [Institute of Microelectronics (IME), Agency for Science, Technology and Research (A\*STAR)]

**H**igh stress occurs when 3D heterogeneous integrated circuit (IC) packages are subjected to thermal cycling at extreme temperatures. Finite element analysis (FEA) is widely used to predict such stresses without the need of an actual prototype. FEA, however, does require specialized knowledge and usually is computationally expensive, as well as time consuming. However, testing in a production environment requires simplified, but accurate, stress prediction tools to provide quick answers and solutions within a short time frame. Therefore, FEA may not be the right tool for stress prediction. We present an artificial intelligence (AI)-based stress predictor tool that allows engineers with no FEA background to perform fast and efficient routine package stress checks for testing and production purposes.

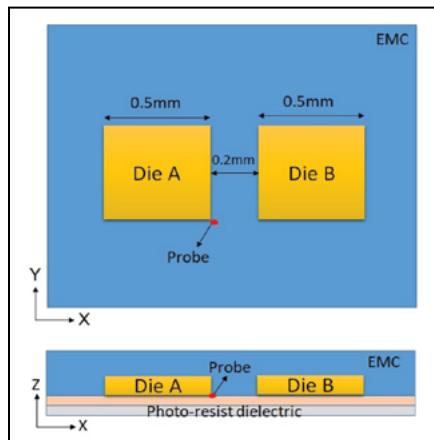

To demonstrate the AI-assisted stress predictor tool, stress in a simple two-chip package (**Figure 1**) was studied. There are two main problems encountered when developing a stress predictor tool—the development of the AI stress predictor tool was focused on addressing them (see the sections below).

**Figure 1:** Probe on a 2-dies package for stress prediction. Stress (MPa) occurs at the bond between different materials when subjected to thermal cycling ( $-55^{\circ}\text{deg}$  to  $150^{\circ}\text{deg}$ ). The X and Y axes refer to the plane, while the Z and X axes refer to the side view.

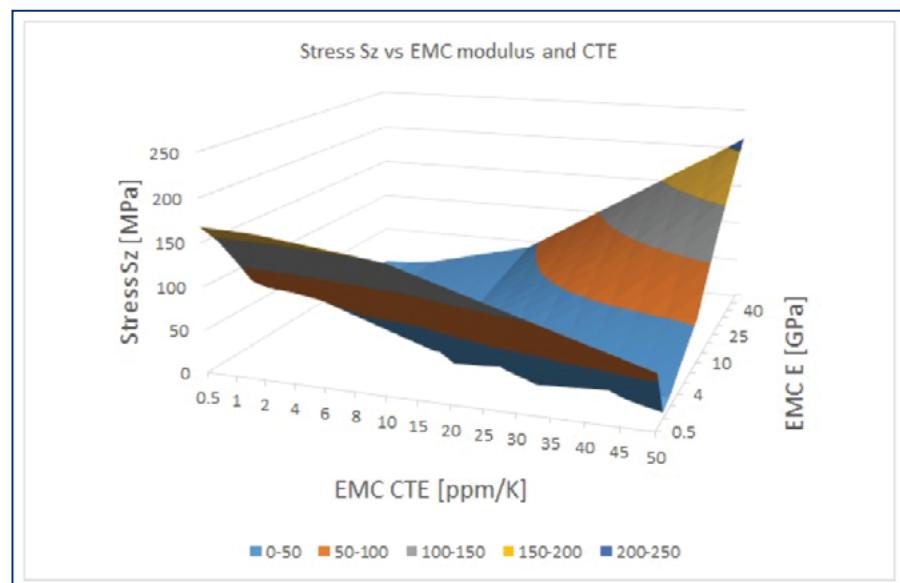

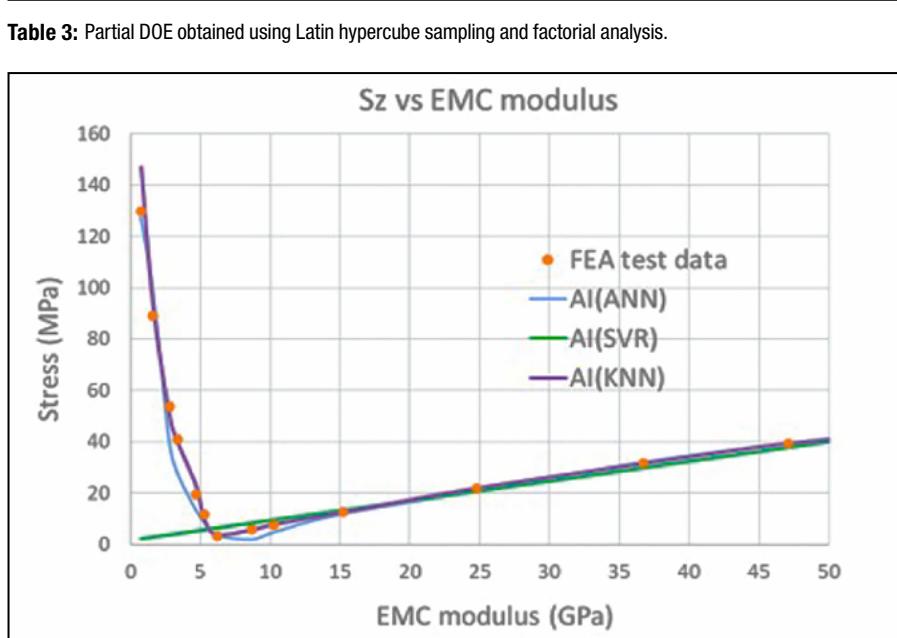

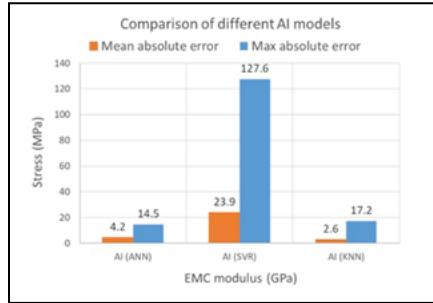

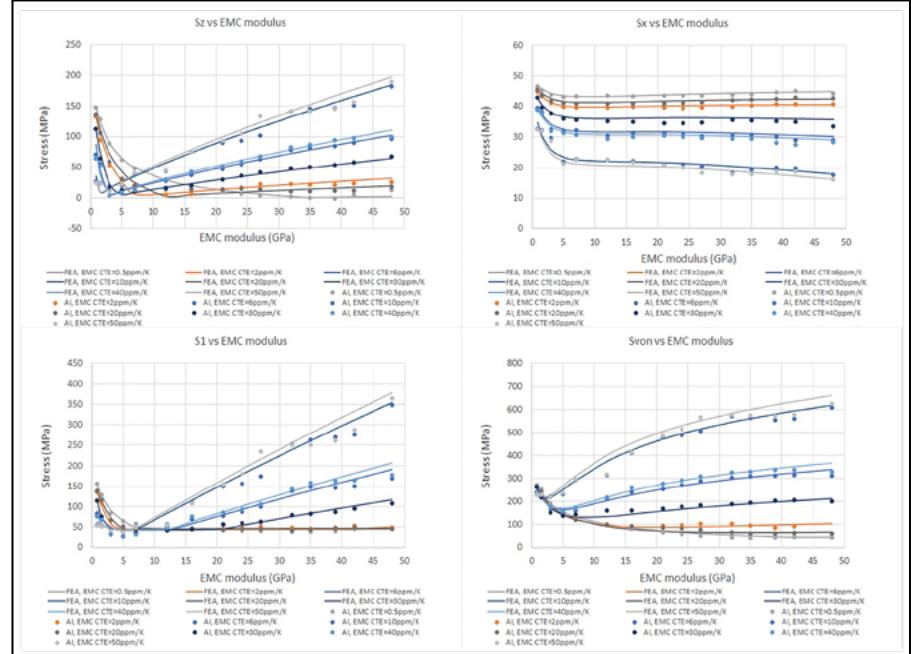

**Nonlinearity.** Although vanilla deep regression has the capability to perform stress modeling, the input (design and material variables) and output (various stress vectors) of the problem is highly nonlinear. The nonlinearity can be studied from the simple viewpoint of a two-input variable problem. **Figure 2** shows that the response of the stress  $S_z$  to the epoxy molding compound (EMC) modulus and

AI in the first place. Other practical issues include the number of man-hours and equipment cost (i.e., scientist/engineer with a mechanical stress background, ANSYS subscription, and a powerful workstation).

Recent excellent works related to mechanical stress modeling using state-of-the-art deep learning include papers found in [1-5]. Nie, et al. [5], first published an image-based stress dataset

**Figure 2:** Stress response corresponding to a two-input variables case is asymmetric and saddle shaped.

coefficient of thermal expansion (CTE) is in the shape of an asymmetrical saddle. Such a nonlinear response is a challenge for AI to model  $S_z$  accurately when a limited training dataset is available. Furthermore, for stress prediction to be useful to real-world problems, it has to cope with more than two inputs and one output variable.

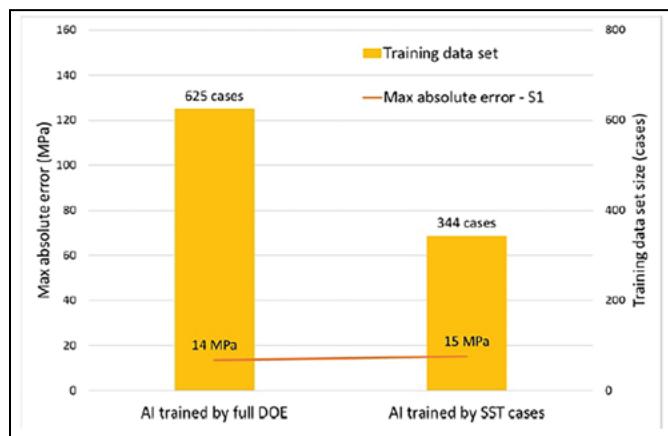

**Dataset.** We used commercial FEA software (ANSYS) to generate a training dataset (**Table 1**). Generating a large dataset with more variables is not only computationally demanding, but having a full DOE defeats the purpose of using

of 2D structures with 120,960 samples. The authors used shape, boundary conditions and load conditions of a fine-mesh structure as inputs for training convolutional neural networks (CNN), which they call StressNet. Subsequently, Jiang, et al. [1], trained a generative adversarial net (GAN) known as StressGAN to perform a stress prediction. The generator takes in the shape, boundary and load conditions and outputs a stress image, while the discriminator tries to identify it. Concurrently, Yang, et al. [2], also used GAN to predict the stress field for a material composite.

| 100 training data sets |                      |                      |                      |                      |       |                      |                      |                      |                      |       |                      |                      |

|------------------------|----------------------|----------------------|----------------------|----------------------|-------|----------------------|----------------------|----------------------|----------------------|-------|----------------------|----------------------|

| Data#                  | Input                |                      | Output               |                      | Data# | Input                |                      | Output               |                      | Data# | Input                |                      |

|                        | EMC Modulus<br>[GPa] | Sz at probe<br>[MPa] | EMC Modulus<br>[GPa] | Sz at probe<br>[MPa] |       | EMC Modulus<br>[GPa] | Sz at probe<br>[MPa] | EMC Modulus<br>[GPa] | Sz at probe<br>[MPa] |       | EMC Modulus<br>[GPa] | Sz at probe<br>[MPa] |

| 1                      | 0.5                  | 147                  | 26                   | 13                   | 10    | 51                   | 25.5                 | 22                   | 76                   | 38    | 33                   |                      |

| 2                      | 1                    | 116                  | 27                   | 13.5                 | 11    | 52                   | 26                   | 23                   | 77                   | 38.5  | 33                   |                      |

| 3                      | 1.5                  | 93                   | 28                   | 14                   | 11    | 53                   | 26.5                 | 23                   | 78                   | 39    | 33                   |                      |

| 4                      | 2                    | 76                   | 29                   | 14.5                 | 12    | 54                   | 27                   | 24                   | 79                   | 39.5  | 34                   |                      |

| 5                      | 2.5                  | 61                   | 30                   | 15                   | 12    | 55                   | 27.5                 | 24                   | 80                   | 40    | 34                   |                      |

| 6                      | 3                    | 49                   | 31                   | 15.5                 | 13    | 56                   | 28                   | 24                   | 81                   | 40.5  | 34                   |                      |

| 7                      | 3.5                  | 39                   | 32                   | 16                   | 13    | 57                   | 28.5                 | 25                   | 82                   | 41    | 35                   |                      |

| 8                      | 4                    | 30                   | 33                   | 16.5                 | 14    | 58                   | 29                   | 25                   | 83                   | 41.5  | 35                   |                      |

| 9                      | 4.5                  | 22                   | 34                   | 17                   | 14    | 59                   | 29.5                 | 26                   | 84                   | 42    | 36                   |                      |

| 10                     | 5                    | 15                   | 35                   | 17.5                 | 15    | 60                   | 30                   | 26                   | 85                   | 42.5  | 36                   |                      |

| 11                     | 5.5                  | 9                    | 36                   | 18                   | 15    | 61                   | 30.5                 | 26                   | 86                   | 43    | 36                   |                      |

| 12                     | 6                    | 4                    | 37                   | 18.5                 | 16    | 62                   | 31                   | 27                   | 87                   | 43.5  | 37                   |                      |

| 13                     | 6.5                  | 3                    | 38                   | 19                   | 16    | 63                   | 31.5                 | 27                   | 88                   | 44    | 37                   |                      |

| 14                     | 7                    | 4                    | 39                   | 19.5                 | 17    | 64                   | 32                   | 28                   | 89                   | 44.5  | 37                   |                      |

| 15                     | 7.5                  | 4                    | 40                   | 20                   | 17    | 65                   | 32.5                 | 28                   | 90                   | 45    | 38                   |                      |

| 16                     | 8                    | 5                    | 41                   | 20.5                 | 18    | 66                   | 33                   | 29                   | 91                   | 45.5  | 38                   |                      |

| 17                     | 8.5                  | 6                    | 42                   | 21                   | 18    | 67                   | 33.5                 | 29                   | 92                   | 46    | 39                   |                      |

| 18                     | 9                    | 6                    | 43                   | 21.5                 | 19    | 68                   | 34                   | 29                   | 93                   | 46.5  | 39                   |                      |

| 19                     | 9.5                  | 7                    | 44                   | 22                   | 19    | 69                   | 34.5                 | 30                   | 94                   | 47    | 39                   |                      |

| 20                     | 10                   | 7                    | 45                   | 22.5                 | 20    | 70                   | 35                   | 30                   | 95                   | 47.5  | 40                   |                      |

| 21                     | 10.5                 | 8                    | 46                   | 23                   | 20    | 71                   | 35.5                 | 31                   | 96                   | 48    | 40                   |                      |

| 22                     | 11                   | 8                    | 47                   | 23.5                 | 20    | 72                   | 36                   | 31                   | 97                   | 48.5  | 40                   |                      |

| 23                     | 11.5                 | 9                    | 48                   | 24                   | 21    | 73                   | 36.5                 | 31                   | 98                   | 49    | 41                   |                      |

| 24                     | 12                   | 9                    | 49                   | 24.5                 | 21    | 74                   | 37                   | 32                   | 99                   | 49.5  | 41                   |                      |

| 25                     | 12.5                 | 10                   | 50                   | 25                   | 22    | 75                   | 37.5                 | 32                   | 100                  | 50    | 41                   |                      |

**Table 1:** Full-factorial FEA dataset for Sz vs. EMC modulus. There are 100 training and 14 test cases in total.

They collected a dataset of 2000 stress field images, then used a U-net for the generator and PatchGAN for the discriminator. Gao, et al. [4], predicted the stress field of a crust and rock formation using several CNNs in parallel, which they claim further reduced the test error for 877 cases. Wang, et al. [3], used spatial and temporal feature propagation for stress-field prediction using TI-CNN and Bi-LSTM with 61 simulations of a time-series dataset. The above works, however, are not related to IC packages; additionally, they mainly focus on image-based stress prediction. On the other hand, unlike a dataset that contains simple structures, it is much harder to collect an IC package dataset using FEA. Few authors have addressed the issues of using an FEA dataset for stress prediction. Kang, et al. [6], mentioned using a Monte Carlo method to prepare a large dataset. However, little is discussed on preparation and an ANN approach. Instead, the authors mainly investigated layers and nodes for low error in stress prediction, as well as compared results of ANN with FEA. Nourbakhsh, et al. [7], discussed using Latin hypercube sampling [8] for collecting a design of experiment (DOE) exercise and developing surrogate models from various structures to enable a more general model prediction for the same class with different topology and boundary conditions. More recently, Chen, et al. [9], has discussed using

ANN to learn from past FEA simulations of packaged components in an effort to shorten the design cycle for IC packaged products.