# Chip Scale Review®

ChipScaleReview.com

The Future of Semiconductor Packaging

Volume 27, Number 6

November • December 2023

Automotive LiDAR: Photonics assembly requirements and trends

- Optimizing advanced IC substrates (AICS) for PLP

- Die-to-wafer hybrid bonding development for HVM

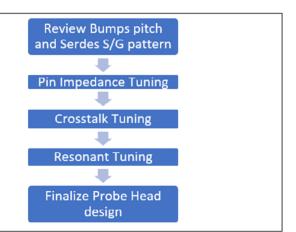

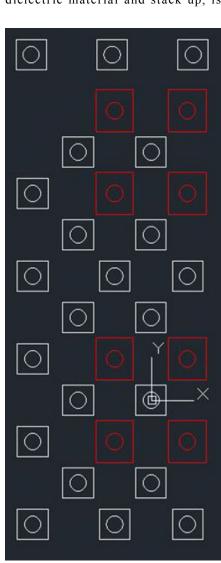

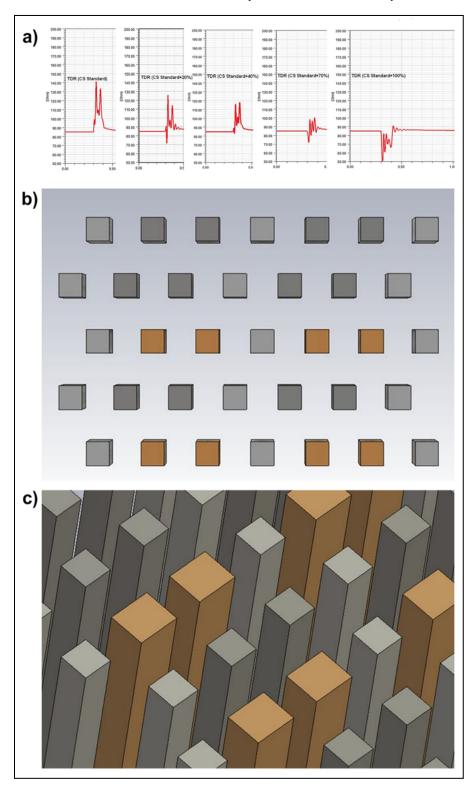

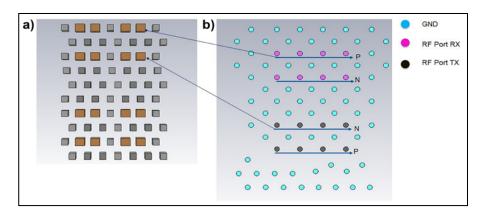

- High-speed probe card architecture for high-end devices

- Recent advances in bridges for chiplets communications

- Automotive gate driver package with galvanically-isolated communication linkage

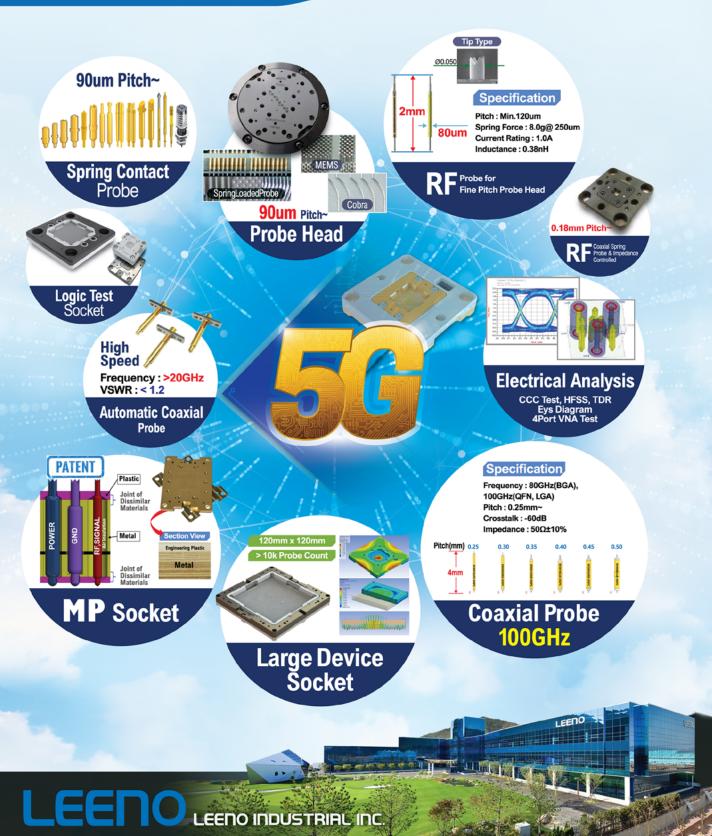

# LEENO

# Fine Pitch Probe Continuous Non-stop Innovation! & Probe Head

## **Proven Mass Production Capability**

RF-300 m Pitch

#### 974m Pitch

#### 92 µm Pitch

#### 92 µm Pitch

#### Mechanical Spec.

- Spring Force : 0.2126z (12.0g) @ .0079 (0.20nm) - Recommended Travel: .0079 (0.20mm)

- Full Travel ; .0098 (0.25mm)

- Current Rating: 2.0A

- Plunger Hardened BeCu / Au plated Spring Music Wire / Au plated

#### Electrical Spec. (Simulation data)

- Propagation Delay: 7.68ps

- Capacitance : 0.05pF Inductance : 0.25nH

- Insertion Loss : > 100GHz @ -1dB

- Return Loss: > 100GHz @ ·10dB (Dielectric material: MDS100)

#### Mechanical Spec

- Spring Force : 0.2825z (8.8g) @ .0079 (0.20nm) ommended Travel : .0079 (0.20mm)

- Full Trevel : .0098 (0.25mm)

- Material : Terminal Pd Alloy / No Plated Plunger - Pd Alloy / No Plated Barrel - Ni-Au Alloy / Au Plated Spring - Music Wire / Au Plated

#### Electrical Spec.

- Current Rating (Reference Only): 1.0A

(Resed on 20% for

- Inductance : 0.42nH

- -Insertion Loss: > 60.00GHz @ -1.000dB

- Return Loss: 59.67GHz @ -10.000dB

(Dielectric material: CERAMIC)

- Capacitance : 0.22pF

- Propagation Delay: 18.00ps

#### Mechanical Spec

- Spring Force: 0.247oz (7.0g) @ .0118 (0.30mm)

- mmended Travel: .0118 (0.30mm)

- Full Trevel : .0136 (0.35mm)

- Material : Terminal Pd Alloy / No plated Plunger - Pd Alloy / No plated Barrel - Ni-Au Alloy / Au plated Spring - Music Wire / Au plated

#### Electrical Spec.

- Current Rating (Reference Only): 1.0A

(Based on 20% force)

- Inductance : 0.67nH

- Insertion Loss : > 60.00GHz @ -1.000dB

- Return Loss: 56.03GHz @ -10.000dB

Olelectric protects: CERAMO

- Capacitance : 0.43pF • Propagation Delay: 33.90ps

#### Mechanical Spec.

- Spring Force: 0.176oz (5.0g) @ .0098 (0.25mm)

- Recommended Travel: .0098 (0.25mn)

- · Full Travel : .0118 (0,30mm)

- · Material : Terminal Pd Alloy / No plate Plunger - Pd Alloy / No pisted Barrel - Ni-Au Alloy / Au plated

#### Electrical Spec.

- Current Rating (Reference Only): 1.0A

(Based on 20% force reduction)

- Inductance : 0.81nH

0.092,0.092

- Insertion Loss: 35.66GHz @ -1.000dB

- Return Loss: 34.19GHz @ -10.000dB (Dielectric material: CERAM)

- Capacitance : 0.50pF

USA: hskang@leeno.co.kr/+14083132964/+821087376561 korea: sales-leeno@leeno.co.kr/+32517925639

#### November • December 2023 Volume 27, Number 6

Legislation to support reduction in carbon dioxide emissions is driving the growth in the electric vehicle (EV) market. LiDAR is also driving trends in automotive photonics devices. This issue features two articles that cover these important needs. MRSI (a part of Mycronic Group) discusses the photonics device assembly requirements and trends in automotive LiDAR and presents a solution for typical edge-emitting lasers and VCSEL chips. To answer the need for on-board systems such as EV traction inverters, DC/DC converters, etc., which must be connected to high-voltage power sources, NXP Semiconductors, Inc., presents a package designed for automotive high-voltage gate driver applications.

Cover image courtesy of iStock/Just\_Super

# CONTENTS

#### **FEATURE ARTICLES**

- 6 Die-to-wafer hybrid bonding development for HVM By Jonathan Abdilla [BE Semiconductor Industries N. V.] Guan Huei See [Applied Materials, Inc.]

- **14** Optimizing advanced IC substrates (AICS) for PLP By Keith Best [Onto Innovation]

- 19 Automotive gate driver package with galvanically-isolated communication linkage

By Ankur Shah, Burton Carpenter, Fred Brauchler, Di Liu, Pierre Calmes, JM Liu, Xueting Wu [NXP Semiconductors Inc.]

25 Automotive LiDAR: Photonics assembly requirements and trends

By Limin Zhou, Avy Yi [MRSI, a part of Mycronic Group]

# FUSION AND HYBRID BONDING FOR HETEROGENEOUS INTEGRATION

- Enabling advanced 3D device stacking and chiplet integration for CMOS image sensors, memory and 3D system-on-chip (SoC)

- High-volume production equipment and process technology for Wafer-to-Wafer (W2W) and Die-to-Wafer (D2W) hybrid bonding

- GEMINI® FB Automated Production Wafer Bonding System delivers industry leading alignment accuracy and bonding performance

EVG®850 NanoCleave™

Revolutionary NanoCleave™ technology enables release and transfer of ultra-thin layers with nanometer precision

**GET IN TOUCH** to discuss your manufacturing needs **www.EVGroup.com**

## Chip Scale Review

ChipScaleReview

The Future of Semiconductor Packaging

#### STAFF

#### **Kim Newman**

Publisher

knewman@chipscalereview.com

#### **Lawrence Michaels**

Managing Director/Editor

Imichaels@chipscalereview.com

#### **Debra Vogler**

Senior Technical Editor dvogler@chipscalereview.com

#### SUBSCRIPTION-INQUIRIES

Chip Scale Review

All subscription changes, additions, deletions to any and all subscriptions should be made by email only to subs@chipscalereview.com

Advertising Production Inquiries: Lawrence Michaels

Imichaels@chipscalereview.com

Copyright © 2023 Haley Publishing Inc.

Chip Scale Review (ISSN 1526-1344) is a registered trademark of Haley Publishing Inc. All rights reserved.

Subscriptions in the U.S. are available without charge to qualified individuals in the electronics industry.

Chip Scale Review, (ISSN 1526-1344), is published six times a year with issues in January-February, March-April, May-June, July-August, September-October and November-December.

P.O. Box 2165 Morgan Hill, CA 95038 Tel: +1-408-846-8580

E-Mail: subs@chipscalereview.com

Printed in the United States

Volume 27, Number 6 November • December 2023

#### FEATURE ARTICLES (continued)

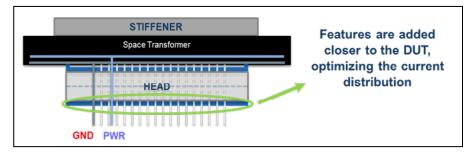

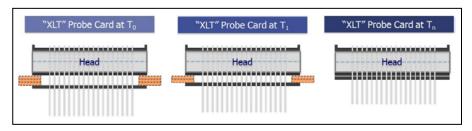

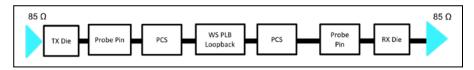

- High-speed probe card architecture for high-end devices

By Xin-Reng Foo, Chee Hoe Lin [AMD Singapore]

Alberto Berizzi [TECHNOPROBE Italy]

- Recent advances in bridges for chiplets communications

By John H. Lau [Unimicron Technology Corporation]

#### **DEPARTMENTS**

#### **INDUSTRY EVENTS**

47 IMAPS Symposium 2023

By Suresh Jayaraman [General Chair of IMAPS Symposium, 2023, and Amkor]

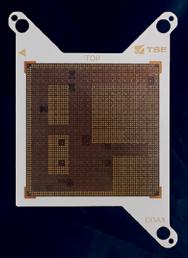

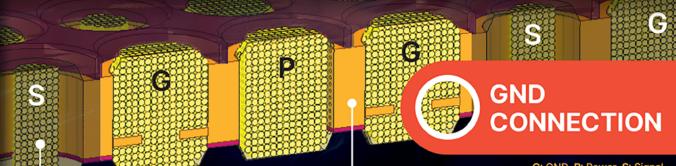

# COAXIAL **ELASTOMER SOCKET**

for >64Gbps ATE/SLT Test for Crosstalk free Board to Board Connector

Semiconductor Package Test

**Board to Board** Interconnection

# ELTUNE-coax

**Metal GND Structure** Extremely Low Crosstalk >100Ghz@-20dB Inductance < 0.1nH Min. pitch 0.6mm

Elastomer + Conductive Ni Particles **GND Shielding** by Metal housing G: GND P: Power S: Signal

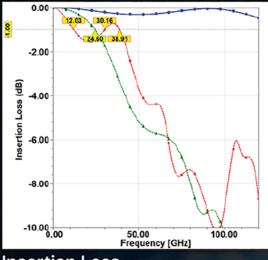

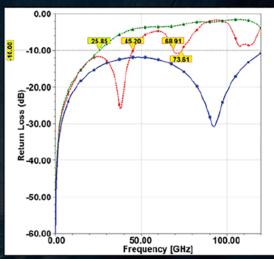

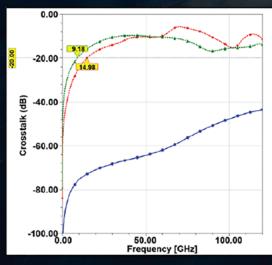

| Electrical Specifications (unit: GHz)                       |       |       |      |  |  |  |

|-------------------------------------------------------------|-------|-------|------|--|--|--|

| 50Ω, 0.80mm pitch Spring pin Elastomer <i>ELTUNE-coax</i> ™ |       |       |      |  |  |  |

| Electrical Length(mm)                                       | 3.05  | 0.60  | 0.60 |  |  |  |

| Insertion Loss(S21) @-1dB                                   | 12.03 | 24.60 | >100 |  |  |  |

| Return Loss (S11) @-10dB                                    | 45.20 | 25.85 | >100 |  |  |  |

| Crosstalk (S31) @-20dB                                      | 14.98 | 9.18  | >100 |  |  |  |

#### **Insertion Loss**

#### **Return Loss**

#### **TSE USA**

Jong M. Lee jmlee@tse21.com Kevin Kim kevin.kim@tse21.com

#### TSE HQ

Justin Yun justice@tse21.com Jimmy Hwang jimmyhwang@tse21.com

- ELTUNE-CORN "

- Elastomer

- Spring Pin

Crosstalk

## Die-to-wafer hybrid bonding development for HVM

By Jonathan Abdilla [BE Semiconductor Industries N. V.], Guan Huei See [Applied Materials, Inc.]

his article addresses the key requirements for a successful die-to-wafer (D2W) hybrid bonding process. The selected process steps from bonding pad formation to grind and singulation, as well as an integrated D2W bonding process will be addressed, providing key technical values for the various steps involved. The integrated bonding processes include wet cleaning, degassing and plasma surface treatment. Successful Cu-Cu diffusion through grain growth across the boundary interface will show the efficacy of such a tool, C-mode scanning acoustic microscopy (C-SAM) results will address the topic of voids, and electrical yield results will also be presented. Actual placement accuracy results will also be shared for both collective and direct D2W hybrid bonding.

#### Introduction

The adoption of 3D architectures in advanced packaging between chips is driven by high-performance computing (HPC) and artificial intelligence (AI) requirements [1, 2]. Flip chip has been the main technology of forming the die attachment in packaging. It requires a copper (Cu) pillar made out of a metal alloy, namely copper-nickel-tin-silver (Cu-Ni-Sn-Ag) that occupies an opening with a critical dimension (CD) of 20-40µm on a passivation polymer dielectric (e.g., polymide or polybenzoxazole [PBO]) for each of the contact points. Such a thickness is needed to allow underfill material to flow reliably and to act as a stress buffer for mechanical integrity. The flip-chip attach is done through thermal compression bonding (TCB) where at least one of the dies or substrates is heated to ensure that the Cu bump reaches the eutectic state so that Sn-Ag can form a good electrical contact. With this bonding technique, some amount of inter-metallic compound that is causing higher resistivity and weaker reliability is inevitably generated.

The migration toward Cu hybrid bonding (HB) will only require the use of standard

back end of line (BEOL) inorganic dielectric and Cu, and is expected to improve over the issues noted above, as well as adding other benefits. Overall, the preparation needs for die bonding are simplified, Cu bump and underfill processes are removed, and TCB is replaced with room temperature HB. This directly translates into reduction of vertical form factor and scaling to higher input/ output (I/O) density, thereby leveraging the mature BEOL that scaled well below the submicron range. The change of pad material from a complex alloy (Cu-Ni-Sn-Ag) to pure Cu and the direct connection through HB at room temperature are expected to offer shorter interconnect lengths, lower resistance and improvement in thermal diffusion. As a result, an increase in system-level performance with better bandwidth and/or speed can be expected.

HB is achieved as a two-step process: first, by leveraging on the initial forces of surface interaction at atomic proximity of the dielectric-dielectric interface to form the "tacking," which is the initiation of the bonding, and finally, following up with a fusion process by annealing at an elevated temperature (100°C-400°C) to form both stronger dielectric-dielectric covalent bonds

with the release of excessive water ( $\rm H_2O$ ) molecules, as well as metal-metal diffusion that will enable the electrical connection. A successful bond can be achieved with careful surface engineering of the dielectric, typically with dielectric surface roughness values of <0.4nm [3]. Of the two HB flavors, wafer-to-wafer (W2W) or D2W, the latter enables higher system-level yield thanks to use of known-good-dies only. This paper describes the necessary conditions to achieve a successful D2W HB suitable for high-volume manufacturing (HVM) production.

## PVD-CMP co-optimization for D2W HB

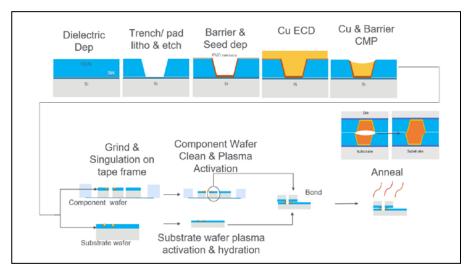

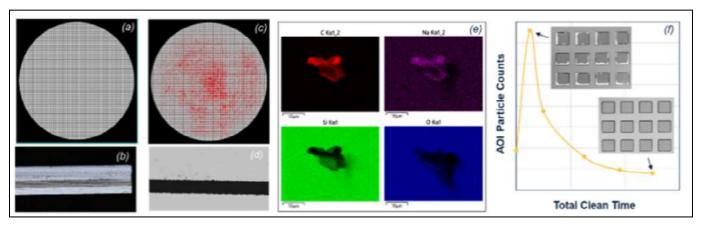

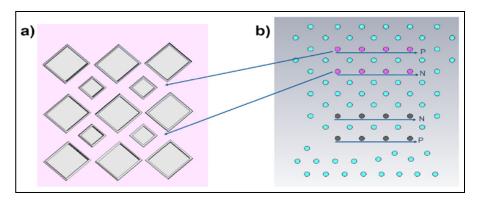

As elegant as it looks, HB also has many challenges. The bonding requirements that work for W2W HB, e.g., the Cu chemical mechanical polishing (CMP) process that ensures good roughness (<0.4nm), dishing (<5nm) and erosion, are not directly transferable to D2W. A D2W test vehicle and bonding flow was developed based on the illustration of the key process sequence shown in **Figure 1**. Previous work done on W2W test vehicles successfully demonstrated thick barrier and

Figure 1: Selected process steps from bonding pad formation to grind and singulation.

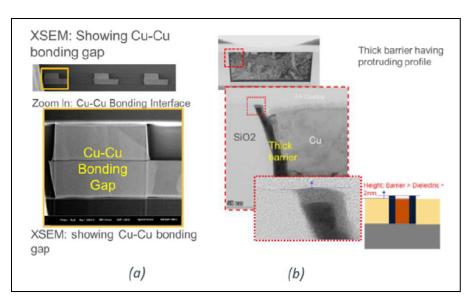

Figure 2: a) A PVD thick barrier-CMP interaction with zoom in focus and an illustration of barrier protrusion, which resulted in b) a Cu-Cu bonding gap due to barrier-CMP interaction (see the XSEM).

CMP optimization [4]. However, when the same process was applied to D2W HB, it resulted in a visible Cu-Cu gap from X-ray secondary emission microscopy (XSEM) analysis as shown in Figure 2a due to insufficient force (weight) to form good tacking (i.e., low force was used to bond the samples compared to the forces used in W2W bonding) as a result of thinning and dice. The failure analysis of a cross section with transmission electron microscopy (TEM) at the edge of the Cu bond pad (Figure 2b), indicated the barrier was higher than the dielectric by 1-2nm. One hypothesis suggested that this barrier protrusion was standing out from the rest of the dielectric at the corner of the bonding

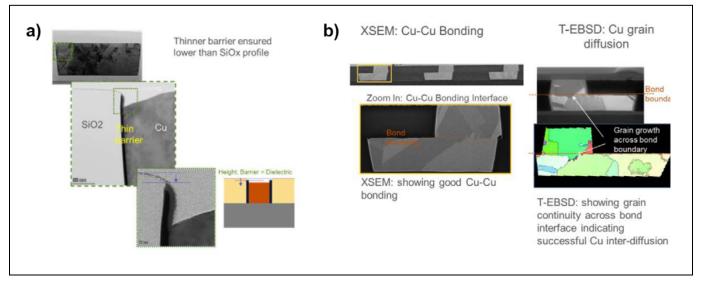

pads, and in addition to the already reduced force acting on the bond interfaces from grinded and singulated die, was preventing the "tacking" of dielectric-dielectric during die placement. At post-bond anneal, the protruded barrier has higher thermal expansion than the oxide (Ta: 6.5 10<sup>-6</sup>/K vs.  $SiO_2$ : 0.65  $10^{-6}/K$  [5]) and therefore was expanding faster, pushing the two bond interfaces apart and preventing the Cu pads from making contact and diffusing (or inter-diffusing), giving rise to a wider gap (20~40nm) than initial dishing. The physical vapor deposition (PVD) barrier-CMP process was optimized by using a thin barrier and a tuned CMP process to ensure that oxide was always higher than the barrier as shown in **Figure 3a**, while keeping the roughness, Cu dishing and erosion within the D2W bonding process requirements. The same bonding and annealing was repeated. The results showed that the Cu-Cu bond was fused, and was further validated with transmission electron-back-scatter-diffraction (T-EBSD) portraying a successful Cu diffusion across the bonding boundary (**Figure 3b**).

# Surface activation, cleanliness, queue time and electrical yield

Once the interfaces were optimized as discussed in the section on PVD-CMP co-optimization, we moved on to study dielectric surface activation, the impact of a particle-free surface and queue time. These requirements are more stringent for D2W HB than for W2W HB because of the need to process dicing and singulated dies on flexible organic tape or on carrier wafers with organic adhesive.

Plasma activation has been demonstrated to increase hydrophilicity for dielectrics such as SiO<sub>2</sub> and SiCN [6]. Hydrophilicity is achieved by the presence of the silanol groups (Si-O-H) on the dielectric surfaces. Ion energy is one way to promote the silanol groups' attachment to the dielectric surface by creating disorders and highenergy states on the surfaces. The presence of these silanol groups is essential, as they enable initial bonding when dielectric surfaces from substrates and chiplets are brought together even at room temperature. The measurement of the hydrophilicity of dielectric surfaces is a way to evaluate the effectiveness of the activation

Figure 3: a) An optimized thin PVD-CMP, with zoom in focus and an illustration of higher dielectric than barrier in nm-scale, which resulted in a Cu-Cu diffusion (see the XSEM) and confirmation with T-EBSD showing grain growth across the bond boundary.

**Figure 4:** Plot showing the plasma activation effect on the initial contact angle on an  $SiO_2$  surface and the queue time effect on the contact angle and bonding performance after activation. Bonding degrades with excessive queue time between activation and bonding as shown in the C-SAM images of the delamination around the die edges.

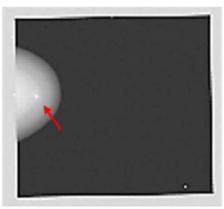

process. Macroscopic observations of the hydrophilicity of the SiO<sub>2</sub> surface are seen with water contact angle measurements. When the SiO<sub>2</sub> dielectric surfaces are treated with the right plasma conditions, superhydrophilicity with a contact angle of <5° can be achieved (Figure 4). It is also shown that the contact angle degrades over time if the wafers are exposed to air after activation. The degradation or the hydrophilicity leads to poor bonding performance, as shown in delamination at the die edges from C-SAM analysis (see insets of Figure 4). Therefore, controlling the queue time between activation and bonding is crucial to achieving the best bonding performance.

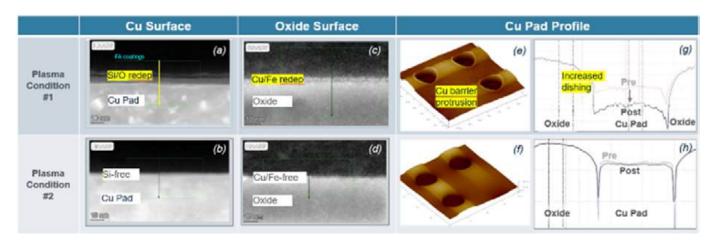

Proper selection of plasma conditions, including ion energy, density, and

chemistry is essential for sufficient activation without causing physical or chemical damage to other materials, such as Cu and plastic tapes. As shown in Figure 5, when the ion energy is too high, the dielectric surfaces are roughened, which creates voids and diminishes the bonding performance. In addition, the sputtered materials from the dielectric surface and organic adhesive can further redeposit on the die surface under strong plasma conditions. The redeposition creates an undesired Cu diffusion barrier during the post-bonding annealing stage. Therefore, it is important to optimize the plasma activation conditions to achieve surface roughness of <0.5nm and etching of SiO<sub>2</sub> of <1nm while preserving the Cu dishing profile and ensuring the surface is free of organic residue and without excessive oxidation (Figure 5e-h).

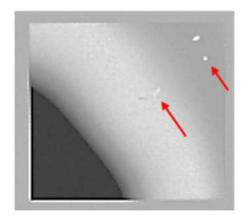

Cleanliness is paramount to the performance of the HB. Any particle on the bonding surface can lead to poor adhesion, weak bonds, or complete failure of the bond (**Figure 6**). To ensure the best bonding performance, free particle control is a high priority for any pre-treatment system design. Particles should be controlled to meet the device specification in the activation chambers. In addition, a highly efficient wet clean process is essential to ensure the cleanliness before the wafer and the component dies enter the bonders. Efficient cleaning is particularly challenging for diced wafers on flexible tapes because the dicing processes could introduce additional particles or/and contaminants. Insufficient post-dicing cleaning could leave particles on the tape or die sidewalls (Figure 7a-b). In some cases, further cleaning, if not done correctly, can create more particles when stirred up from the tape or die sidewalls and land on die surfaces, causing delamination near die edges (Figure 7c-f).

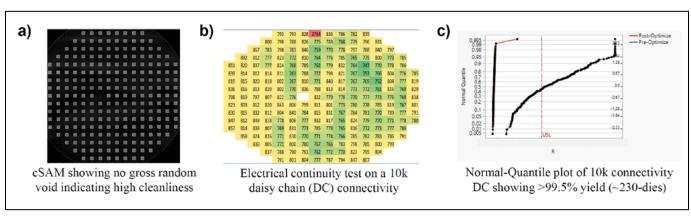

After the whole integration, bonding process optimization and alignment were done, a 300mm substrate wafer was bonded (~230 dies) to validate the bonding performance. Figure 8a shows the post-bond C-mode scanning electron microscopy (C-SAM) result where no gross random void was observed, indicating high cleanliness efficiency. This is further confirmed with an electrical continuity test on a 10,000-daisy chain (DC) connectivity occupying an area of 1mm x 1mm (of a 6mm x 6mm die size) shown in the Figure 8b wafer contour plot and in the

Figure 5: Surface and topography comparison between strong and soft plasma-treated patterned samples: a–d) TEM cross-sectional study of the Cu pad and dielectric oxide surface, revealing surface contamination from redeposition caused by a strong plasma; e–h) Atomic force microscope measurements showing that a strong plasma alters Cu pad profile, and an increased dishing amount.

# Global No.1 Total Test Solution Provider ISC

# System Package Test Solution iSC-WiDER

- Up to 350um warpage can be covered

- Improved socket structure allowed 30% lower force

- Stroke increased by 50% to accommodate larger device size over 100x100

Figure 6: SAM images of defective bonding (delamination and voiding) caused by surface particles.

**Figure 7:** Automatic optical inspection (AOI) of the a) surface and b) sidewall of singulated dies of a tape-frame wafer after thinning and the saw-dicing process. A large number of particles (black) can be seen adhering to the sidewall. c-d) An incorrect further cleaning detaches and redeposits the particles onto the die surface. c-e) The organic nature of the particles revealed by energy-dispersive X-ray spectroscopy inspection suggests tape adhesive as the origin. If not properly removed, f) these particles can cause die delamination after bonding, as seen under SAM inspection.

normal quantile plot in **Figure 8c**, which shows a >99.5% continuity electrical test yield (a significant improvement from pre-optimization data). The process improvement was reflected in overall mean resistance and variability.

The same test vehicle was further used to characterize the process-induced possible

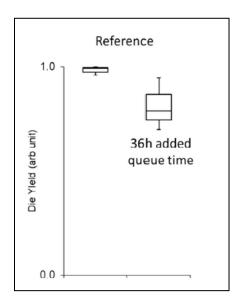

yield impact of queue time between the various process steps, as batch-mode processing makes it difficult to control queue time. Samples were processed with a 36-hour queue time and compared with the baseline; in the high-volume production case, one could expect a queue time of 1 to 2 days, and not just time, but also its

variance increases with a more complex bonding configuration, where >3-5 different chiplets are in the roadmap to be bonded to the same substrate. Three bonded wafers from the "delayed" lot were compared to the baseline in **Figure 9**. Adding queue time leads to significantly lower yield (80%) vs. the reference case (98%).

Figure 8: Post optimization: a) CSAM result showing void-free bonding, b) a wafer contour plot of 10,000-connectivity daisy-chains resistance, and c) Normal-quantile plot of 10,000 connectivity DC showing >99.5% yield (~230-dies)—a significant improvement from pre-process optimization.

#### Die placement accuracy

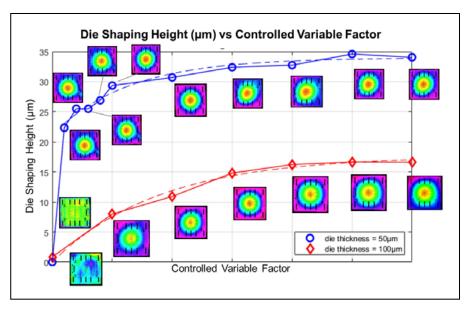

Two bonding process cornerstones include bond force control and bond front propagation, of which the latter can be controlled through several options—with die shaping being preferred. The die shaping is responsible for creating a controlled bond front, ensuring no void entrapment, and avoiding ablation generated from the high-speed die bond to substrate wafer. Bond force, in turn, can impact initial bond strength from dielectric fusion as well as damage to the die if force is not controlled or not optimized.

Our approach to die shaping and bond front propagation is to have a single point of initial contact between die and substrate wafer, which is at the center of the die. This approach ensures two things: first, the initial contact causes instant bonding through Van der Waals's forces, thereby locking the die laterally and rotationally and minimizing placement accuracy loss from possible mechanical influences. Second, this allows the air between die and substrate wafer to be expelled symmetrically outwards as the die is flattened, thereby ensuring equal conditions on all sides of the die as well as minimizing risks of void entrapment. Figure 10 shows the shape of the same die at different values of the variable-controlled factor for a 7x7mm die at thicknesses of 50μm and 100μm. The inner orange circle delineates that the die is at its highest warpage level taking on a convex shape. The graph shows that for the thinner 50µm die, the change in shape occurs at a much lower value for the controlled variable factor

**Figure 9:** Plot showing the effect of added queue time on bonding yield.

**Figure 10:** Die shaping height of die in  $\mu$ m vs. variation in the controllable factor for a 50 $\mu$ m (blue) and 100 $\mu$ m (red) thick die.

and that the maximum height is also higher. For the 100µm example, the die shows no deformation for the first four values of the controlled-variable factor. The maximum height is lower than the 50µm thick die, but both exhibit a similar behavior whereby the maximum die shape height flattens out. At all stages following the initial conditions however, the first point of contact is always in the center of the die.

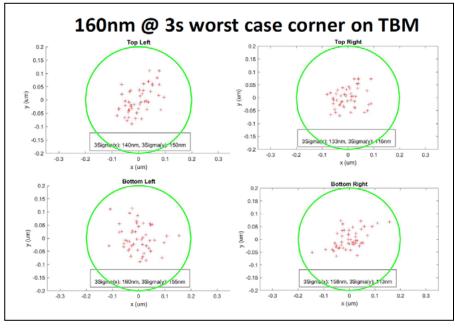

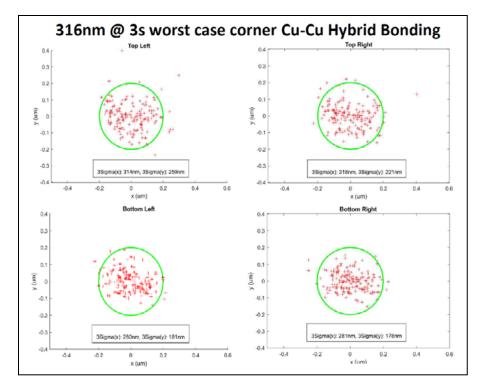

Two scenarios were explored to estimate bonding precision. The first scenario is bonding on a substrate wafer coated with a temporary bonding material (TBM) layer. The second scenario consists of direct, or fusion, bonding. The first scenario uses a process that does not rely on plasma activation because the bonding mechanism is not through instantaneous fusion by way of Van der Waal's forces, but through the temporary bonding material adhesive. However, this process is reliant on the TBM's properties of bonding reaction times, elasticity and viscosity among others, all of which have an impact on final accuracy. The process was carried out with ~7x7mm dies analyzed using infrared (IR) microscopy. The results are shown in Figure 11 and

Figure 11: IR overlay for die placement on a wafer with a TBM layer.

# adeia

# Adeia turns ideas into innovations

Our name may be new, but our roots run deep with decades of continued innovation. We invent, develop and license innovations that advance how we live, work and play.

Adeia invented and pioneered Direct and Hybrid Bonding

DBI® Ultra

Die-to-Wafer Hybrid Bonding **DBI**®

Wafer-to-Wafer Hybrid Bonding **ZiBond®**

Wafer-to-Wafer Direct Bonding

Better Ideas. Better Entertainment.

Figure 12: IR overlay for die placement on a wafer with direct bonding including a copper pad.

indicate that actual bond placement accuracy is an impressive 160nm @ ±3s for worst corner, which is currently one of the best die-to-wafer (D2W) accuracies. The green circle represents a ±200nm circle.

For the second scenario, the wafers were subjected to wet cleaning and plasma, as delineated in **Figure 1**. The dies in question were ~6x6mm. **Figure 12** shows placement accuracy results of 316nm @ ±3s for worst corner. The main factor for the gap in accuracy is that direct bonding is more prone to impact from customer material than any other bonding mechanism such as mentioned in the first part of this article due to its complexity and stringent requirements. Notwithstanding, 316nm @ ±3s for worst corner is still a very good result for a lab test vehicle and further

trials with optimizations are planned in the future. The data shown in **Figure 12** was collected with an inline metrology system with feedback control capability.

#### **Summary**

A working process flow for D2W HB has been presented. Positive outcomes of an HVM-capable process heavily depend on the co-optimization of many pieces of a complex technical jigsaw. The bonding dielectric needs to be controlled in terms of surface roughness, and needs to be properly activated with plasma. Such plasma should not lead to damage to the dielectric, nor to the metal pads, which, in turn need to be controlled not just in terms of dishing, but also with regard to unwanted protrusions from the Ta barrier.

The importance of cleanliness was clearly stated and demonstrated via studies showing void formations arising from particle entrapment. The bonding process itself was accomplished with advanced dynamic die-shaping capabilities, state of the art alignment (162nm @ 30), and using inline control capability. Finally, control of the queue time along the whole process is critical to guarantee optimal yield.

#### **Acknowledgments**

Portions of this article were presented at the IMAPS Device Conference 2023. Additional co-authors are: Ying Wang, Raymond Hung, Yauloong RuiPing Wang, Arvind Sundarrajan of Applied Materials, Inc., Hybrid Bonding Centre of Excellence; and Stefan Schmid, Benedikt Auer, Djuro Bikaljevic, PC Koay, Nithyananda Hegde, and Chris Scanlan of BE Semiconductor Industries N.V.

#### References

- 1. W. L. I. C. C. a. C. H. Chiu, "Low-temperature wafer-to-wafer hybrid bonding by nanocrystalline copper," IEEE 72nd Elec. Comp. and Tech. Conf. (ECTC), 2022.

- 2. R. Agarwal, et al., "3D packaging for heterogeneous integration," 72nd ECTC, 2022.

- 3. S. Sitaraman, et al., "A holistic development framework for hybrid bonding," 72nd ECTC 2022.

- 4. V. Chidambaram, et al., "Dielectric materials characterization for hybrid bonding," IEEE 71st ECTC, San Diego, CA, USA, 2021.

- 5. "https://www.azom.com/properties. aspx?ArticleID=1114," [Online].

- 6. S. Son, et al., "Characteristics of plasma-activated dielectric film surfaces for direct wafer bonding," IEEE 70th ECTC, 2020.

#### **Biographies**

Jonathan Abdilla is Director of Technical Marketing at BE Semiconductor Industries (BESI) N. V., Austria. He has 17 years of packaging experience in the semiconductor industry. Before joining BESI, he worked for STMicroelectronics. He has participated in several EU-funded projects and resides on several technical committees for semiconductor packaging conferences. He has a degree in Mechanical Engineering and an Executive MBA from the U. of Malta and a diploma in Computing Information Systems from the U. of London. Email jonathan.abdilla@besi.com

Guan Huei See is Director of Packaging Process Integration at the Hybrid Bonding Centre of Excellence at Applied Materials Singapore Technologies Pte Ltd. He spent the last 8 years enabling advanced packaging process integration solutions, where hybrid bonding (HB) is the most essential. This role requires him to generate and identify the necessary conditions to achieve successful C2W HB and readiness for high-volume manufacturing production.

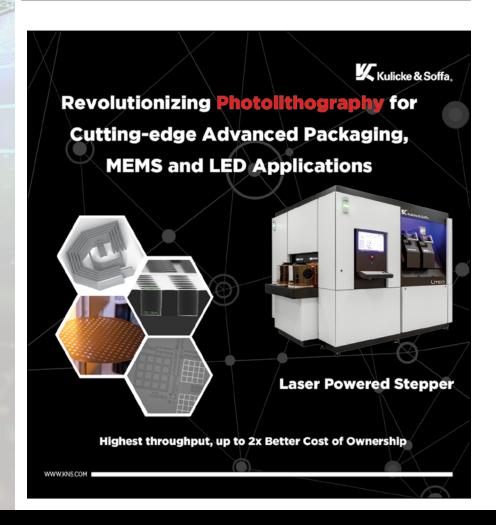

# Optimizing advanced IC substrates (AICS) for PLP

By Keith Best [Onto Innovation]

aster data transfer, greater heat dissipation, less power consumption and increased functionality are all qualities that chipmakers and their customers want from their devices. Since the dawn of the semiconductor industry, the pursuit of increasingly advanced nodes has served as the industry's North Star. But for today's voyagers, rough seas are ahead: these nodes have decreased in size, input/output (I/O) bumps on the chip have grown smaller—and with the shrinking of these bumps, their ability to mate directly to printed circuit boards (PCB) diminishes. The way to avoid this is to use advanced IC substrate (AICS), i.e., an intermediary substrate that enables progress in panel-level packaging (PLP) and chiplets.

Chiplets are a type of advanced packaging in which multiple die—such as memory, analog and other devices—are assembled in a single, large package along with a central processing unit (CPU) or graphics processing unit (GPU). With AICS, all of these chiplets can be co-packaged together in packages that may be as large as 120mm x 120mm each, which is a considerable increase from the 10mm x 10mm-sized packages

of fan-out panel-level packaging (FOPLP). These large packages allow multiple die with smaller interconnects to be assembled and then redirected to larger contact bumps compatible with a PCB. None of this means the industry has left the pursuit of next-generation advanced nodes behind, or smaller packages for that matter.

Although the semiconductor industry has turned to chiplets and other advances to meet various nextlevel performance needs and spur new innovations, advanced nodes remain key areas of development and advancement. But this move toward extra-large AICS packages signals the need for large exposure field, fine-resolution panel-level lithography systems that can expose entire panels using fewer exposures. The journey to a new era of chiplets and PLP, however, is fraught with challenges that must be overcome. including total overlay shift, yield loss and copper-clad laminate (CCL) substrate distortion. In this article, we will focus on these three challenges to the rapidly growing AICS market and outline several solutions that we have determined will enable manufacturers to address them.

#### **Total overlay drift**

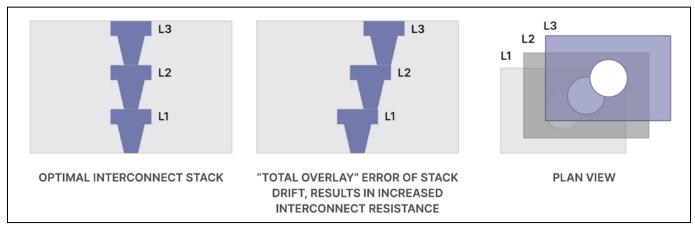

The AICS substrate that enables PLP and the segments it serves (e.g., the emerging industry star artificial intelligence [AI]) features up to 24 redistribution layers (RDL) split between the frontside and backside of the substrate. While having such a large number of RDLs improves the package's I/O count and functionality, these improvements are not without their complications. For example, as the number of RDL layers increases, minimizing overlay errors becomes increasingly burdensome. Furthermore, the trouble with overlay errors is not merely a layer-to-layer issue. Total overlay drift—the compounded drift of all RDLs in an AICS—is a challenge that advanced packaging manufacturers will need to address. But first we need to discuss how RDL processing affects the substrate.

During the AICS process flow, the buildup film between the RDLs is cured after each laser-drilled via layer. This continuous thermal cycling of the CCL substrate has the potential to distort the substrate in each quadrant of the panel. The result is that each quadrant could have vastly different overlay results.

Figure 1: A visual explanation of total overlay drift.

And in the case of extremely large exposure field (e.g., 250mm x 250mm) lithography systems, these differences in overlay create a major yield challenge, especially for high-volume manufacturing.

First, let's define total overlay. Total overlay is the summation of the overlay errors for all RDL layers, with respect to the bookending final layers on either side of the panel (Figure 1). Cumulative overlay drift from individual RDL buildup layers can significantly increase overall trace length. This may result in higher interconnect resistance, parasitic effects and poor performance for high-speed and high-frequency applications.

As each RDL is added to the film stack, layer-to-layer overlay data needs to be continuously monitored. If the total overlay error exceeds specifications at any point, and at any location on the panel, corrective action must be taken to mitigate total overlay drift or else the design resistance specifications for a package may be exceeded.

You can think about total overlay like this: if the overlay drifts  $5\mu m$  per layer, and there are 10 layers, the total RDL length will increase by  $45\mu m$ . This problem is exacerbated as the number of layers increases, i.e., in a 24-layer RDL stack, the interconnect length would increase by  $115\mu m$ .

To address the total overlay challenge, manufacturers should employ an overlay tracking system, one that incorporates metrology, lithography and analytics that records measurements for every RDL-to-via overlay across the entire panel and sums the vectors, from layer to layer, as the process stack grows. With such a system, the manufacturing team could use inspection and data analytics to track and compensate for multi-layer overlay drift. The tracking system would generate an error signal when cumulative overlay error exceeds thresholds, and the required overlay correction offsets would then be calculated and sent to the lithography system. Without a suitable tracking system in place, manufacturers have no way of knowing if RDL resistance meets specification until final electrical test (e-test). By that point, resources, time and money will have been wasted.

#### **Yield challenges**

Now that we've discussed total overlay drift, let's explore AICS package yield and its importance in fostering a cost-effective, high-throughput process. As previously mentioned, AICS have relatively few packages per panel. For example, a 510mm x 515mm AICS panel can only accommodate 16 packages (120mm x 120mm) compared to FOPLP, which could have over 2,300 packages. That's a significant difference. One defective package on an AICS could result in a 6.25% yield loss, whereas with FOPLP, one defective package may only represent a 0.04% yield loss.

To make matters even more complicated, the yield challenge is exacerbated because as the AICS package size increases to 150mm x 150mm, a single defective package failure results in an 11% yield loss, which is a significant decrease in an industry that operates under extremely narrow margins. In addition, the requirement to process both the frontside and backside of the AICS offers another risk: surface contamination leading to defects that result in yield loss.

It takes a few weeks to complete the processing of an AICS. Only by knowing the yield of an entire fab's AICS inventory, in real time, will productivity be evaluated accurately. Furthermore, panel yield needs to be assessed in terms of

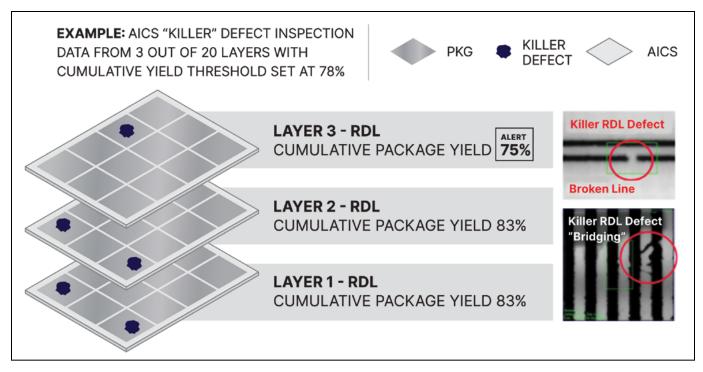

Figure 2: The effect of defects on cumulative package yield.

cost at each process step. The AICS process is a die-last process, so the panel is not of high value until the die are placed at the very end of the build. Knowing when to scrap, restart or continue to process low-yielding AICS becomes a business decision, one that relies heavily on accurate yield data. Of course, the yield loss needs to be investigated and root causes identified as soon as defects, both potential and actual, arise. With this in mind, if the manufacturing team learns that the panel at layer five in the process has a yield of 50% and it's a 40-layer process, is it worth processing the panel further? Should the panel be scrapped and restarted? The likely answer is, yes (Figure 2).

This is where the use of advanced automatic defect classification (ADC) and yield analytics are imperative for a quick and successful recovery. To track the panel yield, a comprehensive and intelligent yield-tracking database, with access to inspection data for each panel at each process step, is needed. In addition, the inspection data requires an ADC system trained to identify killer defects. These killer defects—such as RDL opens, RDL shorts, missing vias and via residue—must be classified with 100% accuracy, so that each defective package on the panel can be identified

with confidence. However, some defects may not be apparent until later in the process. For instance, a large particle embedded in the build-up film may not impact the current via layer, but a later RDL pattern that is located on top of the particle could induce RDL bridging due to the particle creating an out-of-focus lithography condition.

As the industry transitions to glass core substrates that may allow for single-side processing, future AICS processes may become more robust. However, package sizes will continue to grow, and RDLs will continue to shrink below a line/space of 5µm. This is a problem for the build-up film because it is not capable of supporting laser-drilled vias less than 10µm. In other words, the technology roadmap will require new photoresist and photo-imageable dielectric processes.

#### **Copper-clad laminate distortion**

Now that total overlay and yield loss in AICS have been discussed, let's move on to a discussion about how CCL processing leads to panel distortion and how overlay correction solutions compensate for this. To start with, let's talk about the curing of buildup film. CCL substrate processing requires the curing of buildup film. During this process, the CCL substrate is subjected to repeated thermal cycling, resulting in

the distortion of the X and Y coordinates of the interconnect patterns. This distortion impacts the registration of the laser-drilled vias to the lithography-printed RDL.

Here's where the CCL process gets challenging: RDL design typically includes a large landing pad at the end of each interconnecting line/space (1/s) that connects to the vias. The landing pad is significantly larger than the critical dimension of the RDL. By including this feature, the overlay tolerance is increased significantly. For example, if the diameter of the laserdrilled via hole is 30µm, the RDL landing pad could be 50µm to provide an overlay tolerance of +/-10µm. With the interconnect technology roadmap approaching a point of inflection—from 12µm/9µm l/s to below 5μm/5μm l/s—it becomes increasingly difficult for advanced packaging designers to meet this challenge because the large landing pads limit design space. This results in the need to increase the number of RDL layers, along with an increase in cost and potential yield loss. To mitigate this design quandary, smaller RDL landing pads are required, but this can only be achieved if process overlay is improved. With improved overlay performance, RDL and via structures with smaller landing pads can be squeezed into a smaller area, eliminating the need for additional RDL layers. Moreover, this reduces the cost and yield loss risk—i.e., fewer layers mean fewer worries.

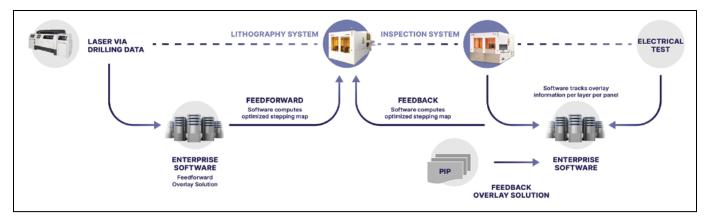

Figure 3: Overlay solution for AICS panels.

To improve process overlay, the lithography system, or stepper, must analyze and compensate for CCL substrate distortion errors. While this sounds simple in principle, the CCL distortion components are complex and extend beyond the traditional six-parameter model supported by most lithography steppers. This nonlinear distortion requires additional higher order lithography system corrections, thereby increasing the complexity of the model.

The stepper's ability to correct for the substrate distortion is only part of the solution. We also need accurate metrology data to generate optimum alignment solutions to compensate for distortion errors. Typically, this data is only available after the lithography process is finished and overlay of the vias to the RDL landing pad is measured. The data is then analyzed and sent back to the stepper to correct panel distortion for future incoming panels (a.k.a. feedback corrections). However, the feedback corrections are only relevant if the panel distortion remains constant for incoming future panels. Sampling plans and periodic metrology can help generate a run-to-run solution. These steps, together with artificial intelligence (AI) and machine-learning software, can correct the dynamic distortion errors exhibited by CCL substrates over time.

An alternative approach could be to gather metrology data from the substrates after the laser-drilled vias have been created and before the stepper is involved. These are known as feedforward corrections. Feedforward metrology requires a leap of faith, however, because it depends on a laser-drilling tool and stepper working in concert to produce an accurate and reliable dataset to create the stepper alignment solution (Figure 3).

In principle, the ideal solution to solve the overlay problem would be to use a feedforward approach where X and Y coordinate data from the laser-drilled via holes are employed to generate an alignment solution. The overlay metrology data will confirm if the feedforward correction is accurate and will highlight the residual errors. If the residual errors are significant, the feedforward model likely needs to be adjusted. Ironically, post-exposure, final overlay metrology could be used to optimize the feedforward model. With machine learning and continued iterations, the model could be continuously adjusted to achieve good overlay with low residuals.

The manufacturing of large packages requiring the heterogeneous integration of chiplets, high-bandwidth memory (HBM) and GPU/CPU is only achievable using AICS processing. To deliver this capability, substrate distortion needs to be characterized and compensation provided in order to maintain high yields and reduce

costs. A comprehensive metrology and lithography solution is required. This solution should be used in conjunction with advanced software that can automatically adjust models to compensate for the dynamic substrate distortion components. This approach could extend the roadmap of CCL substrate manufacturing beyond its current design limits, thereby reducing costs and improving yields.

#### Summary

With the AICS market forecast to reach nearly \$25 billion in 2027, according to Yole Group, there is little doubt that AICS will be one of the chief drivers of innovation. However, AICS brings with it significant challenges, like total overlay shifts, yield loss and CCL substrate distortion. And with the number of RDLs soaring to 24 with AICS, any unaddressed errors in any single layer can ruin a substrate that otherwise would have been used in a PLP. However, by applying the techniques in this article, manufacturing teams can improve yield and throughput and reduce costs in this emerging PLP segment of the semiconductor industry, guiding manufacturers away from turbulent waters and steering their ships toward smoother seas.

#### **Biography**

Keith Best is the Director of Product Marketing, Lithography, at Onto Innovation, Wilmington, MA. For more than 35 years he has held a range of semiconductor processing and applications positions for both device manufacturing and capital equipment companies. He also has numerous publications and holds 22 US patents in the areas of photolithography and process integration. Email keith.Best@ontoinnovation.com

## Capable of producing probes with 75um outer diameter

# **Spring Probe**

Customized design and manufacturing spring probe capability are available for different applications, we provide the most fitting materials, coatings, and probe structures for your ever changing IC packages and testing conditions.

Simulation

To attical action at the case of the case

Customizable plunger

Ensuring probe performance and quality by simulation

#### Manufacturing

#### CNC

- ▼ Self-manufacturing parts

- ▼ Automated recipe configuration

#### **Plating**

√ Various plating materials:

Au/ AuCo/ AuCu/ Rh/ Ag/ PdNi/ NiP/ NiCo

Choose coating based on product attributes: varying in anti-adhesion, anti-oxidation, wear resistance, and corrosion resistance

#### **Assembly**

√ 100% automation assembly and inspection (AOI)

#### **Analysis**

#### Mechanical property Hardness test

#### Plating Roughness Meas & Thickness Meas

# Automotive gate driver package with galvanicallyisolated communication linkage

By Ankur Shah, Burton Carpenter, Fred Brauchler, Di Liu, Pierre Calmes, JM Liu, Xueting Wu [NXP Semiconductors, Inc.]

ith legislation driving to reduce CO2 emissions, electric vehicles (EVs) are a perfect alternative to internal combustion engine (ICE) vehicles and government incentives are encouraging faster adoption from ICE vehicles to EVs. Approximately half of all vehicles sold by 2030 will contain an electrified powertrain [1]. Furthermore, vehicle electrification is driving advanced functional safety, control and protection features in automotive EV electronics. Many on-board systems such as EV traction inverters, DC/DC converters, and on-board chargers are powered by, or connected to, high-voltage power sources. For example, a traction inverter converts DC voltage from a high-voltage battery into a high-current, multi-phase AC voltage to drive the traction motor. Microcontroller unit (MCU) output is not capable of driving a power device (insulated-gate bipolar transistor [IGBT] or silicon carbide [SiC]), which in turn drives the traction motor. Therefore, to drive the power device, an isolated gate driver is essential because of features such as a strong gate drive and overshoot protection; additionally, faster switching allows for higher efficiency, faster reverse recovery, and lower input capacitance, etc.

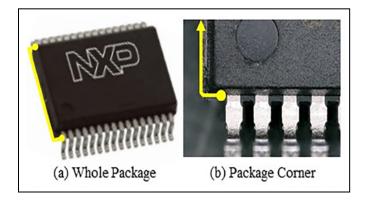

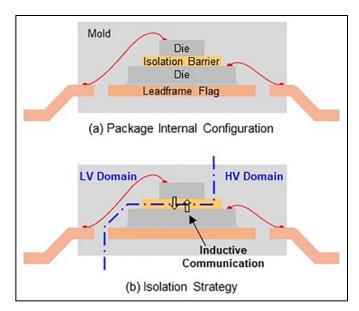

A 32-lead small outline integrated circuit (SOIC) package with leads on only two sides was selected to meet the creepage and clearance requirements. Internal isolation was achieved by placing a high-voltage dielectric barrier between two stacked die that could communicate by inductive (magnetic) coupling. Galvanic isolation, therefore, was achieved between the high voltage (HV) and low voltage (LV) sides, thereby meeting the UL 1577 requirement for 5000V<sub>rms</sub> isolation for 60 seconds. Accelerated lifetime tests confirmed working voltages up to 1500V<sub>pk</sub> can be maintained for at least 20 years. Finally, the package passed the full suite of Automotive Electronics Council (AEC) Q100 Grade 1 component reliability requirements, including AEC Q006 Cu wire criteria.

#### **Galvanic** isolation

Galvanic isolation is the principle of isolating functional sections of electrical systems to prevent current flow—no direct conduction path is permitted. However, energy or information can still be exchanged between the sections by other means, such as capacitive, inductive (magnetic), optical, acoustic or mechanical coupling. Furthermore, the device must meet certain performance criteria and pass AEC Grade 1 component qualification for under-the-hood operation.

An advanced gate driver package makes direct physical electrical connections to both HV and LV domains, therefore, safety and functional requirements necessitate that design, testing and manufacture of the gate driver component ensure galvanic isolation between these domains.

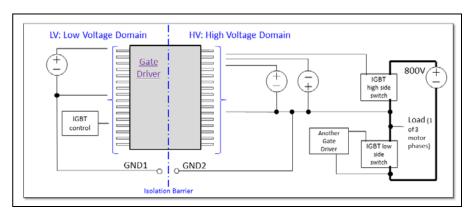

In a typical application as shown in Figure 1, the gate driver is electrically connected to two isolated voltage domains, termed LV and HV. The LV leads connect to the automobile control system powered by the 12V~48V battery grounded to the vehicle chassis.

Meanwhile, the HV leads connect to the 400V~800V battery that powers the drivetrain motors. For safety and functional reasons, the package must maintain galvanic isolation between the LV and HV domains. Functional safety requirements for the gate drivers is at Automotive Safety Integrity Level D (ASIL-D).

The development and release of this gate driver package occurred in two phases. A summary for the initial 7.72mm creepage automotive drivetrain application was summarized by Carpenter, et al. [2]. This paper provides an overview of the upgraded package with greater creepage, enhanced design criteria, and improved HV performance: achieving a comparative tracking index (CTI) >600V (Material Group 1), creepage >8mm, and common mode transient immunity (CMTI) >200V/nsec.

#### **Product features**

NXP's gate driver IC (GDIC) is functionally safe (ASIL C/D compliant) and can be used with both 400V and 800V traction inverter systems. These new isolated GDICs have features optimized for operation with both IGBT and SiC power devices. These features include dynamic gate strength control (+/-10A to +/-30A)

Figure 1: Schematic of gate driver application.

| Category      | Item                 | Criteria                                               |  |

|---------------|----------------------|--------------------------------------------------------|--|

|               | Noise Immunity       | CMTI > 200 V/ns                                        |  |

| Communication | Comm Delay           | <10 ns                                                 |  |

| Performance   | Direction            | 2-way communication                                    |  |

|               | Power                | <2.5mW per channel                                     |  |

| Reliability   | Component            | AEC Grade 1 + Cu Wire                                  |  |

| Galvanic      | High Side<br>Voltage | Drive motors powered by 800V DC battery                |  |

| Isolation     | LV-HV Isolation      | Galvanic isolation<br>5000V <sub>rms</sub> for > 1 min |  |

| Manufacturing | Yield                | Equivalent to similar package                          |  |

Table 1: Key design criteria.

for optimized drive capability. Several external bill of materials (BOM) components are reduced or removed though features integrated into the gate drivers, thereby providing system-level board space and cost savings. This new GDIC incorporates programmable control for protections, monitoring, and diagnostic features such as <1µs short-circuit detection, temperature, over-voltage/over-current protection and power device aging detection, which enable optimized performance and predictive maintenance of the traction inverter and power devices.

| System Leve                | el Sta | andards                                                                                           |  |  |

|----------------------------|--------|---------------------------------------------------------------------------------------------------|--|--|

| IEC 60065-1                | [3]    | Audio / Video Safety requirements                                                                 |  |  |

| IEC 60950-1                | [4]    | Information Technology Equipment - Safety                                                         |  |  |

| IEC 61010-1                | [5]    | Electrical equipment for measurement, control, and laboratory - Safety                            |  |  |

| IEC 61800-5                | [6]    | Motor Drives & Inverters<br>Safety requirements                                                   |  |  |

| IEC 61000-4-5              | [7]    | Surge immunity test (needed for connection to European line voltage)                              |  |  |

| Component                  | Leve   | l Standards                                                                                       |  |  |

| AEC Q100 H                 | [8]    | Automotive Component Qualification                                                                |  |  |

| AEC Q006 A                 | [9]    | Addendum to Q100 for components with Cu wirebond                                                  |  |  |

| UL 1577                    | [10]   | Universal Digital Isolator Standard –<br>Accepted/Mandated for all Digital Isolators<br>worldwide |  |  |

| IEC 60747-17               | [11]   | Magnetic and capacitive coupler safety standard                                                   |  |  |

| VDE 0884-10<br>VDE 0884-11 | [12]   | Magnetic and capacitive coupler safety standard                                                   |  |  |

|                            |        | indards: attempt by IEC to harmonize mechanical standards                                         |  |  |

| IEC 60664-1                | [13]   | Insulation Coordination for equipment within low voltage systems                                  |  |  |

| Test Method                | s      |                                                                                                   |  |  |

| IEC 60270                  |        | High-voltage test techniques –                                                                    |  |  |

Table 2: Applicable standards and description.

#### Design objectives

Key performance, reliability, isolation and manufacturing criteria necessary to satisfy the application requirements are summarized in Table 1. Communication performance refers to data transfer between voltage domains. In fact, galvanic isolation demands a multitude of requirements driven by a variety of industry standards, summarized in Table 2 (references in table). Component reliability qualification followed the norms of AEC Q100 and Q006.

[14] Partial discharge measurements

#### Package design

To achieve galvanic isolation, the package is divided into LV and HV regions that could electrically connect to their respective system domains but remain insulated from each other by appropriate isolation barriers. The design required isolation strategies external to the package (outside the mold body) and internal to the package (inside the mold body). The standards in Table 2 define a variety of metrics to ensure packages and systems can meet their stated isolation specifications. Table 3 summarizes exemplary parameters from these standards.

External isolation is achieved by selecting a package outline to meet the first two parameters in Table 3: creepage and clearance. A 32-lead 7.5mm x 11.0mm wide-body SOIC package is ideal. With leads on only two sides, leads 1-16 are connected to the LV domain and leads 17-32 to the HV domain. Figure 2 illustrates that the creepage path around

| Purpose                                                                | Parameter                                 | Standard/Definition                                                                                                          | Target<br>Spec                               |

|------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Prevent flash over or arcing between                                   | Creepage                                  | IEC 60664-1<br>Shortest distance along<br>the surface of a solid<br>insulating material<br>between two conductive<br>parts   | ≥ 8 mm                                       |

| package<br>external leads                                              | Clearance                                 | IEC 60664-1<br>Shortest distance in the<br>air between two<br>conductive parts                                               | ≥ 8 mm                                       |

| Surge<br>protection<br>Ex. Lightning<br>strike                         | Viosm                                     | IEC 60747-17<br>Maximum Surge<br>Isolation Voltage                                                                           | 10 kV <sub>pk</sub><br>50x ~50μsec<br>pulses |

| Allow time for<br>system safe<br>shutdown                              | Viso                                      | UL 1577<br>Maximum Withstanding<br>Isolation Voltage                                                                         | 5 kV <sub>rms</sub><br>1 min                 |

| Lifetime<br>working<br>voltage                                         | Viorm                                     | VDE 0884-11<br>Maximum Repetitive<br>Peak Isolation Voltage                                                                  | 1.5 kV <sub>pk</sub><br>20 years             |

| Production<br>screen to<br>weed out<br>defective<br>units              | PD<br>(Partial<br>Discharge)              | VDE 0884-10, -11<br>A localized electrical<br>discharge that partially<br>bridges the insulation<br>between conductors       | ≤5pC<br>@ 2.9 kV <sub>pk</sub>               |

| Classify<br>surface<br>insulation<br>resistance of<br>mold<br>compound | CTI<br>(Comparative<br>tracking<br>index) | VDE 0884-10, -11 An insulation material's resistance to damage and surface current when exposed to conductive contamination. | ≥ 600V                                       |

Table 3: Isolation metrics.

Figure 2: 32-lead SOIC package (7.5mm x 11.0mm). The yellow line indicates creepage path.

Figure 3: Package side view. The red line indicates clearance path.

Figure 4: Schematic of package internal structure.

the package edge could maintain the specification value even with worst-case tolerance stack-up (lead placement, body size, etc.). Similarly, the heels of the leads could maintain clearance under the package mold body as shown in Figure 3.

The package internal configuration and isolation strategy are shown in Figure 4. Device functionality is partitioned into two dies-one for each domain. The stacked structure permits communication elements on each die to directly transfer data using inductive coupling across the galvanic isolation barrier. The materials and internal spacings are designed to pass the last five HV isolation tests in Table 3. Note that maximum surge isolation voltage  $(V_{IOSM})$ , maximum withstanding isolation voltage (V<sub>ISO</sub>), and maximum repetitive peak isolation voltage (V<sub>IORM</sub>) are intended to ensure isolation integrity on three very different time scales: microseconds, seconds and years, respectively. Known as Type Tests, these three can only be performed on representative samples not intended for shipment. In other words, the tests are considered destructive even for passing devices. On the other hand, Partial Discharge (PD) method B1 is an industry standard production screening method. Furthermore, safety compliance to UL 1577, IEC 60664, IEC 6074717, and VDE 0884-10 have been certified. VDE 0884-11 certification is ongoing.

#### Discussion

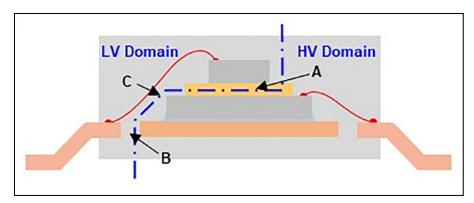

Critical distances in the definitions of creepage and clearance (Table 3) ensure external isolation. While not explicit, minimum spacing must be maintained between HV and LV domains within the package to pass the internal isolation requirements. The cross section in Figure 5 highlights three critical geometry locations in the package as follows: A: Isolation barrier within the die stack; B: LV leads and die flag; and C: Wire loop from the LV die crossing over the HV die. Each specific critical distance depends on the dielectric breakdown strength of intervening material.

The isolation barrier (A) thickness balanced competing requirements: thicker improved isolation, but thinner

Figure 5: Critical internal package geometries.

reduced communication loss and power consumption. The final design value achieved this balance. Margin was demonstrated through electrical simulations and experimental studies. Maximum and minimum thickness barriers maintained both device functionality and V<sub>ISO</sub> isolation (5kVrms for over 60 seconds). Likewise, the inner lead to flag spacing (B) was designed to perform at the worst-case manufacturing tolerance. V<sub>ISO</sub> actually passed greater than 8kVrms before failing in these locations. Finally, wire looping (C) always maintained the same minimum distance required for location B.

Defectivity control was critical in the isolation barrier (A) because the narrow spacing between die intensified the electric field strength. Small voids or foreign matter could cause either shortterm failures under voltage peaks or premature wear-out over time due to degradation of the insulation around the defect. PD testing effectively identified such units. Void area was correlated to PD capacitance, and suitable production control limits were established. The twostage production PD test (isolation barrier check at the first voltage plus capacitance measurement at the second voltage) ensured that all units could meet the field isolation requirements on all time scales: microseconds, seconds and years.

#### Summary

A package designed for automotive high-voltage gate driver applications was partitioned into two galvanicallyisolated domains to meet functional and safety requirements. Inductive coupling between two stacked dies permits dieto-die communications through an isolation barrier. This package was tested to a variety of industry system and component safety standards from UL, VDE and IEC. Representative HV stress tests were described with an explanation for their relevance to the application. The package passed the representative HV type tests, including V<sub>IOSM</sub>, V<sub>ISO</sub>, and V<sub>IORM</sub>. Additionally, all requirements of AEC Grade 1 copper wire qualifications were met.

#### References

- 1. Compiled from several sources: Strategy analytics, HIS, Evercore.

- 2. B. Carpenter, et al., "Automotive gate driver package with galvanically isolated communication linkage," SMTAI, Nov. 2021.

- "Audio, video and similar electronic apparatus – Safety requirements," IEC60065-1, June 2014.

- 4. "Information technology equipment Safety Part 1: General requirements," CEI/IEC 60950-1, Dec. 2005.

- 5. "Safety requirements for electrical equipment for measurement, control, and laboratory use Part 1: General requirements," IEC61010-1, Mar. 2019.

- 6. "Adjustable speed electrical power drive systems Part 5-1: Safety requirements Electrical, thermal and energy," IEC61800-5, June 2012.

- 7. "Electromagnetic compatibility (EMC) Part 4-5: Testing and measurement techniques Surge immunity test," IEC 61000-4-5, Aug. 2017.

- "Failure mechanism based stress test qualification for integrated circuits," AEC Q100 Rev. H, Sept. 2014.

- "Qualification requirements for components using copper (Cu) wire interconnections," AEC Q006 Rev. A, July 2016.

- 10. "UL standard for safety for optical isolators," UL 1577, Apr. 2014.

- "Semiconductor devices Part 17: Magnetic and capacitive coupler for basic and reinforced isolation," IEC/PAS 60747-17, Sept. 2020.

- 12. "Semiconductor Devices Part 11: Magnetic and capacitive coupler for basic and reinforced isolation," DIN VDE V 0884-11, Jan. 2017.

- 13. "Insulation coordination for equipment within low-voltage systems Part 1: Principles, requirements and tests," IEC/CEI 60664-1:2007, Apr. 2007.

- 14. "High-voltage test techniques Partial discharge measurements," IEC 60270:2000+A1:2015: Dec. 2000, amended Nov. 2015.

Ankur Shah is a Principal Packaging Engineer at NXP Semiconductors, Inc., in Chandler, AZ. He received a Master's degree in Electrical Engineering from Arizona State U. He has 14 years of experience in the semiconductor industry in various roles such as packaging, test and product management. He leads package development efforts for gate drivers, battery management system and high-precision analog products. Email: ankur.shah@nxp.com

Burt Carpenter is a Technical Director at NXP Semiconductors, Inc., in Austin, TX. He received BS and MS degrees in Materials Engineering from Rensselaer Polytechnic Institute. During the past 29 years, Burt has held positions in package process development, design, modeling and package integration as the company transitioned ownership from Motorola to Freescale to NXP. Currently, he is focused on fan-out and panel-level packaging.

# COATING SYSTEM FOR MORE THROUGHPUT

With up to six wet process modules and improved wafer handling due to In Motion Centering (IMOC), SUSS MicroTec's ACS200 Gen3 TE takes the very successful ACS200 Gen3 coating platform to a new level. Next to increasing throughput, it reduces energy and media consumption with features like temperature and flow controllers. Furthermore, it enables new technologies like inkjet printing for automated systems.

SUSS MicroTec info@suss.com www.suss.com

Contact us for more information!

GLOBAL LEADER LEENO

**HEAD OFFICE**10 105beon-gil, Mieumsandan-ro Gangseo-gu, Busan, Korea

USA: hskang@leeno.co.kr / +1 408 313 2964 / +82 10 8737 6561 korea: sales-leeno@leeno.co.kr / +82 51 792 5639

# Automotive LiDAR: Photonics assembly requirements and trends

By Limin Zhou, Avy Yi [MRSI, a part of Mycronic Group]

n this paper, the similarities and differences between automotive light detection and ranging (LiDAR) and optical transceivers are compared. The photonics device assembly requirements and trends in automotive LiDAR are introduced. From the analysis, an assembly solution for automotive LiDAR is explained. Finally, a demonstration of the solution with actual assembly experiments for typical edge-emitting lasers (EELs) and vertical cavity surface emitting laser (VCSEL) chips for automotive LiDAR are presented.

#### **Overview**

Vehicular safety has always been very important to the automotive industry and the situational awareness enabled by advanced sensors plays a critical role in building safe self-driving vehicles. Most car makers believe LiDAR is necessary and important for both advanced driving assistance systems (ADAS) and autonomous vehicles (AVs). The demand for automotive LiDAR in ADAS applications is growing at a high double-digit compound annual growth rate (CAGR), and mass production of automotive LiDAR is rapidly becoming a reality. Driven by new technologies and economies of scale, automotive LiDARs are becoming lighter, thinner, and cheaper. The high-reliability assembly of photonics devices is the key challenge for the mass production of highly-reliable automotive LiDAR. To address this challenge, it is necessary to understand the assembly needs and technology trends of automotive LiDAR, and then provide the best photonics device assembly solution.

## Photonics devices assembly in automotive LiDAR

Automotive LiDAR is a complex photonics sensor system that consists of multiple optical components, including lasers, amplifiers, phase and amplitude-

| Items                   | Automotive LiDAR                                                                       | Optical Transceiver                                                                          |

|-------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Performance             | Range, resolution, frame rate                                                          | Data rate, distance                                                                          |

| Package                 | No industrial standard, Customer Spec                                                  | Industrial standard, SFP/CFP/QSFP/OSFP/                                                      |

| Standard                | AEC-Q                                                                                  | Telcordia GR-468                                                                             |

| Temperature             | Reliability: (AEC-Q100-REV-H)                                                          | Reliability: (Telcordia GR-468-CORE)                                                         |

|                         | Grade 0: -40°C to +150°C                                                               | Storage temperature range is from -40 °C to 85 °C                                            |

|                         | Grade 1: -40°C to +125°C                                                               | Operation temperature range is from -5 °C to 75 °C (Datacom 0°C to 70°C, 15°C to 55°C)       |

|                         | Grade 2: -40°C to +105°C                                                               |                                                                                              |

|                         | Grade 3: -40°C to +85°C                                                                |                                                                                              |

|                         | (ambient operating temperature range)                                                  |                                                                                              |

| Volume                  | High mix and volume from low to high, depends on customer application                  | High volume for datacom transceiver                                                          |

| Innovation              | Fast-paced innovation and NPI, need flexible multi-dies and multi-processes            | Steady pace of innovation and NPI, need a<br>relatively flexible die bonding process machine |

| Customer<br>expectation | Lower cost, higher reliability, higher performance                                     | Lower cost, higher bit rate, lower consumption                                               |

| Lifetime                | 10k-100k hrs/>10 years                                                                 | Datacom >3~5 years                                                                           |

| Quality System          | IATF 16949                                                                             | ISO 9000                                                                                     |

| Manufacturing           | No mature solutions for assembly & testing, developed by LiDAR suppliers and customers | Proven solutions for assembly and testing                                                    |

Table 1: Automotive LiDAR vs. optical transceiver.

control low-noise photodiodes, mode converters, and optical waveguides, etc. **Table 1** shows the comparison of automotive LiDAR and optical transceivers. Based on the table entries, automotive LiDAR is in an earlier phase of product life cycle than the optical transceiver.

From Table 1, we know automotive LiDAR does not have industry standards for packages and optoelectronics (OE) interfaces at this point in time. The end users of automotive LiDAR have diverse package design requirements to fit it into their cars. This means that the vehicle manufacturers decide on the package form and interface of automotive LiDAR devices. If a LiDAR supplier targets multiple vehicle models from multiple car companies, there will be a wide range of package form factors. Manufacturing in the automotive LiDAR industry, therefore, will be high-mix low-volume for the time being. As a result, LiDAR suppliers have to provide flexible equipment to support different customers' packaging and assembly process designs.

The quality system of the LiDAR supplier has to pass the IATF 16949 certification process. Additionally, automotive LiDAR has to pass the AEC-Q series reliability test, especially the higher temperature operation reliability test. While the reliability of the photonics chips/dies must be high enough to ensure the final products meeting the AEC-Q reliability requirements, the chip assembly solution must also meet the same reliability standard. Laser chips and their assembly are the most critical factors in determining the reliability of the LiDAR system. Highreliability laser chip assembly can enable the high-reliability automotive LiDAR volume manufacturing to meet IATF 16949 zero defect requirements. To that end, advanced equipment and processes are needed.

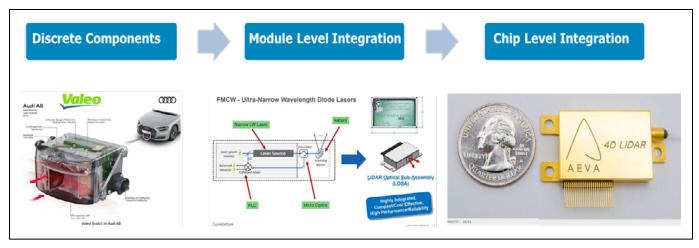

With the advancement of new technologies, we find that automotive LiDAR imaging technology has evolved from mechanically-scanned LiDAR to hybrid solid-state LiDAR, and then to solid-state LiDAR. The packaging of automotive LiDAR evolved from discrete

Figure 1: Automotive LiDAR package design trends.

components to module-level integration, and even chip-level integration (see Figure 1). The market is trending towards highly-integrated, thinner and cheaper products [1-4]. Consequently, higher accuracy assembly is required to manufacture the photonics devices. Automotive LiDAR has a similar photonics device assembly process to that of the optical transceivers, and the

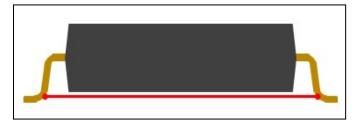

assembly accuracy and other requirements are also similar. Depending on the different laser package designs, from 5µm to 0.5µm is the typical high-accuracy requirement for laser die; other parts, however, may have less critical accuracy requirements. In general, most edge-emitting laser dies are attached with a eutectic process (some may use an epoxy process); VCSEL laser dies are usually

attached with an epoxy process, and an optical lens with ultraviolet (UV) epoxy plus in situ curing.

According to Yole Intelligence [5], "The LiDAR market for passenger cars (PC) and light commercial vehicle (LCV) and robotaxis is expected to reach \$4.5B in 2028 with a 55% CAGR from 2023." So the LiDAR volume will ramp up very fast. In the long run, technological choices will have to be made to be aligned with mass production, low cost, and high performance, and pricing pressure will increase. Lower cost and high-reliability mass production will be essential. Therefore, the photonics devices assembly solution for automotive LiDAR must have higher efficiency for low-cost volume manufacturing. To summarize, the photonics assembly requirements for automotive LiDAR are high reliability, high flexibility, high accuracy, high speed and fully automated.

# Solutions for photonics die assembly

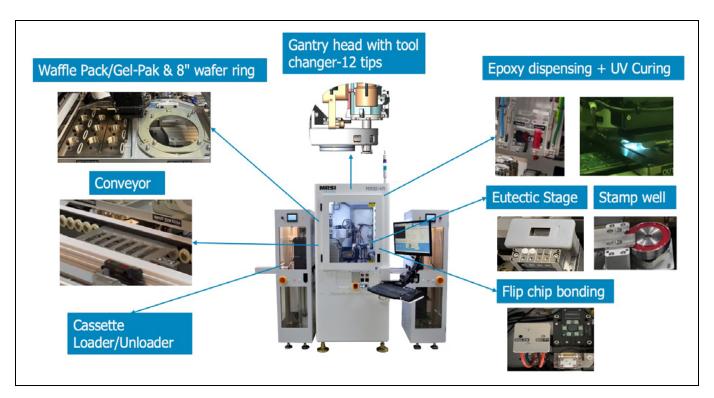

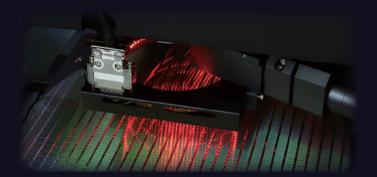

Similar to optical transceivers, higher flexibility, higher reliability, higher accuracy, and higher speed (efficiency) are the solutions to address the challenges of volume manufacturing in the automotive LiDAR industry. We have provided solutions to the industry challenges with our MRSI-H-LD die bonder (Figure 2).

Our bonder has an accuracy of  $\pm 1.5 \mu m@3\sigma$ . Higher accuracy is also available as an option ( $\pm 1 \mu m@3\sigma$ ). This bonder has a very stable gantry head and is equipped with a patented tool changer that does not require recalibration after the tool change. The tool changer is equipped with a 12-tip turret to achieve "on-the-

Figure 2: MRSI-H-LD die bonding machine features.

fly" tool change for the multi-die process. The bonder also has multiple die bonding process capabilities and supports eutectic bonding, epoxy stamping and dispensing, UV curing, and flip-chip bonding.

#### **Experiments**

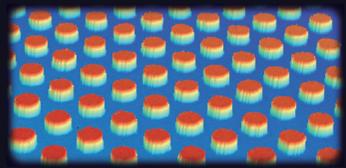

The laser chip assembly process is the most critical step that affects the reliability of automotive LiDAR assembly. The experiments we performed involved the selection of two typical laser chips that are used for automotive LiDAR applications. One is the 905nm EEL high-power laser chip and the other is the 905nm high-density multi-junction VCSEL chip.

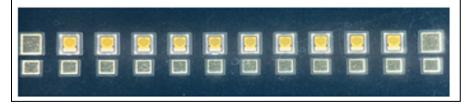

For the 905nm EEL high-power laser chip bonding, both eutectic and epoxy processes are used in automotive LiDAR depending on the laser package design. We completed experiments for eutectic bonding and had the following results: 1) Both X/Y post-bonding accuracy measurements are  $2.7\mu\text{m}@3\sigma$  and the angle accuracy is  $0.13^{\circ}@3\sigma$ ; and 2) For the epoxy process experiment, the post-bonding accuracy for X/Y is  $2.8\mu\text{m}@3\sigma/3.0\mu\text{m}@3\sigma$ , respectively, and the angle accuracy is  $0.27^{\circ}@3\sigma$ . Figure 3 shows the 905nm EEL high-power laser die bonding results for the eutectic and epoxy processes.

Typically, for 905nm high-density multi-junction VCSEL chip bonding,

#### Eutectic Post Bonding Results (mm)

| Item  | Х      | Υ      | Angle |

|-------|--------|--------|-------|

| MAX   | 0.0085 | 0.7241 | 0.14  |

| MIN   | 0.0069 | 0.7223 | 0.053 |

| Range | 0.0016 | 0.0018 | 0.087 |

| 3σ    | 0.0027 | 0.0027 | 0.132 |

#### Epoxy Post Bonding Results (mm)

| Item  | Х       | Y       | Angle |

|-------|---------|---------|-------|

| MAX   | 0.0011  | 0.0011  | 0.218 |

| MIN   | -0.0007 | -0.0011 | 0.057 |

| Range | 0.0018  | 0.0022  | 0.161 |

| 3σ    | 0.0028  | 0.0030  | 0.276 |

Figure 3: 905nm EEL high power laser die bonding results by eutectic and epoxy processes.

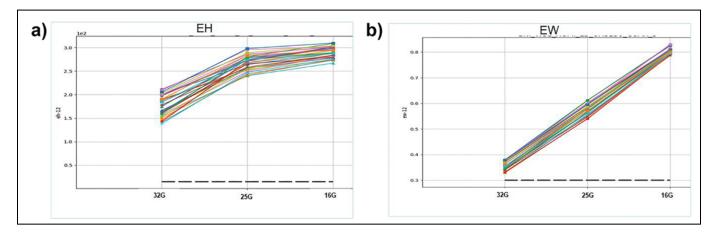

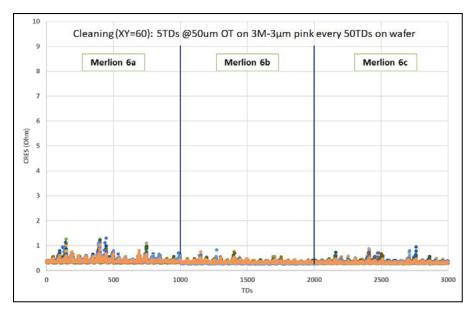

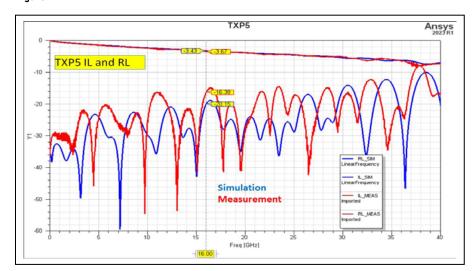

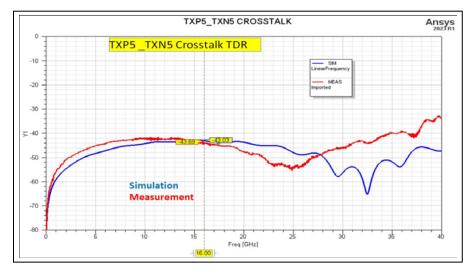

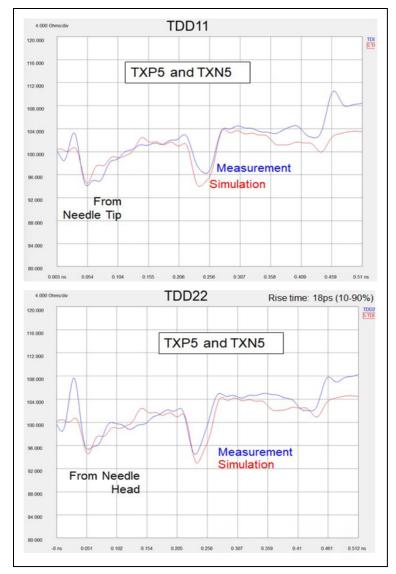

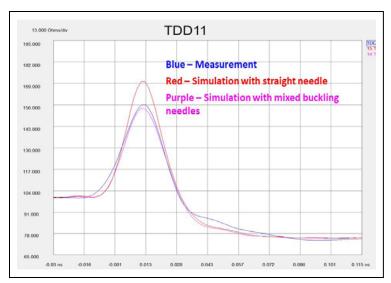

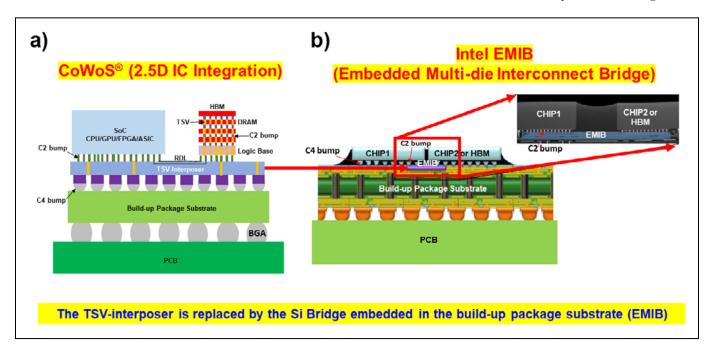

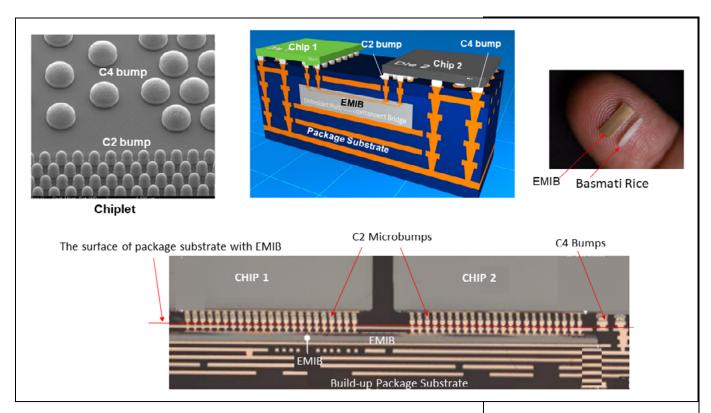

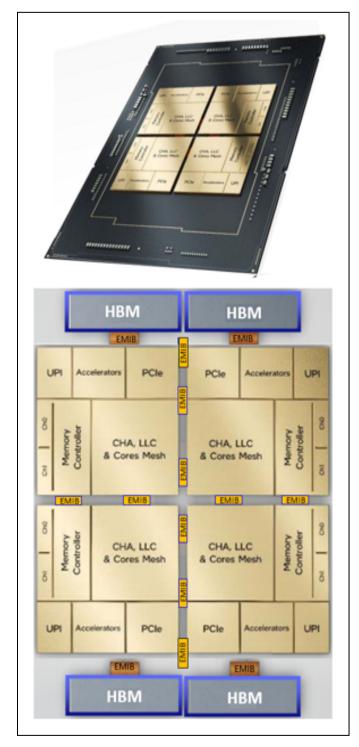

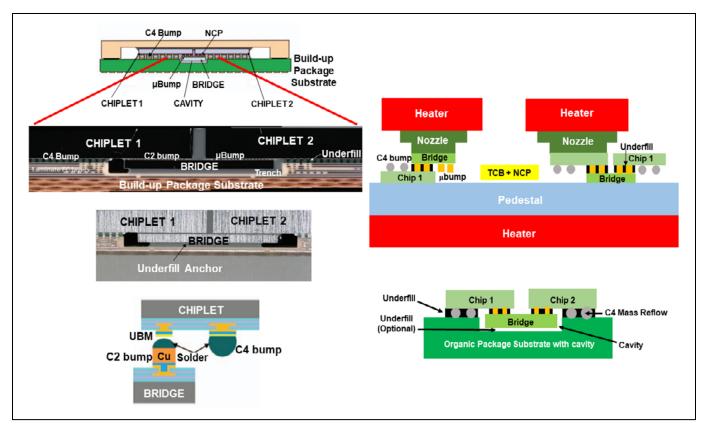

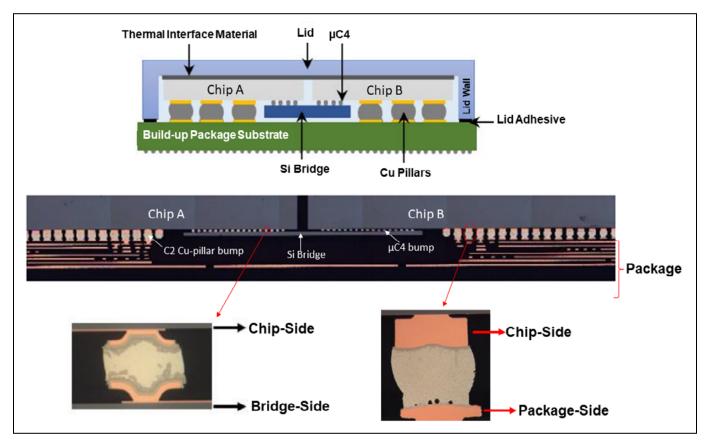

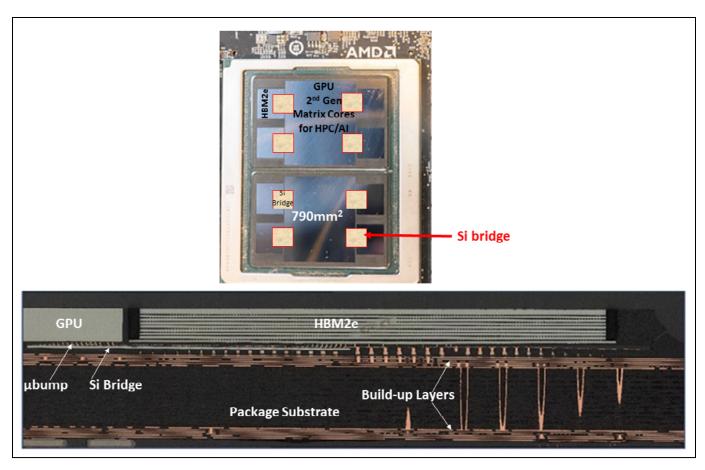

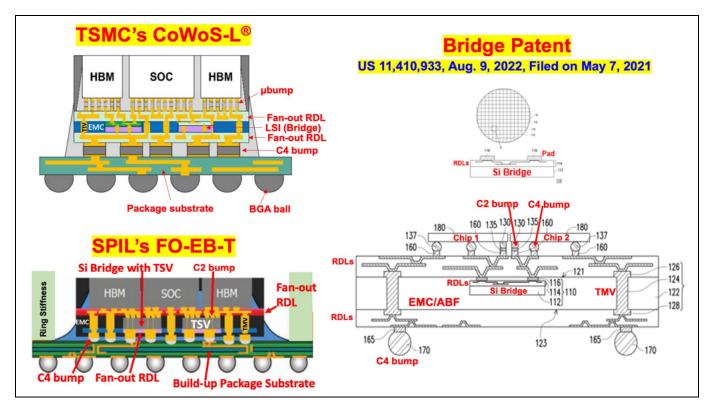

### Die Post Bonding Results (mm)