# Chip Scale Review<sup>®</sup>

ChipScaleReview.com

#### The Future of Semiconductor Packaging

Volume 27, Number 4

July • August 2023

mina Cum

A new generation of e-beam lithography to enable packaging at the leading edge

- Transitioning from 3D packaging to 3DHI

- Foundry 2.0: A renaissance in innovation

- An academic/industry model for integrated systems packaging

- · HI of chiplets technology enabled by AP architectures, first-level interconnect

- Parallel validation strategies minimize debug time and ensure sufficient test coverage

444444

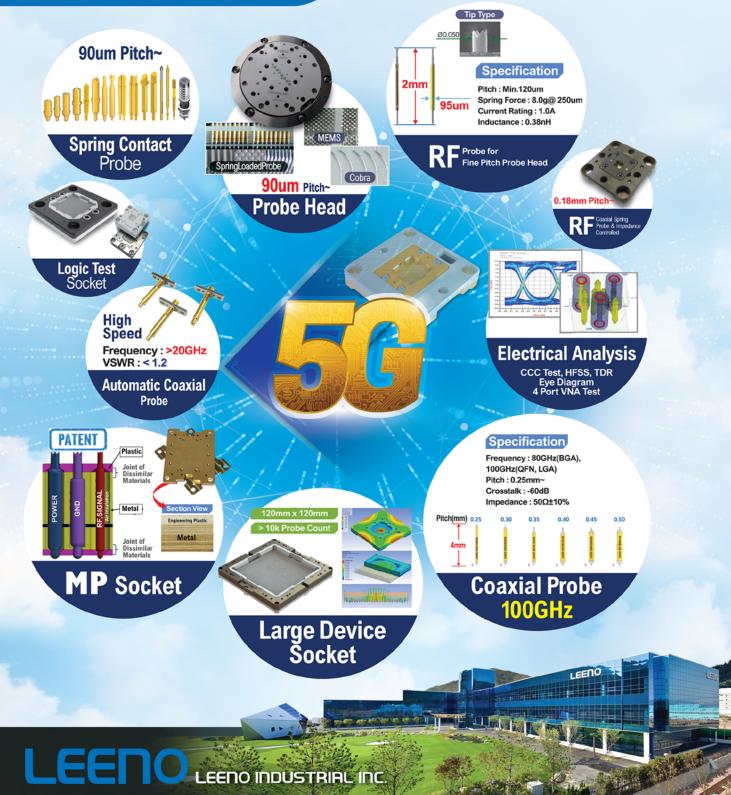

# LEENO

Fine Pitch Probe Continuous Non-stop Innovation! & Probe Head

### **Proven Mass Production Capability**

High Speed RF Short Signal Path 0.80mm

with Spring Contact Probe!

#### RF-300 um Pitch

#### Mechanical Spec

- \* Spring Force : 0.212oz (12.0g) @ .0079 (0.20mm)

- Recomme nded Travel : .0079 (0.20mm)

- Full Travel : .0098 (0.25mm) Current Rating : 2.0A

- Material

Barrel - Alloy / Au plated Plunger - Hardened BeCu / Au plated

#### Spring-Music Wire / Au plated

- Electrical Spec. (Simulation data)

- Propagation Delay : 7.68ps

- Capacitance : 0.05pF

- Inductance : 0.25nH

- Return Loss : > 100GHz @ -10dB (Dielectric material : MDS100)

#### 120 µm Pitch

#### Mechanical Spec.

- Spring Force: 0.281oz (8.0g) @ .0098 (0.25mm) • Rec ommended Travel : .0098 (0.25mm) • Full Travel :.0118 (0.30mm)

- Material : Terminal Pd Alloy / No plated Plunger - Pd Alloy/ No plated Barrel - Ni-Au Alloy / Au plated Spring - Music Wire / Au plated

#### Electrical Spec. (Simulation data)

- Current Rating : 1.0A

- Propagation Delay : 20.80ps

- Capacitance : 0.21pF Inductance : 0.38nH

- Insertion Loss : 40.83GHz @ -1.000dB

- Return Loss : 30.03GHz @ -10.000dB (Dielectric material : CERANIC)

#### 110 µm Pitch

- Mechanical Spec.

- Spring Force: 0.212oz (6.0g) @ .0118 (0.30mm) mmended Travel : .0118 (0.30mm)

- Full Travel :.0138 (0.35mm) Material : Terminal – Pd Alloy / No plated

- Plunger Pd Alloy / No plated Barrel - Ni-Au Alloy / Au plated

#### Spring – Music Wire / Au plated Electrical Spec. (Simulation data)

- Current Rating : 0.9A

- Propagation Delay : 38.25ps

- Capacitance : 0.47pF

- Inductance : 0.63nH Insertion Loss : > 50.00GHz @ -1.000dB

- Return Loss : > 50.00GHz @ -10.000dB

- (Dielectric material : CERAMIC)

100 $\mu$ m Pitch

#### Mechanical Spec.

- Spring Force: 0.247oz (7.0g) @ .0118 (0.30mm)

- mmended Travel :.0118 (0.30mm) • Full Travel :.0138 (0.35mm)

- Material : Terminal Pd Alloy / No plated

- Plunger Pd Alloy / No plated Barrel - Ni-Au Alloy / Au plated Spring - Music Wire / Au plated

#### Electrical Spec. (Simulation data)

- Current Rating : 0.8A

- Propagation Delay : 35.55ps

- Capacitance : 0.44pF

- Inductance : 0.66nH

- Insertion Loss : > 50.00GHz @ -1.000dB • Return Loss : > 50.00GHz @ -10.000dB

- (Dielectric material : CERAMIC)

#### GLOBAL LEADER LEENO

HEAD OFFICE 10 105beon-gil, N CONTACT USA : hskang@le . Mieumsandan-ro Gangseo-gu, Busan, Korea

USA : hskang@leeno.co.kr / +1 408 313 2964 / +82 10 8737 6561 korea : sales-leeno@leeno.co.kr / +82 51 792 5639

#### July • August 2023 Volume 27, Number 4

Advanced packaging technologies fuel today's most exciting new applications, but are limited in I/O density, bandwidth, and scale. Novel trends toward adaptable directwrite lithography are emerging to enable a new generation of leading-edge advanced packaging, yielding more connectivity, higher density, and faster speeds between chips.

Cover image courtesy of Multibeam Corporation

## CONTENTS

#### **DEPARTMENTS**

#### **EXECUTIVE VIEWPOINT**

7 A new generation of e-beam lithography to enable packaging at the leading edge

By David K. Lam, Ken MacWilliams [Multibeam Corporation]

#### **GUEST EDITORIAL**

**34** Foundry 2.0: A renaissance in innovation By Bob Patti [NHanced Semiconductors]

#### PERSPECTIVES IN R&D

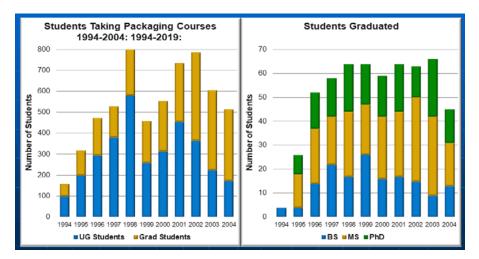

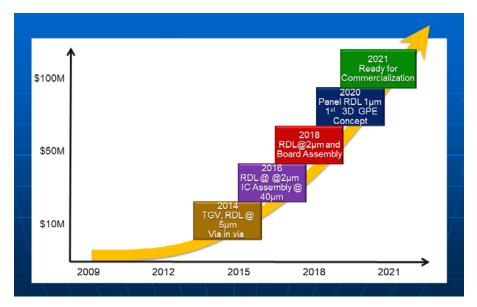

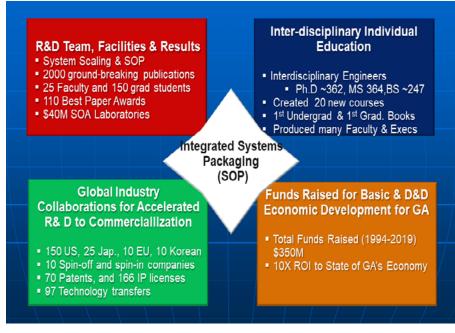

**38** A pioneering and successful academic-industry model in integrated systems packaging at Georgia Tech By Rao R. Tummala [Georgia Tech]

#### **INDUSTRY NEWS**

By Ibrahim Guven [General Chair, 2023 IEEE 73rd Electronic Components and Technology Conference and Virginia Commonwealth University]

## Unmatched Flexibility Exceptional Performance

Unleash the power of Amkor's automotive-ready FCBGA packages!

Experience unrivaled reliability and design flexibility for demanding environments. Discover state-of-the-art solutions with unmatched versatility and unlock the full potential of your applications!

Hito

## FUSION AND HYBRID BONDING FOR HETEROGENEOUS INTEGRATION

Enabling advanced 3D device stacking and chiplet integration for CMOS image sensors, memory and 3D system-on-chip (SoC)

High-volume production equipment and process technology for Wafer-to-Wafer (W2W) and Die-to-Wafer (D2W) hybrid bonding

GEMINI<sup>®</sup> FB Automated Production Wafer Bonding System delivers industry leading alignment accuracy and bonding performance

Heterogeneous Integration Competence Center<sup>™</sup> serving as leadingedge innovation incubator for EVG customers and partners

GET IN TOUCH to discuss your manufacturing needs www.EVGroup.com

### Chip Scale Review

STAFF Kim Newman Publisher knewman@chipscalereview.com

Lawrence Michaels Managing Director/Editor Imichaels@chipscalereview.com

Debra Vogler Senior Technical Editor dvogler@chipscalereview.com

#### SUBSCRIPTION-INQUIRIES

Chip Scale Review All subscription changes, additions, deletions to any and all subscriptions should be made by email only to subs@chipscalereview.com

Advertising Production Inquiries: Lawrence Michaels Imichaels@chipscalereview.com

Copyright © 2023 Haley Publishing Inc. Chip Scale Review (ISSN 1526-1344) is a registered trademark of Haley Publishing Inc. All rights reserved.

Subscriptions in the U.S. are available without charge to qualified individuals in the electronics industry. Chip Scale Review, (ISSN 1526-1344), is published six times a year with issues in January-February, March-April, May-June, July-August, September-October and November-December.

P.O. Box 2165 Morgan Hill, CA 95038 Tel: +1-408-846-8580 E-Mail: subs@chipscalereview.com

Printed in the United States

Volume 27, Number 4 July • August 2023

#### **FEATURE ARTICLES**

**10** Transitioning from 3D packaging to 3D heterogeneous integration (3DHI)

By John Park, Vinod Kumar Khera [Cadence Design Systems]

**19** Heterogeneous integration of chiplets technology enabled by advanced package architectures, first-level interconnect *By Nelson Fan, Eric Ng [ASMPT Limited]*

28 Parallel validation strategies minimize debug time and ensure sufficient test coverage

By Adir Zonta [Advantest]

## Elevate<sup>®</sup> Gold 7990 NBV HT

levate

Electrolytic Sulfite Gold

Environmentally responsible exceptionally stable, and extremely versatile.

- Cyanide free

- · Thallium and arsenic free

- Very stable electrolyte

- Extended bath life

- · Low-stress, smooth bright deposit

- Low deposit thickness variation

- Deposits 2-3X more gold in vias

- In global production at high volume manufacturing

## COAXIAL ELASTOMER SOCKET

for >64Gbps ATE/SLT Test for Crosstalk free Board to Board Connector

Semiconductor Package Test

Board to Board Interconnection

Metal GND Structure Extremely Low Crosstalk >100Ghz@-20dB Inductance <0.1nH Min. pitch 0.6mm

P

Elastomer + Conductive Ni Particles GND Shielding by Metal housing G: GND P: Power S: Signal

CONNECTION

GND

G

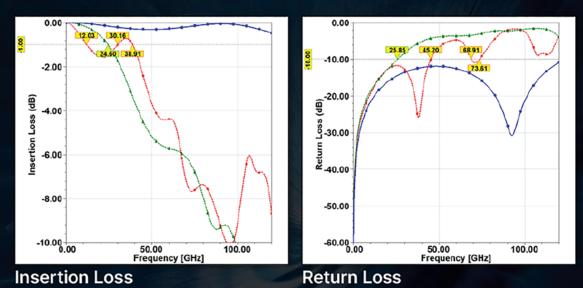

| Electrical Specifications (unit: GHz) |            |           |               |

|---------------------------------------|------------|-----------|---------------|

| 50Ω, 0.80mm pitch                     | Spring pin | Elastomer | ELTUNE-COAX M |

| Electrical Length(mm)                 | 3.05       | 0.60      | 0.60          |

| Insertion Loss(S21) @-1dB             | 12.03      | 24.60     | >100          |

| Return Loss (S11) @-10dB              | 45.20      | 25.85     | >100          |

| Crosstalk (S31) @-20dB                | 14.98      | 9.18      | >100          |

| 102 00/1    |                     |  |  |

|-------------|---------------------|--|--|

| Jong M. Lee | jmlee@tse21.com     |  |  |

| Kevin Kim   | kevin.kim@tse21.com |  |  |

#### TSE HQ

TSE USA

Justin Yun justice@tse21.com Jimmy Hwang jimmyhwang@tse21.com

- ELTUNE-cond<sup>™</sup>

Elastomer

- Spring Pin

#### Crosstalk

www.tse21.com 189, Gunsu 1-gil, Jiksan-eup, Seobuk-gu, Cheonan-si, Chungnam, 31032, Korea

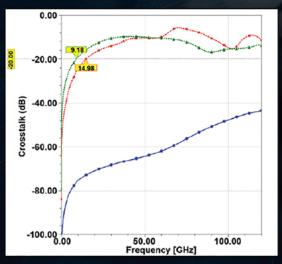

## M-Series<sup>™</sup> with Adaptive Patterning<sup>®</sup>

### One Technology, Many Applications

Expand what's possible

## EXECUTIVE VIEWPOINT

## A new generation of e-beam lithography to enable packaging at the leading edge

By David K. Lam, Ken MacWilliams [Multibeam Corporation]

dvanced packaging technologies are enabling hardware improvements in artificial intelligence

(AI), 5G, high-performance computing (HPC), smart cars, and other applications that will power continuous growth for the semiconductor industry. Over the years, the packaging industry has relentlessly transitioned to enabling technologies. First with flip-chip, then wafer-level packaging, and now 2.5D and 3D packaging technologies. Today, however, these technologies are being stretched to their limits by certain constraints of conventional back-end lithography tools. Take edge computing, for example. Already on a growth trajectory, this application requires large storage and high I/O to meet aggressive new demands in data analysis, inference, and decision making at the edge of the network. The new requirements are driving new technical imperatives for backend lithography tools.

The rising prominence of advanced packaging was noted by TSMC chairman, Mark Liu, as he recently remarked that, "Demand for advanced packaging far exceeds the current production capacity [1]." Liu further noted that the company is, "accelerating the increase in production capacity," to match demand for advanced packaging and, "support the next generation of HPC, AI, mobile applications...to help customers achieve product success and seize market opportunities [1]."

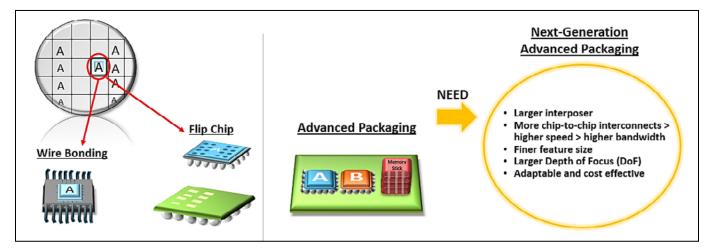

Conventional flip-chip packaging (still used today) has a minimum pitch of about 150 $\mu$ m and advanced microbumps have pushed minimum pitches to below 50 $\mu$ m, yet there remains a critical bottleneck. To overcome the limitations, some "big tech" companies are employing in-house custom processors, accelerators, and networking silicon. But it's clear that next-gen devices will inevitably need more chiplets and

higher bandwidth in package. Indeed, demands for larger interposers, more I/O, greater bandwidth, more processing power, lower latency, and lower power usage are converging to drive the need for a new generation of lithography technology engineered to enable backend imperatives.

We have developed Multicolumn Electron-Beam Litho (MEBL) systems that perform maskless patterning to meet current and projected back-end requirements, as discussed in the sections below.

Edge computing. Edge computing eliminates the bottleneck of datatransfer between the edge device and data center. MEBL's fine-resolution and direct-write capabilities enable higher interconnectivity and higher bandwidth between chiplets. Dense interconnects and I/O can be integrated without the need for large, power-hungry SERDES circuits presently required for highbandwidth communication between chips. All this helps speed in-package data analysis, inference, and decision making, thereby optimizing overall smart computing of edge devices.

Large interposers. Today's interposers are limited to the size of one optical field of view, or a few optical reticle fields, stitched together. In contrast, MEBL's auto-stitch capability enables very large-scale interposers, spanning up to full-wafer. Such large interposers enable a unique flexibility to integrate additional powerful processors for HPC, graphics processing units (GPUs), and AI engines. Furthermore, MEBL is capable of patterning fineinterconnect pitches with more than 10 times higher resolution. This finer resolution creates much greater chipto-chip bandwidth and reduces the SERDES overhead requirements.

**High productivity.** EBL has been valued for decades as an enabling tool for research and pilot purposes.

However, it has never met the throughput standards required for fab production. In contrast, MEBL is fully automated and employs multiple miniature e-beam columns operating in concert to pattern full wafers while the wafer stage is in motion-an architecture also known as "parallel writing on the fly." This allows MEBL to yield 20x to 100x higher productivity than single-beam lithography systems found in research labs. Incidentally, in e-beam mask-making (an adjacent market of MEBL), single-beam writing systems are being replaced by multibeam writing systems for the same reason - higher productivity.

Large depth of focus (DoF). In advanced systems-in-package, the substrate may be stressed and warped by processes such as through-silicon via (TSV) or bonding, resulting in an uneven surface. This poses challenges to optical lithography, which is known for its shallow DoF. The problem intensifies at finer resolutions because optics capable of higher resolution have correspondingly smaller DoF. By using a 100x larger DoF than advanced optical systems [4], we were able to overcome this limitation at finer resolutions. This DoF advantage enables patterning of high-resolution interconnects with relaxed requirements for substrate flatness, bow, and warpage. It helps to overcome patterning challenges associated with non-flat surfaces in advanced packaging.

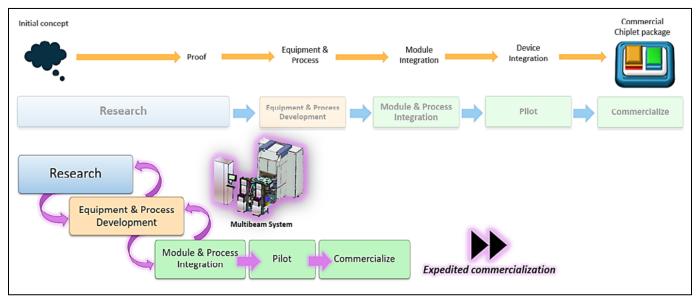

**Rapid cycles of learning.** New applications have ever-increasing requirements for system integration and performance, and, "Increasing complexity continues to create new challenges for package design," as noted in [5]. Cycles of learning are crucial to successful development of new systemsin-package devices. Our system enables rapid testing of early concepts by writing layouts directly onto substrates with no

Figure 1: Enabling co-optimization with rapid cycles of learning to accelerate time to market. SOURCE: Multibeam Corporation

masks (Figure 1). Layout changes can be quickly implemented using MEBL's data prep computer, increasing the speed of learning cycles, and reducing time-tomarket for new products.

### Industry trends driving a new generation of e-beam lithography

Aside from the need for greater fab productivity in EBL technology, there are two major semiconductor industry trends that need to be addressed as discussed below.

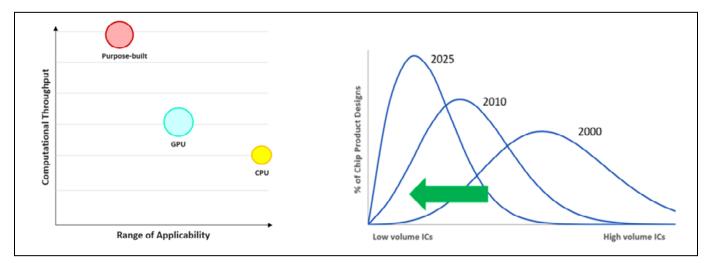

**Purpose-built devices.** Tightly integrated processing, memory, communications, and other functions, can be optimized to

meet the needs of specific applications. Dense interconnects between chiplets will eliminate the need for large SERDES circuits previously needed for highbandwidth chip-to-chip communication. The MEBL solution addresses this need.

Mass customization. Customized devices' compute throughput is distinctly higher than that of general-purpose devices. This has led to an industrywide shift toward mass customization—a trend that aligns very well with advanced packaging. Advanced packaging allows designers to develop purpose-built devices from individual chiplets, thereby optimizing performance and power efficiency. Data shows that "purposebuilt silicon," optimized to accelerate specific tasks, performs significantly better than general-purpose CPUs. This means advanced applications requiring high computation, such as 5G, intelligent edge devices, smart cars, and AI, will all benefit from the trend toward mass customization and purpose-built silicon. With purposebuilt silicon and mass customization on the rise, the demand for advanced packaging is soaring (Figure 2).

Extendible very large-scale interposers will allow manufacturers to maximize

Figure 2: Optimizing performance and power efficiency of advanced packaging by facilitating high-throughput purpose-built silicon and shifting to mass customized designs. SOURCES: Multibeam Corporation, SkyWater Technology

Figure 3: The evolution of advanced packaging to next-generation advanced packaging. SOURCE: Multibeam Corporation

performance by enabling more connections between larger numbers of chiplets in compact, low-power packages.

As packaging evolves and these industry shifts accelerate, back-end lithography will evolve as well. Mask-based optical lithography is a natural fit for highvolume manufacturing and has played an integral role in the chip industry's success. However, device costs rise when fabricating small batches of customized wafers with mask-based lithography technology. Further, mask-based lithography is hindered by die shift that can significantly reduce yield. Such limitations make maskbased lithography less practical for the next-generation of advanced packaging applications. In contrast, maskless e-beam direct writing has inherent advantages in writing fine resolutions across large areas, tying together disparate chiplets into highperforming integrated packages. The maskless MEBL system makes it possible to adjust for die shift, enabling denser interconnects between varied chiplets. This adaptability is crucial in integrating heterogeneous chips into new purposebuilt devices (Figure 3).

#### **Summary**

System and packaging development cycles can take years. With a highproductivity direct-write MEBL system, the development cycle can be reduced significantly. Moreover, this new generation of direct-write EBL is well-suited to support the shift toward purpose-built edge devices. As AI and edge computing converge to drive growth in the semiconductor industry, a nextgeneration direct-write lithography system will eliminate in-package bottlenecks and enable larger-scale integration of compact, low-power/high-functionality chiplets. In addition to enabling greater latitude to innovate, the new generation of directwrite EBL gives developers of new devices a faster, cost-effective route to market.

#### References

- M. Chen, J. Shen, "TSMC opens new advanced backend fab," Digitimes Asia, June 2023 https:// www.digitimes.com/news/ a20230608PD214/tsmc-3dfabricadvanced-packaging-testing.html

- D. Patel, "Advanced packaging part 1 – pad limited designs, breakdown of economic semiconductor scaling, heterogeneous compute, and chiplets," Dec. 2021 https://www. semianalysis.com/p/advancedpackaging-part-1-pad-limited

- 3. C. Sandstrom, R. Davis, B. San Jose, "Large-panel fan-out perspective on cost, yield, and capability," Chip Scale Review, p. 34, Nov/Dec 2022 https:// chipscalereview.com/wp-content/ uploads/flipbook/30/book.html

- 4. K. P. MacWilliams, A. C. Ceballos, T. A. Prescop, D. K. Lam, "High-productivity direct-write e-beam lithography: an enabling patterning technology to augment your lithography toolbox," SPIE Advanced Lithography, April 2023

https://www.spiedigitallibrary. org/conference-proceedingsof-spie/12497/1249705/Highproductivity-direct-writee-beam-lithography--anenabling/10.1117/12.2658237.short

K. Felton, "Slipping IC package design schedules and what to do about it," Chip Scale Review, p. 37, May/June 2023 https:// chipscalereview.com/wp-content/ uploads/flipbook/33/book.html

#### **Biographies**

11111

David K. Lam is founder, chairman & CEO of Multibeam Corporation in Santa Clara, CA, where he leads the development of Multicolumn Electron-Beam Lithography (MEBL) systems for semiconductor manufacturing. He is the founder and former CEO of Lam Research. Lam earned his PhD in Chemical Engineering from M.I.T. Email: dlam@MultibeamCorp.com

Ken MacWilliams is President and board member of Multibeam Corporation, Santa Clara, CA. He has helped develop and commercialize novel equipment platforms and processes for the world's leading semiconductor manufacturers, and held senior management positions at Applied Materials, Novellus Systems (acquired by Lam Research), Veeco, and Yield Engineering Systems (YES). He holds PhD and MS Electrical Engineering degrees from Stanford U.

## Transitioning from 3D packaging to 3D heterogeneous integration (3DHI)

By John Park, Vinod Kumar Khera [Cadence Design Systems]

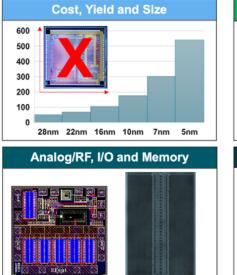

he semiconductor industry has been using scaling to keep up with the increasing demands of more functionality, higher integration, improved performance, and smaller footprints. With Moore's Law slowing down at advanced nodes, the industry is transitioning from "More Moore" to "More Than Moore" for the lower cost, larger design sizes and modularity benefits. Advanced packaging technologies and 3D heterogeneous integration (3DHI) are becoming more critical for enabling this transition; these technologies are evolving as the primary alternative to the traditional monolithic system-on-chip (SoC).

As the two worlds of system design and integrated circuit (IC) design are beginning to merge, new challenges for the complete ecosystem are being introduced—from electronic design automation (EDA) tool providers to package substrate designers and application-specific integrated circuit (ASIC)/SoC designers. This paper discusses some of these challenges and the EDA tool provider's perspective on this transition.

#### Introduction

As nonrecurring engineering (NRE) costs climb for advanced nodes, manufacturing size limitations are reached, and more I/O, analog/radio frequency (RF) designs are required. As a result, new form factors emerge, and solely relying on process shrink (Moore's Law) is no longer the best technical and economical path forward as shown in Figure 1.

It could be argued that reticle size limitations and the emergence of throughsilicon vias (TSVs) allowed semiconductor foundries to enter the world of multi-die packaging leading to the Moore-than-Moore era. A decade later, designers and manufacturers are beginning to realize the benefits of integrating some of the die in a vertical stack rather than building a single large monolithic SoC. This approach of 3D stacking can include dies, cores, memory, and more, to meet the needs of their next product. This technology, called 3D-IC, 3D heterogeneous integration (3DHI) or silicon stacking, promises many advantages over traditional singledie planar designs, such as lower costs and more modularity,

Figure 1: Moore's Law: economic and technical viability.

Integration in the vertical dimension/ silicon stacking technologies allows designers to potentially cram more functionality into smaller form factors while improving performance and reducing costs. Silicon stacking architectures can integrate multiple homogeneous and heterogeneous die/ chiplets, such as logic, memory, analog, and RF, into a single design. These heterogeneous, multi-chiplet architectures can provide a much lower-cost alternative to using advanced nodes (scaling).

### Trends in advanced semiconductor packaging

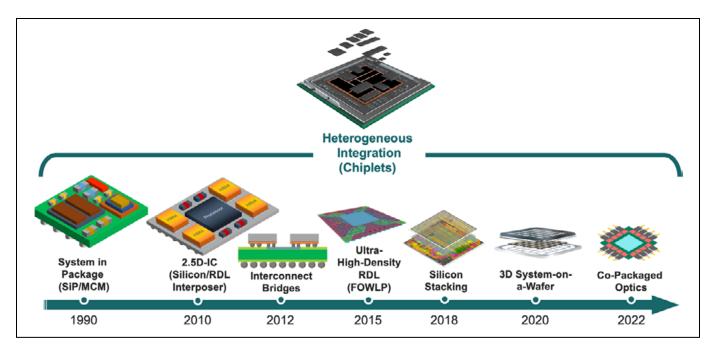

Semiconductor packaging engineers have been heterogeneously integrating die and designing 3D stacks for multiple decades. Typical examples are stacked and wire-bonded dynamic random access memories (DRAM) and package-onpackage (PoP) solutions. The industry used the terms multi-chip module (MCM) and a system in a package (SiP) to describe these architectures. Today, dozens of new packaging technologies support higher interconnect density and better electrical and thermal performance. Before discussing some of the newer packaging technologies, let's go back 30 years to the beginning of advanced packaging.

Advanced packaging started with single and multiple wire-bond and flipchip die on a printed circuit board (PCB)like laminate substrate called the ballgrid array (BGA). Build-up substrates came later, allowing smaller interconnect geometries. Interconnect bridges followed sometime near 2012. About the same time, TSV technology emerged, enabling silicon to be used as a high-density multi-chip(let) packaging platform. This technology is commonly referred to as 2.5D-IC packaging and is considered modern-day advanced packaging. This was when the semiconductor foundries began to offer "back-end" services, which

## **NEXT-GENERATION** SEMICONDUCTOR TESTING

## **DOT Test Platform**

The capabilities of two traditional testers, combined in a single, test-head-only system. A true zero-footprint solution, with 100% test efficiency.

Linear

Sensors

SerDes

(((၇)))

5G, IoT & Wireless

Medical

Discover how to save up to 90% on your Cost of Test www.spea.com/savewithDOT

SPEA S.p.A. Via Torino 16, 10088 Volpiano (TO) - Italy Tel. +39 011 982 5400

DOTBOO

#### Your trusted partner in IC testing

Figure 2: Heterogeneous integration leverages multiple packaging technologies.

were multi-die packaging using foundrybased manufacturing techniques. A few years later, foundries also started offering higher-density single-die packaging solutions ideally suited for the mobile communications market. Fan-out waferlevel packaging (FOWLP) wasn't new, but the ultra-high-density fan-out redistribution layer (RDL) provided smaller interconnect geometries than previous FOWLP solutions. These new foundry-based technologies created healthy competition and collaboration with the outsourced semiconductor assembly and test (OSAT) companies that had dominated packaging for 25 years.

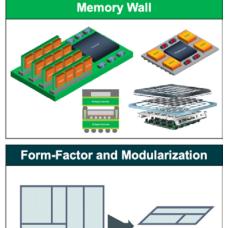

Over the past few years, a new vernacular has emerged based on a new set of acronyms – 3DHI, 3D-IC, and chiplets. This new vernacular primarily comes from semiconductor foundries and IC designers as they pivot from More Moore to the world of More-Than-Moore (3DHI). The sections below discuss specific challenges with 3DHI.

**3D** heterogeneous integration (**3DHI**). Heterogeneous integration is about the disaggregation of a chip into smaller building blocks, commonly called chiplets. It offers many benefits, such as: 1) Lower nonrecurring engineering (NRE) costs; 2) Shorter time to market (TTM); and 3) Flexibility and modularization benefits.

Heterogeneous integration is a term used to describe the disaggregation

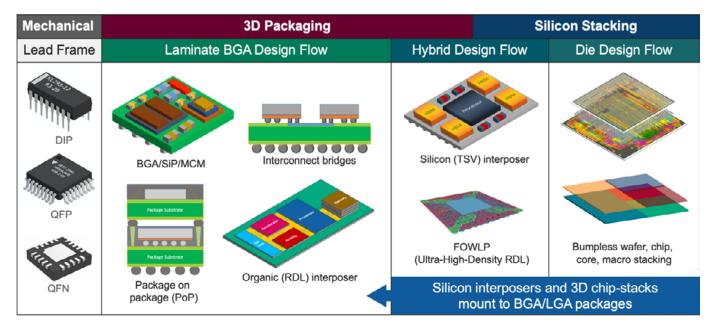

of an ASIC/SoC into smaller building blocks, each of which can be fabricated at whatever node or technology makes the most sense. Advanced packaging then becomes the process of aggregating all the building blocks (chiplets). And, of course, designers get to choose from dozens of packaging technologies (Figure 2). As discussed previously, semiconductor foundries started extending the back-end design services into silicon-based advanced packaging solutions a decade ago. The foundry-based approach of high-density interconnect geometries combined with TSVs paved the way for silicon interposers to emerge as the leading technology to aggregate and integrate multiple chiplets. But other packaging technologies might be starting to catch up. Most notable are RDL interposers, which don't require TSVs, thus lowering the cost

With advanced packaging as the primary technology for the next generation of electronic product design, it's crucial to understand the nuances between different packaging technologies. Packaging engineers have been designing organic/laminate substrates for three decades. The design flows and methodologies are well established. However, some interesting facts about today's foundry-based packaging technologies include:

- Convergence of the die design flows with the system design flows leads to questions about the expertise needed (die design or system design).

- ٠ While using bumpless stacking technology, in many cases, true chip-on-wafer and wafer-on-wafer applications are not packaging at all. Instead, it's die design except with the ability to now design in the vertical direction. This silicon stacking approach best suits the die designer with enhanced 3D capabilities in their place and route tool. In most cases, silicon stacking doesn't use chiplets in the traditional sense. Instead, a single register transfer level (RTL) gets partitioned in the third dimension, and in the case of face-to-face stacking, small 1-2um pads are used to connect the two levels. This differs from most chipletbased applications, which connect devices with micro I/O buffers, RDL, and micro-bumps using a die-todie (D2D) communication interface such as Unified Chiplet Interconnect Express (UCIe<sup>™</sup>) or bunch of wires (BoW).

- Finally, the combination of these two worlds is the hybrid scheme. Hybrid packaging technologies combine these two worlds (3D packaging and silicon stacking). 2.5D silicon interposer or ultra-high-density FOWLP requires tools and expertise spanning IC and

## We put **Advanced Packaging** to the test.

mkor

Amkor's advanced System in Package (SiP) solutions enable highly integrated products in a smaller footprint with higher component density and increased system performance. Innovative test solutions help deliver quality and reliability for all your advanced SiP packaging needs.

### Enabling the Future

© 2023 Amkor Technology, Inc. All Rights Reserved.

Figure 3: Packaging technologies.

system design. Figure 3 illustrates the different categories of multichip(let) packaging technologies.

Bottom line, 3DHI has its caveats, such as: 1) The design does not get easier with heterogeneous integration and gets more complicated; 2) Moving from a single monolithic SoC to a system-level architecture reintroduces considerations that SoCs effectively counteracted, such as thermal, electrical, and mechanical stresses; and 3) The correct tools, methodologies, and team collaboration approaches must be implemented before designing a heterogeneous integration chip.

#### **Challenges for 3DHI**

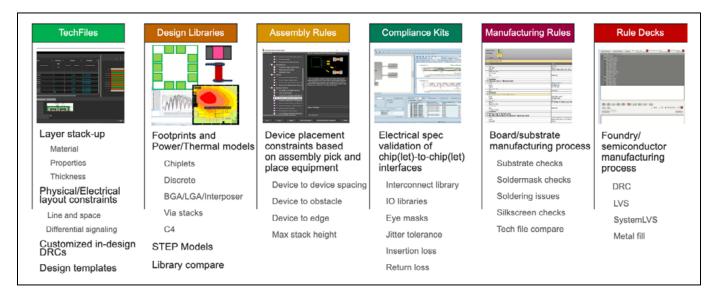

As discussed above, 3DHI offers many benefits over monolithic IC design. However, as with most emerging technologies, several challenges must be overcome—starting with the minimal availability of assembly design kits (ADKs) (Figure 4). Some of the primary design challenges for 3DHI are discussed in the sections below.

Lack of package ADKs. PDKs provide the necessary information to start the design in ASIC/SoCs, but there is a lack of such data to start the package design as we transition to the world of 3DHI. Existing ADKs are focused on the rule deck and lack the design libraries for packaging. Starting a new design without a PDK is another hurdle for IC designs to jump.

Commercialization and standardization. Commercialization and standardization of chiplets are two more major challenges. This is because most chiplet-based designs today are in a closed ecosystem of vertically-integrated companies. While much progress has been made with standards such as UCIe<sup>TM</sup>, BoW, chiplet design exchange (CDX) and TSMCs 3Dblox<sup>TM</sup>, we have ways to define a business model that makes sense for turning silicon intellectual property (IP) into chiplet form for the general market.

Figure 4: Package assembly design kits (ADKs).

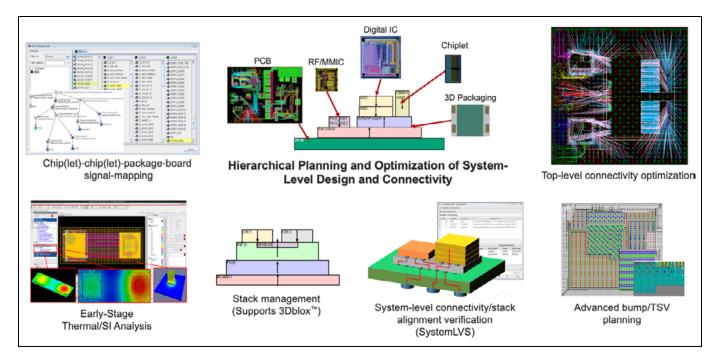

Figure 5: Requirements for EDA tools.

It may be 3-5 more years before we have a catalog of known-good chiplets from which to choose like what is available to printed circuit board (PCB) designers.

#### **3DHI challenges for the package** designers

Package designers face new challenges while pivoting to ultra-high-density foundry-based packaging technologies. A massive change for most package designs is the design verification step. Further, they face many other challenges, such as:

- Sign-off design rule check (DRC) and layout vs. schematic (LVS) are standard practices when designing something for a foundry-based manufacturing process. Today, most package substrate designers use a much less formal process of validating their design from a DRC, LVS and assembly perspective (see previous discussion re: ADK).

- Lack of a formal SystemLVS methodology to validate the alignment and connectivity through the multiple levels of a 3D heterogeneously-integrated package.

- Pre- and post-route chipletto-chiplet signal integrity and compliance issues have become a new requirement for most substrate designers focused on single-die packaging. In single-die packages,

electromagnetic (EM) extraction tools are used to generate the pin parasitics of a package. In multichip(let) designs, the electrical compliance between the devices requires signal integrity expertise.

#### **3DHI challenges for ASIC/SoC** designers

There are a number of 3DHI challenges that face ASIC/SoC designers such as:

- A top-level planning methodology needs to be established for planning and optimizing the interconnect (netlist) for the system-level design across multiple chiplets and packaging tiers.

- Robust co-design with the package substrate design team is paramount. The over-the-wall approach of the past may lead to increased final product cost, or worse.

- Pre-place and route thermal analysis capabilities to determine the best 2D and 3D chiplet placement to meet thermal budgets long before detailed implementation.

- On-the-fly die splitting and repartitioning in the third dimension, potentially across different design nodes, requires a design tool that works concurrently with multiple PDKs or tech library exchange formats (LEFs) in a single layout session.

#### EDA tools perspective

From the EDA tool provider's perspective, it is essential to develop cross-domain design flows that provide a platform to the user for designing multichiplet-based packages from a single logical hierarchical representation to a multi-chiplet-design (from the transistor level to the full system level) (Figure 5). The existing die design tools need extensive enhancements to support 3DHI architectures and help design and analyze from the system perspective. The increasing complexity because of the rising number of design tools as we transition from monolithic SoC to 3D-IC demand EDA tools with capabilities such as:

- Place and route tools must be extended to support multiple PDKs;

- The tool database must also be extended to support structures such as silicon vias, TSVs, bumps, backside metal, and more;

- Scalability to handle increasing instances and routing interconnect styles;

- · Pre-place and route and heat/thermal analysis;

- Automated optimized TSV placement solutions and routers to connect multi-die in a stack;

- Additional capability for digital signoffs, such as:

- o Static timing analysis (STA) with automated corner reduction; and

- Rule-deck-free SystemLVS for 3D package-level alignment and connectivity checking.

- Comprehensive thermal stress and design for manufacturability (DFM) tools for chemical mechanical polishing (CMP) planarity checks across the dies.

These tools should allow the designer to aggregate the chiplets and packaging technologies to plan and optimize the toplevel design. Apart from this, the tools should have the ability to work at very abstract levels of the design to make designers capable of performing early-stage analysis of the 3DHI.

Additionally, next-generation design flows need to move more analysis further upstream in the design process. EDA technologists have used the term "shift-left" to describe moving electrical analysis into the layout tools, but for 3DHI, the analysis tools need to be shifted further left into the design planning stage. Thermal analysis, for example, must be performed as early as possible when considering stacking silicon.

#### **Summary**

As we advance with 3DHI, design methodologies are becoming even more complex. Companies willing to invest in their design flows will have a competitive edge. As the domains of die and system design converge, many new challenges await ASIC and package designers entering the world of "Moore-than-Moore." An integrated design methodology across IC, package, and board design, along with analysis and verification moved further upstream in the flow, will be vital in enabling designers to focus on design work, not design tools. Seamless integration across the tools will significantly reduce design cycle times and enable codesign and co-analysis across IC, package, and PCB domains.

## Bringing tomorrow's electronics to life

mrsisystems.com

#### **Biographies**

John Park is Product Management Group Director for Advanced Semiconductor Packaging at Cadence Design Systems, Louisville, CO, where he leads a team responsible for defining cross-domain solutions and methodologies for IC, package, and PCB co-design and analysis. His team is especially focused on developing tools and flows for chiplet-based 3D designs. He has over 40 years of experience in the EDA field and is regarded as an international expert on chiplets, packaging, and heterogeneous integration. Email jpark@cadence.com

Vinod Kumar is Lead Marketing Communications at Cadence Design Systems, India. He received a PhD in VLSI from NIT, Kurukshetra, India. Vinod has worked in the semiconductor industry for over 12 years in the domain of VLSI and embedded systems design.

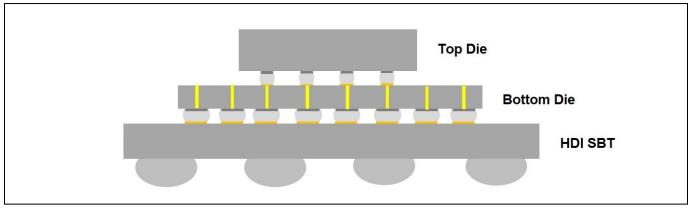

### LEADING FIRST-LEVEL INTERCONNECT SOLUTION FOR HETEROGENEOUS INTEGRATION

## Heterogeneous integration of chiplets technology enabled by advanced package architectures, first-level interconnect

By Nelson Fan, Eric Ng [ASMPT Limited]

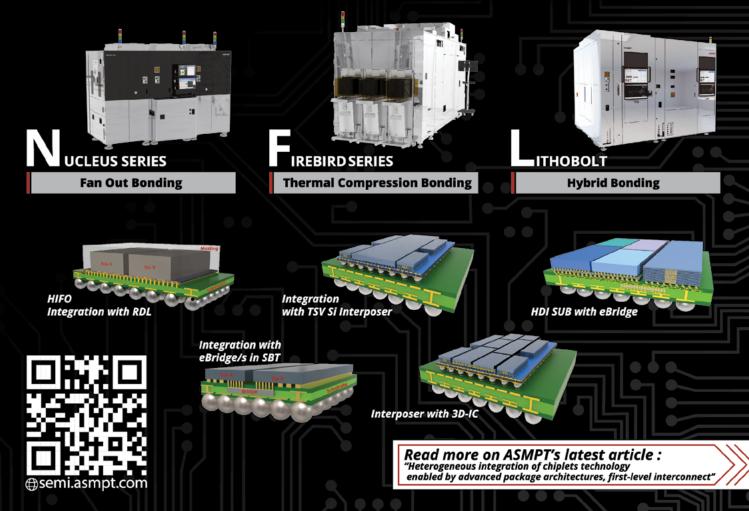

hile leading semiconductor companies continue to develop complementary metal-oxide semiconductor (CMOS) scaling under the driving forces of highperformance computing (HPC) and artificial intelligence (AI) applications, "More than Moore" has been successfully demonstrated through the heterogeneous integration of chiplets (HIC) in various advanced package architectures, together with advanced first-level interconnect (FLI) technologies (Figure 1). The objective of developing advanced package architecture is to deliver the same or even better device performance as a system-on-chip (SoC) format while achieving the best cost of production.

#### **FLI process mapping**

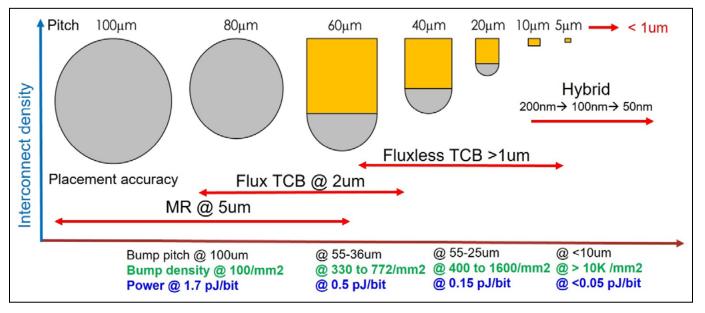

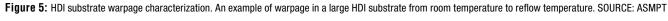

Although CMOS scaling is continuing to progress at a slower pace, the focus is now on creating chiplets with higher density and I/O counts at a finer pitch (down to sub-micron pitch level) resulting in smaller bump sizes, rather than using SoCs. The HIC approach is being deployed to mitigate the economic effects of expensive nodes. To achieve the required performance, a very high degree of chiplets placement accuracy in a heterogeneously-integrated (HI) device is being scaled up, and more advanced FLI interconnect processes are being developed. From traditional mass reflow flip chip (MR-FC) and thermal compression bonding (TCB) at 5µm and 2µm placement accuracy respectively, the technology is now evolving towards fluxless thermal compression bonding with bond accuracy of less than 1µm to handle the very high bump density with pitches less than 10µm. Although the ultimate device performance can be enabled by the copper-to-copper connection through the hybrid bonding process, the cost of ownership can currently only be borne by devices with a very high average selling price (ASP). That being said, hybrid bond technology is continuously being developed to target devices with higher density, better yield, and an affordable cost of ownership for high-volume manufacturing (HVM) in the near future.

#### Various HI package architectures

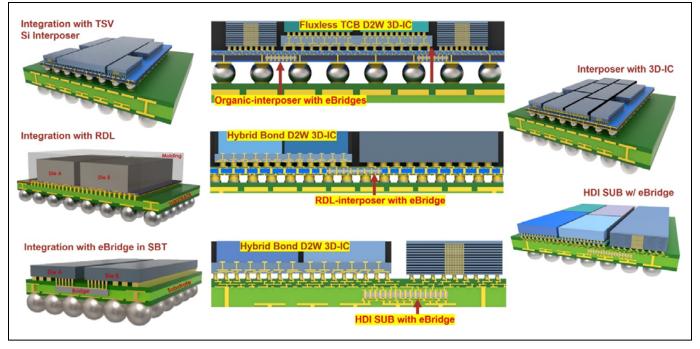

Over the last decade, various HI package architectures have been developed by the technology frontrunners including wafer foundries, integrated device manufacturers (IDMs), outsourced semiconductor assembly and test suppliers (OSATs), and advanced substrate houses (Figure 2). These HI package architectures can be classified into three major basic categories: 1) with a through-silicon via (TSV) interposer; 2) with a redistribution layer (RDL) interposer; and 3) with single and/ or multiple embedded silicon bridges (e-bridge) inside the high-density buildup interconnect (HDI) substrate.

Among the three categories mentioned above, the TSV interposer offers the best routing capability with the finest line width and spacing at the submicron scale of wafer fabrication feature size. However, it is the most expensive type and is also limited by its 300mm diameter manufacturing format. The number of interposers will be very much limited per 300mm diameter format,

Figure 1: First-level interconnect (FLI) process mapping.

Figure 2: Various heterogeneous integration (HI) package architectures at a glance. SOURCE: ASMPT

particularly if the interposer size is continuously growing (said to be more than 4 reticle sizes to support a larger degree of integration).

A HDI substrate with e-bridge has been developed as another way to integrate multiple chiplets without facing the interposer manufacturing format size limitation. It makes use of single or multiple pieces of a smaller Si bridge fabricated with fine line width and spacing capability to partially connect two chiplets at the location designed for die-to-die communication. Because the e-bridge is embedded precisely onto the target location of the high-density build-up (HDBU) substrate as part of the manufacturing process, the associated challenges are the final substrate yield related to the induced top substrate top surface planarity, open/short continuity, and warpage, among others.

The RDL interposer has been developed to provide the most costeffective way for integration. Various versions can support a die-first or dielast approach depending on the process capability and device performance requirement. Recently, silicon bridges have been embedded into the RDL interposer to further improve the integration capability and to enhance the power and signal integrity of integrated device performance requirements.

#### Continuous advancement of the TCB process

TCB is one of the most advanced FLI methods. Although it has been developed and deployed for more than a decade, it is continuously being adopted for new applications (Figure 3). The most recent adoption is for the nextgeneration high-bandwidth memory (HBM). Flux-TCB has been qualified for HBM as the HVM process up to 12 layers, with proven capability to maintain the tight control die-to-die gap height for all the layers (Figures 4-6). The next-generation HBM is required by the latest HPC and AI devices to meet the performance requirements.

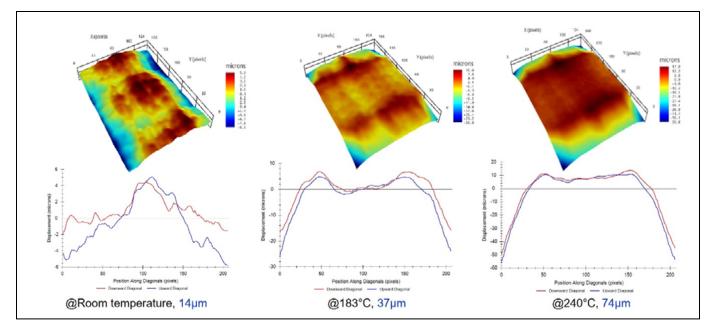

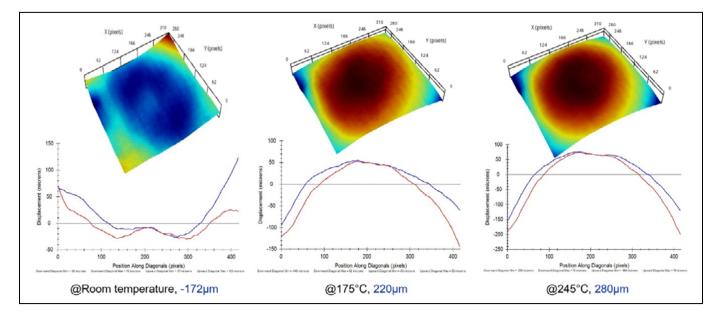

Another example of new HVM deployment of the TCB process is for extra-large HI die interconnection to the HDI substrate (Figure 7). As the HI die is becoming larger (larger than 6 reticles in the area), with reduced bump pitch and complicated die layout, coupled with the extra-large HDI substrate (easily 2x larger in the area), the traditional mass reflow flipchip (MR-FC) process becomes impossible. The next-generation TCB bonder, with extra-large HI die handling capability, as well as the sophisticated bond head heater and bond stage design, enables dynamic warpage control for both HI die and HDI substrate during solder joint formation, and is now the new process of record (POR).

Figure 3: Cross-section of the next-generation HBM with flux-TCB.

### smiths interconnect

## **Kepler Test Socket**

High performance scrub contact technology for IC Testing

Whether for testing high performance computing, wearables and other automotive chips, Kepler is the only solution that provides two-axis of motion during a single actuation of the socket. As a result, Kepler provides a boosted first pass yield, enhanced production reliability, and extended maintenance intervals.

- Long contact life, low wear, tested to over 500K insertions

- Provides reliable and consistent contact for Matte Tin or NiPdAu pads, low contact resistance (CRES)

- Exceptional signal integrity

- Covers wide range of test applications

- Match existing PCB socket footprint and test hardware lead to cost saving for customers

- Field repairable, easy cleaning and maintenance

- Low Dielectric constant, Low CLTE, exceptional Flexural Modulus

- Allows for PCB topside components to be placed close to DUT for better signal performance and less signal loss

High Performance Computing

Automotive

Data Centers

KOSDAD CE 🐽 G

## **iPIS Product Family**

#### **iPIS-HX Series**

#### HIGH DETECTABILITY HEXA PLATFORM

Premium Solution of Supporting 6 Sides Inspection (Top/Bottom 2D/3D, 4 Side)

High Detectability for Advanced Package Inspection (SiP, CIS ... )

Support Advanced Inspection Options: Real Total Height (Top 3D), Top Side Dent, Side LFF Stitching, Multi Picker and Deep Learning

#### **iPIS-XTR Series**

EXTENDABILITY TR PLATFORM

All-in-one Inspection Solution with 3 Rail for 6 Side + Tape & Reel

Cost-effective Upgrades which enable to extend Equipment Lifecycle

> Maximized Extension Capability

Selective Inspection Available for Customer Inspection Needs (Advanced Package, Side Inspection)

#### **iPIS-IN Series**

IN-TRAY PLATFORM INSTANT INSPECTION

World Best Productivity Supporting In-tray Handling method with 5 Rail Based Platform

Minimize the Handling Damage with Tray Flipping Technology

Stable Handling with Precise Stitching for Large Package

Option: HX Platform, Tape & Reel

X140TR, X240TR, X34OTR

#### INTEKPLUS CO., LTD.

#263, Techno 2-ro, Yuseong-Gu, Daejeon, 34026 Korea Tel : +82-42-930-9900 Fax : +82-42-930-9999 For more information www.intekplus.com / sales1@intekplus.com

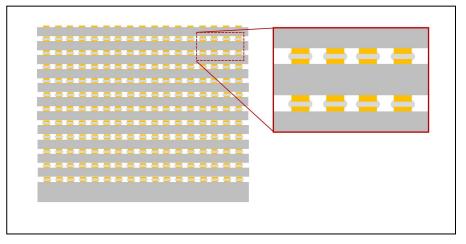

Figure 4: HI die warpage characterization. An example of warpage in large compound HI dies from room temperature to reflow temperature. SOURCE: ASMPT

Figure 6: HI packaging architecture associated challenges and solutions with ASMPT home-built TV with 70 x 70 integrated die size.

TCB bonder manufacturers continue their development efforts to enable the emerging fluxless-TCB process, which is an alternative process to very expensive and yet HVM immature hybrid bonding (HB) technology. Recent development work has shown robust bonding capability for micro bump devices with fine bump pitch at less than  $15\mu$ m (**Figure 8**). The test vehicle, in the form of a 3D structure bonded by the fluxless-TCB process, has also passed the reliability stress test up to 1000 cycles of thermal cycling, as well as 1000 hours of

| Fan-out                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Die Warpage                | RT<br>250°C<br>• Bond head design<br>• Heater design<br>• Collet design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Solder Height<br>Variation | Die bump (5 µm variation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Good Solder<br>Joint       | LocationLeftMiddleRightCut_1Image: Sold in the second seco |  |  |  |

Figure 7: Challenges for extra-large HI die bonding. SOURCE: ASMPT

Figure 8: Fine-pitch micro bumps with fluxless-TCB. SOURCE: ASMPT

Figure 9: Fluxless bonding for 2-layer stack packages. SOURCE: ASMPT

# adeia

Adeia turns ideas into innovations

Our name may be new, but our roots run deep with decades of continued innovation. We invent, develop and license innovations that advance how we live, work and play.

## Adeia invented and pioneered Direct and Hybrid Bonding

## DBI<sup>®</sup> Ultra

Die-to-Wafer Hybrid Bonding

## DBI®

Wafer-to-Wafer Hybrid Bonding

## **ZiBond**®

Wafer-to-Wafer Direct Bonding

Better Ideas. Better Entertainment.

adeia.com

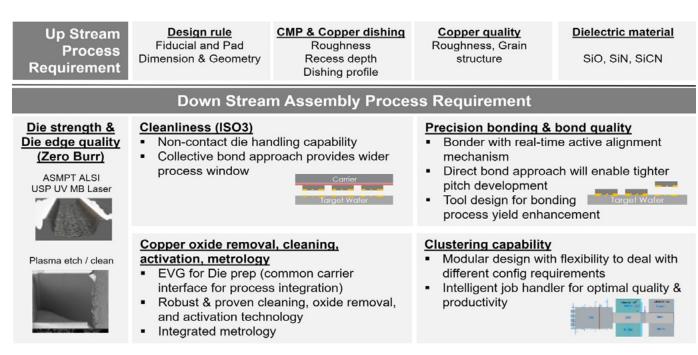

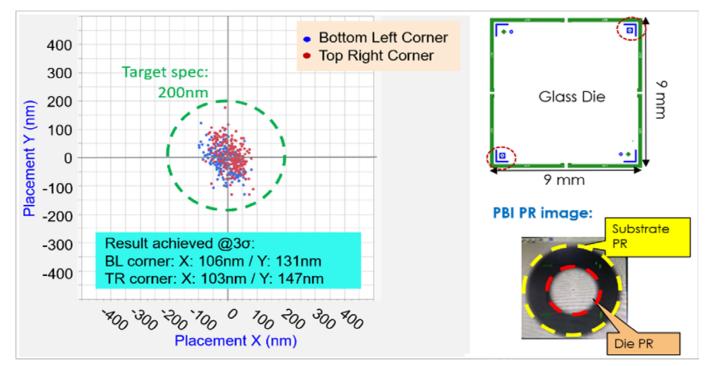

Figure 10: Key challenges and solutions in D2W hybrid bonding.

the resultant solder joint not reliable under stress conditions. A copper-to-copper joint is likely the way to go. While the I/O pad pitch is getting so small, the die gap-filling process will be impossible if it follows the approach of conducting a post-bond underfill process. Bonding the dielectric simultaneously together with the copperto-copper I/O bonding that makes a hybrid bonding process is the most probable way. Hybrid bonding (HB) for HI devices with chiplets integration is an emerging FLI process that requires very different upstream design and process requirements such as chiplets design rules, choice of dielectric material, copper I/O pad plating chemistry, as well as chemical mechanical polishing (CMP) and copper pad dishing (**Figure 10**). It is targeted for devices with I/O pitch at the sub-micron level. Tool makers have already made HB bonders to meet the high-precision alignment accuracy at 200nm (Figure 11). Besides high-precision alignment, a very clean environment to enable a die-to-wafer faceto-face bonding process is also required, with almost zero tolerance for foreign particles. Therefore, bonder cleanliness capability is required to meet ISO 3 specifications, the same as for front-end

Figure 11: Alignment accuracy verification test based on COG (chip-on-glass) done on an ASMPT LithoBolt Bonder showed that a <200nm result has been achieved.

equipment. The bonder is also being put inside the front-end condition to ensure cleanliness. This is a very costly operation compared to running in a traditional backend assembly clean room. To ensure a successful bond with good yield, not only are cleaning and activation of the chiplets and target wafer needed to be done by the material preparation tool critical, but queue time control and cleanliness are also vital. Integration of the material preparation tool and multiple bonders is being advocated, which will induce a "line balancing" issue. The situation will be further complicated if the number of chiplet types increases. All these issues incur additional costs compared with other devices running in HVM mode with TCB and mass reflow (MR) processes.

To fully bring up the merit of HB technology for next-generation chipletsintegrated HI devices in a much more cost-effective way, and enable it for more applications than just very highend devices, new development efforts are being undertaken.

#### **Summary**

The rise of the HPC and AI era exerts increasing demand for performance advancement of computational devices. With front-end node technology continuing to evolve, advanced packaging technology is making corresponding progressive developments. Both advanced TCB and HB are promising FLI processes to enable heterogeneous integration and chiplets applications for our industry. Reaching HVM at a reasonable cost of ownership for advanced packaging technology requires not only the effort of equipment manufacturers to develop equipment capabilities, but also close collaboration with the user to fully understand design requirements, associated material technology, as well as manufacturing conditions.

### LEADERS IN MICRO DISPENSING TECHNOLOGY

SMALL REPEATABLE VOLUMES ARE A CHALLENGE, BUT NOT IMPOSSIBLE IF YOU HAVE BEEN CREATING THEM AS LONG AS WE HAVE.

#### TO DO IT WELL, WE PROVIDE THREE THINGS:

**Dispensing Expertise** in a variety of microelectronic packaging applications.

**Feasibility Testing & Process Verification** based on years of product engineering, material flow testing and software control.

**Product Development** for patented valves, dispensing cartridges, needles, and accessories.

Our Micro Dispensing product line is proven and trusted by manufacturers in semiconductor, electronics assembly, medical device and electro-mechanical assembly the world over.

www.dltechnology.com.

216 River Street, Haverhill, MA 01832 • P: 978.374.6451 • F: 978.372.4889 • info@dltechnology.com

#### **Biographies**

Nelson Fan is the VP of Business Development in Advanced Packaging Technology (APT), SEMI Solutions at ASMPT Limited, Hong Kong. With more than 30 years of experience in the semiconductor industry, he has been positioned in different senior engineering roles in package and process development as well as in manufacturing operations. He holds more than 40 US patents in semiconductor packaging technologies. Email: chfan@asmpt.com

Eric NG is the Business Development Manager for Advanced Packaging Technology (APT) at ASMPT Limited, Hong Kong. With over 20 years of experience in the semiconductor industry, he has held various roles in product and process development, research and development, sales, and business development. He has worked in different fields such as IC packaging, FPC manufacturing, phase-change temperature control devices, and HDD manufacturing.

### Parallel validation strategies minimize debug time and ensure sufficient test coverage

By Adir Zonta [Advantest]

est data volumes are exploding as the number of transistors per chip increases along with the number of test vectors needed to test each transistor. A recent article [1] provided an overview of how the device validation and characterization, structural and functional test at automated test equipment (ATE), and system-level test have evolved over the years to deal with ever-increasing complexity. The author [1] described how traditional methods no longer suffice and introduced innovations in pre-silicon verification, first silicon bring-up, and post-silicon validation (PSV) that are necessary to meet today's challenges. This article provides more details on these recent innovations and the systems necessary to implement them, including information on how to equip an engineering lab with automated parallel test stations to speed up test engineering tasks such as pattern validation. In addition, it describes how a new standard helps bridge the gap between the electronic design automation (EDA) and ATE domains and how an EDA company and an ATE maker have collaborated on an initiative to put the standard into practice.

#### **Test-pattern validation**

One of the challenges that the explosion in test data imposes on test engineering is the ever-lengthening time required for test-pattern validation, which is impacting time to market. Testpattern validation determines whether the patterns are generated correctly, that the expected responses are accurate, and that they have enough margin to account for parameter variations (for example, in voltage and frequency) in production.

#### Generating test patterns

The test patterns include structural scan patterns generated by automatic test-pattern generators or functional test patterns generated manually from a test specification or automatically using random or constraint-based testgeneration methods or other techniques linked with EDA tools. Test patterns from the EDA tools are generally in a standard format such as STIL (Standard Test Interface Language) or WGL (Waveform Generation Language). Structural test patterns target specific fault models, such as "stuck at" faults or timing faults, whereas functional test patterns aim to come closer to confirming the device under test's (DUT) performance in its end use. The need for functional test vectors is particularly important in automotive and other industries where performance and safety are critical. The following sections discuss aspects of generating test patterns.

**Cyclized test vectors.** The patterns in STIL or WGL from the EDA tools must be converted to cyclized test vectors for the target ATE system. The cyclization process involves adding timing and control information to synchronize the patterns with a specific ATE system's clock and control signals, which can require extensive development time.

**Error causes.** Inevitably, errors will appear in the cyclized test vectors. These errors could result from design defects that percolated through the cyclization process, or they may have resulted from the cyclization process itself, or they may result from corner cases that the original design did not take into account. Whatever the reason, the PSV process must identify them and correct any errors.

**Correcting test-pattern errors.** When errors are detected during the pattern validation process, they must be corrected through manual or a combination of manual and automated methods. Engineers can manually review test patterns to identify errors, analyze failing test patterns, examine response traces, perform debugging and diagnosis, and modify the stimulus pattern, the expected response pattern, or both. Alternatively, automated tools can analyze failing test patterns and generate reports making recommendations for correcting errors based on predefined rules.

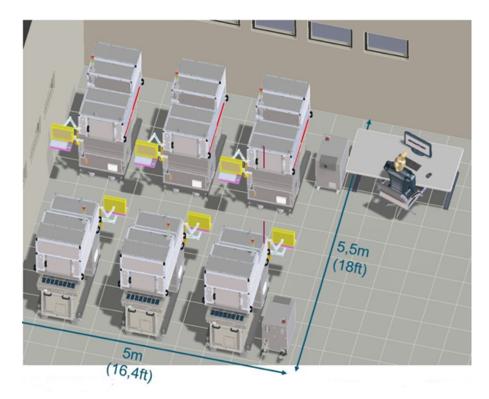

### Using automated parallel test stations to speed up the process

With or without automation, the process discussed above is timeconsuming. Speeding up the process requires a test lab with the equipment necessary to run parallel pattern validation, thereby minimizing the time spent on pattern debugging while assuring sufficient test coverage. A solution such as the Advantest V93000 EXA Scale EX Test Station, an engineering platform for complex device bring-up that supports structural and functional test, provides such parallel test capability without requiring a lot of floor space because it is designed to fit under the company's single-site M4171 automated handler. Complete with integrated active thermal control (ATC) over a -45 to +125°C range, the handler brings automated device loading, unloading, and binning into the laboratory environment. As shown in Figure 1, six test cells can fit within a 5m by 5.5m laboratory space.

#### Bridging pre-silicon verification and post-silicon

An engineering lab with automated, parallel test stations can significantly enhance the test engineering process where the typical test content is dominated by structural test. However, while the structural test is the foundation for systematic test coverage according to targeted fault models, there is a growing need for functional tests to reach high-volume readiness.

Figure 1: Six EX Test Stations with M4127 handlers fitting within a 5m by 5.5m laboratory space to speed up test-pattern validation and other engineering tasks.

Accordingly, there is a trend for an increasing amount of functional tests.

The challenges involved in creating functional test on ATE can be summarized in two major categories. First, the need to convert the functional test content into a production test vector pattern requires tooling and extensive development time. Second, on a typical ATE, there is no native software debugging environment, making it very difficult for the test case developer to debug any issues in support of the test engineer. Excessively long, unpredictable debug cycles are inevitable. That is where pre-silicon methodologies and an ATE instrument can work together to seamlessly and interactively validate the functional test content to help to meet these challenges.

#### Introducing the PSS standard

The transition from the pre-silicon verification stage to first silicon involving bring-up, bare-metal test execution, and the ATE stage—can be greatly smoothed through the reuse of pre-silicon verification test content. To that end, the Accellera Systems Initiative, an organization focused on the creation and adoption of EDA and intellectual property (IP) standards, has promulgated the Portable Test and Stimulus Standard (PSS), which specifies a single representation of stimulus and test scenarios that span simulation, emulation, and post-silicon [2].

### Linking the EDA and ATE communities

A result of PSS is that the oncesiloed disciplines of the EDA and ATE communities can work together. Barriers remain, however. Structural test dominates the ATE side, but rising quality expectations are driving a need for more functional test to ensure the chip will perform properly in its end application environment or mission mode. However, as previously mentioned, converting functional test content into production test vectors requires extensive development time, and a typical ATE system lacks a native software debugging environment that could speed up the process [3].

#### Proposed solutions to handling functional test content

A solution would involve meeting one or more of the following requirements: 1) seamless software-driven execution of unconverted functional test content on the ATE; 2) ATE hardware that supports high-speed I/O (HSIO) communication; 3) enhanced functional coverage closure using constraint random test content; 4) a native software debugging environment instead of vector-pattern compare and error reporting; 5) or an enhanced PSS scenario analysis to observe how varying test conditions impact PSV.

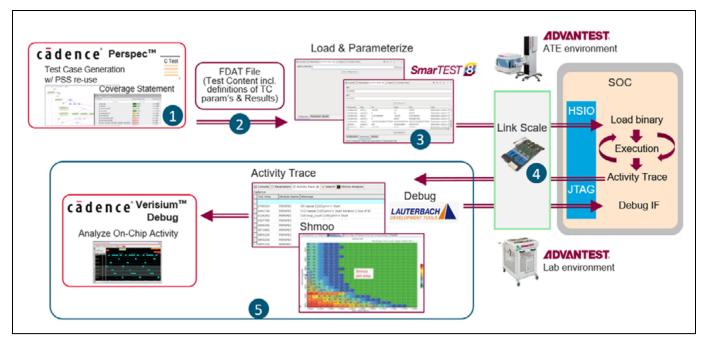

#### **PSS** implementation

A joint cooperative initiative between Cadence and Advantest involved a combination of the PSS and HSIO approaches. The companies have developed a solution that involves PSS-based test content creation, an interface to ATE software, the loading of parameterized test content, test execution on ATE hardware, and debug and analysis (Figure 2). The solution begins with the Cadence Perspec System Verifier, which automates the process of extending the PSS models used in pre-silicon validation to the ATE environment, reducing the complex use-case scenario development time. A container file labeled FDAT in Figure 2 provides an efficient interface between Perspec and the Advantest SmarTest 8 software for its V93000 ATE systems.

### Interacting natively with DUT with no cyclization

Continuing with the process noted in the previous section, Advantest's new Link Scale ATE instrument interacts natively with the DUT using low pin-count HSIO, such as USB and PCI Express interfaces running in full-protocol mode, without pattern cyclization. Collected test traces can be viewed in a SmarTest viewer or imported into Cadence's Verisium Debug AI-powered debug tool for correlation with the original PSS tests. In addition, Link Scale can host embedded software debuggers such as the Lauterbach TRACE32.

#### **Device validation best practices**

The process outlined in **Figure 2** can significantly ease the burden of the postsilicon activities but not eliminate it. Not all DUTs will have HSIO channels for the delivery of test patterns without the necessity of converting them to cyclized test vectors, or not all functions

## **Global No.1! Total Test Solution Provider!**

#### **BURN-IN SOCKET SOLUTIONS**

#### No ball damage

- Direct inserting on Burn In Board without soldering No damage on Burn In Board land

- Simple structure without sub PCB & easy maintenance

#### POGO SOCKET SOLUTIONS

#### · Various design available

- Excellent gap control & long lifespan

- · High bandwidth & low contact resistance

- Adjustable Impedance

- Fully Metal Shielding

#### Hi-fix & Burn In Board

- · High performance and competitive price

- Test fine pitch, high speed device at hot & cold temperature

- Customized design to meet individual requirements

High performance and competitive prices

- · High speed & RF device capability

- No load board pad damage & no contact trace on the ball

- · Customized design to meet challenging budget constraints

- Full thermal and electrical simulation

#### **ISC Connector**

- · ISC Connector Solutions solve many problems across a wide range of circuit sizes, configurations, pitch, and PCB-attach terminations.

- · Designed to have the strong resistance against torque forces on mating area to achieve the high reliability in the natural fall shock.

#### THERMAL CONTROL UNIT

- Extreme active temperature control

- · Customized design to meet challenging requirements

- Price competitiveness through self designing and fabrication

- · Safety auto shut down temperature monitoring of the device & thermal control unit • Full FEA analysis for strength, deflection, air flow and any other critical requirements

**ISC** International Siliconvalley, CA

Tel: +82 31 777 7675 / Fax : +82 31 777 7699 Email:sales@isc21.kr / Website: www.isc21.kr

Figure 2: PSS enables the interfacing of EDA and ATE domains.

of a DUT with HSIO will be able to be accessible to test instruments through HSIO ports in mission mode. Consequently, the need will remain and even grow for engineering test laboratories populated by automated, parallel single-site test stations.

Going forward, one key will be smoothing the transition from the lab environment with engineering test stations to the production floor. One example is the single load board strategy, in which a multisite load board for high-volume production can be used in the lab with only a single site enabled, making it unnecessary to develop one board for engineering activities and another for high-volume manufacturing (HVM). The engineering environment should be as close as possible to the HVM environment, and the EX Test Station achieves this goal because it uses our Xtreme Link technology. The station is also suitable for testing initial engineering batches efficiently.

#### Summary

The semiconductor industry has a long and successful history of testing increasingly complex devices, continually enhancing structural, functional, and system-level test to minimize test escapes. Advances continue as the industry contends with an exploding amount of test data necessary for silicon bring-up, PSV, and other test engineering tasks. A key innovation is a laboratory equipped with engineering workstations that can operate in parallel to speed up tasks such as pattern validation. In addition, EDA and ATE companies are cooperating to leverage standards such as PSS to bridge the pre- and post-silicon verification stages, and they are leveraging HSIO to allow ATE to apply test patterns without cyclization. Finally, engineering workstations are incorporating the loadboard, compute, and communications technologies of production ATE systems, thereby speeding the transition from the lab to HVM.

#### References

- 1. D. Armstrong, "Device validation: the ultimate test frontier," *Chip Scale Review*, Nov-Dec. 2022, p. 26.

- 2. "Accellera Board Approves Portable Test and Stimulus Standard 2.0," Accellera Systems Initiative, April 14, 2021.

- 3. M. Rubin, A. Zonta, "Pre and Post-Silicon Verification Have Never Been Closer! Leveraging Portable Stimulus for Automatic Test Equipment (ATE)," Cadence Design Systems Inc., May 4, 2023.

#### Biography

Adir Zonta is Product Marketing Manager for V93000 Engineering Solutions at Advantest, Boeblingen-Germany. Adir has 19 years of cross-industry expertise in developing cutting-edge solutions and expanding product portfolios across the value chain. He has a MS degree in Mechanical Engineering from the Federal U. of Santa Catarina (UFSC) - Brazil. Email adir.zonta@advantest.com

# GUEST EDITORIAL

### Foundry 2.0: A renaissance in innovation

By Bob Patti [NHanced Semiconductors]

ur society craves customization. We all want clothing, cars, and phones that fit us and our personal usage styles.

In semiconductor hardware, however, customization has become prohibitive. How did the industry get here? What can be done to revive innovation in highend chips? This article discusses a new business model called Foundry 2.0.

#### **Remembering the "Golden Age"**

The 1980s and 1990s saw a golden era of custom integrated circuits (ICs). New gate arrays, or even standard cell custom devices, were relatively inexpensive. A startup company could develop a new chip and go to market for 10 or 20 million dollars. New devices and intellectual property (IP) thrived in the market. Individual companies developed and tuned their own semiconductor products. Moore's Law was in full swing and roomfuls of 1970s electronics became desktops, laptops, tablets, and personal digital assistants (PDAs).

#### The rise of the SoC

Since the "Golden Age," transistors have shrunk from 1µm to 2nm while wafers grew from 200mm to 300mm, providing more dies per wafer and vastly

more transistors per die. Cell phones now routinely outperform the personal computers (PCs) of the 1990s. Key to this progression was bundling ever larger groups of functions into system on chip (SoC) devices to reduce cost, power, and size. These improvements were largely enabled by reduction in wire size and length. Cumbersome chip-to-chip wiring and electrostatic discharge (ESD) structures were replaced by elegant onchip communication. Today's one-sizefits-all SoCs are the result.

However, progress on the path described above has slowed to a crawl. Absorbing more features into an SoC no longer translates reliably into cost, power, and size improvements. Why? Because advances in wiring have fallen far behind advances in transistors.

Wiring limitations are imposed by the limits of process technology and by basic physics. Today's wires are too small to be made with smooth edges; the structures look as if they were drawn with a crayon. Electrons bounce and scatter off these ragged edges, seriously impacting signal speed. At the same time, scaling draws wires closer together and they become more resistive. Wire proximity also adds to capacitance and, therefore, energy consumption. For all of these reasons, wires consume most of the power and most of the delay at very small nodes; transistors take a tiny portion of both budgets. Wires are the root of the problem with continued scaling.

#### The current business model: Foundry 1.0

As feature sizes have shrunk, development and factory costs have risen to staggering heights. Stark economic realities force today's fabs to echo Henry Ford's famous quote, "Any color the customer wants, as long as it is black." Certainly, software provides a level of customization, but hardware inflexibility requires that customers shoe-horn big field-programmable gate arrays (FPGAs) or multi-function SoCs into their applications. These one-size-fits-all chips provide workable solutions, but they typically contain millions of transistors that the application doesn't need and never uses. They take up more space, consume more power, and run more slowly than a sleek, well-tuned custom chip.

Today, IC development costs range into the billions. Developers are scarce and are increasingly averse to risks in technology, design, or market. Innovation is always risky, and is therefore highly constrained in this environment. Customization is nearly impossible; diverting precious resources to address a niche customer carries an enormous opportunity cost that no leadingedge fab is willing to accept. We are at the end of the road for the semiconductor business model driven by Moore's Law.