# **Chip Scale Review**<sup>®</sup>

ChipScaleReview.com

The Future of Semiconductor Packaging

Volume 26, Number 5

September • October 2022

3D ICs Direct bonding: a key enabler for 3D technologies page 6

- High-precision die attach

- Double-sided SiP for 5G wearable applications

- Meeting cost & technology requirements using MLF/QFN

- Silver-free AMB & copper bonding for cost-efficient, reliable AP

- Temperature accuracy & uniformity measurements in wafer probing

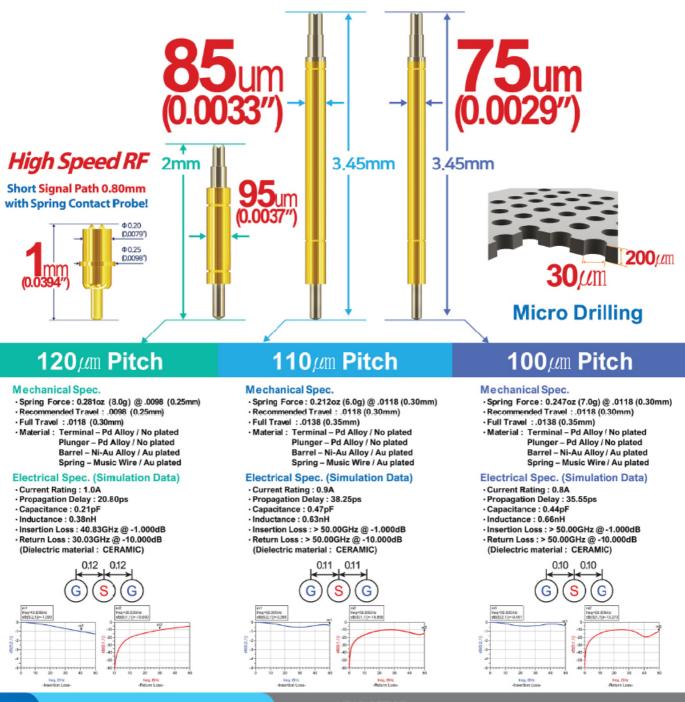

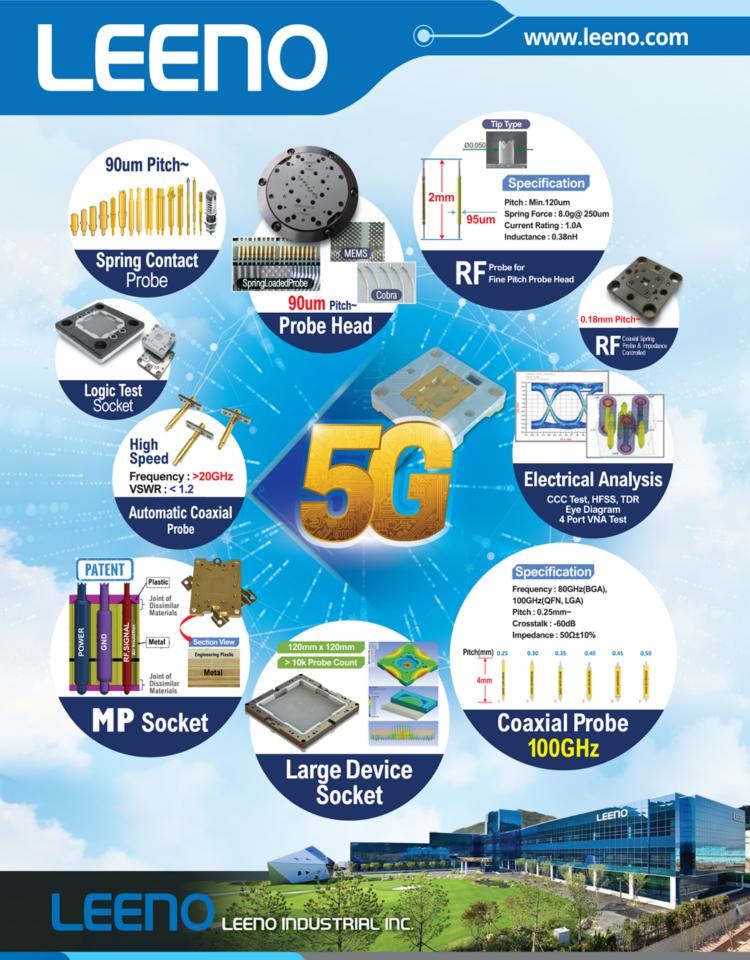

# **Continuous Non-stop Innovation!** & Probe Head

LEENO

# **Proven Mass Production Capability**

GLOBAL LEADER LEENO

#### HEAD OFFICE

10 105beon-gil MieumSandan-ro Gangseo-gu, Busan, Korea

#### CONTACT

USA: hskang@leeno.co.kr / +1 408 313 2964 / +82 10 8737 6561 Korea: sales-leeno@leeno.co.kr / +82 51 792 5639

# Enabling **performance**.

*Micro*LeadFrame<sup>®</sup> (MLF<sup>®</sup>/QFN) provides the right size, weight and performance for automotive, consumer, industrial, networking and communications application requirements. Our innovative leadframe packaging technology offers a cost effective solution when flexible form factor, adaptable interconnect technology, electrical and thermal performance are required.

Amkor – your source for leadframe packages.

Enabling the Future

amkor.com sales@amkor.com

26

www.EVGroup.com

# DIE-TO-WAFER (D2W) BONDING SOLUTIONS

Fusion and hybrid bonding for next-generation heterogeneous integration

Collective D2W bonding enabled by extensive knowledge in carrier preparation and die handling

Direct placement D2W activation and cleaning complete solution with EVG®320 D2W

Production-ready equipment solutions for successful integration of chiplets

Heterogeneous Integration Competence Center™ serving as leading-edge incubation center for customers and partners

GET IN TOUCH to discuss your manufacturing needs www.EVGroup.com

EVG<sup>®</sup> 320 D2W

## September • October 2022 Volume 26, Number 5

Challenges of direct hybrid bonding D2W remain in performance, yield and cost, which are driven by alignment capability, bonding quality and throughput, respectively.

Cover image copyright CEA-Leti, P. Jayet

## STAFF

Kim Newman Publisher knewman@chipscalereview.com

Lawrence Michaels Managing Director/Editor Imichaels@chipscalereview.com

Debra Vogler Senior Technical Editor dvogler@chipscalereview.com

SUBSCRIPTION—INQUIRIES Subscriptions are available without charge to qualified individuals in the electronics industry.

All subscription changes, additions, deletions to any and all subscriptions should be made by email only to subs@chipscalereview.com

Chip Scale Review, is published six times a year with issues in January-February, March-April, May-June, July-August, September-October and November-December.

#### Chip Scale Review P.O. Box 2165

P.0. 802 2165 Morgan Hill, CA 95038 Tel: +1-408-846-8580 E-Mail: subs@chipscalereview.com Printed in the United States

Copyright © 2022 Haley Publishing Inc. Chip Scale Review is a registered trademark of Haley Publishing Inc. All rights reserved.

#### Subscribe

# CONTENTS

## FEATURE ARTICLES

- **6 Direct bonding: a key enabler for 3D technologies** By Emilie Bourjot, Frank Fournel [CEA-Leti]

- 15 High-precision die attach: a major pillar of advanced packaging By Percy Lam

[ASMPT Limited]

#### **24 Double-sided SiP for 5G and wearable applications** By David Wang, Mike Tsai, J. Y. Chen, YP Wang

[Siliconware Precision Industries Co., Ltd]

## 32 Meeting cost and technology requirements using MLF/QFN

By Marc Mangrum [Amkor Technology, Inc.]

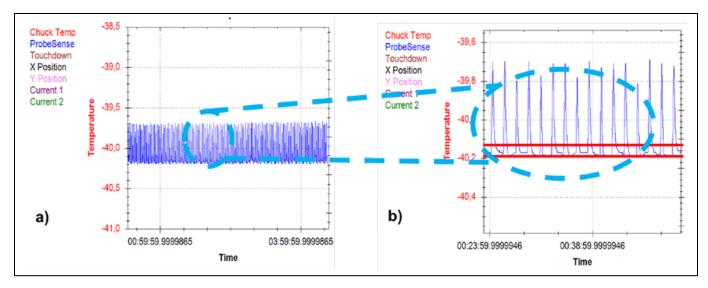

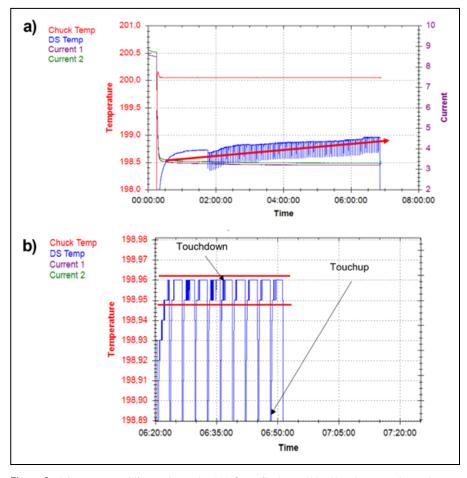

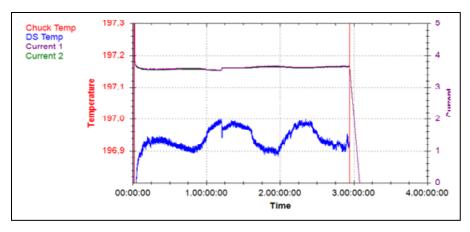

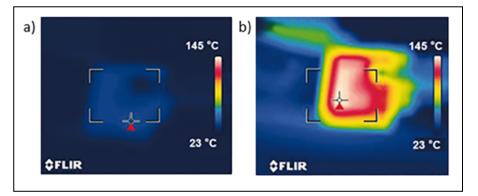

## 38 Addressing temperature accuracy and uniformity measurements in wafer probing

By Klemens Reitinger, Bengt Haunerland, Sophia Oldeide [ERS electronic GmbH]

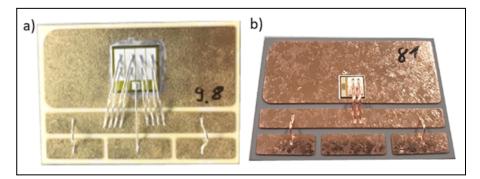

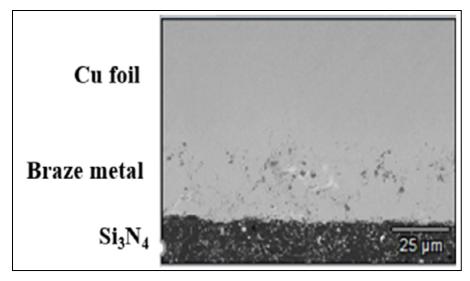

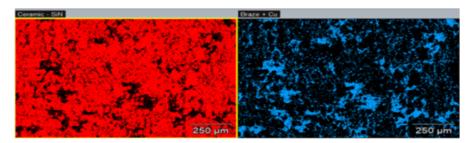

# 45 Silver-free AMB and copper bonding for cost-efficient, reliable advanced packaging

By A. Schwöbel, C. Féry, B. Fabian, D. Schnee, M. Rauer, A. Miric, S. Gunst [Heraeus Deutschland GmbH & Co. KG]

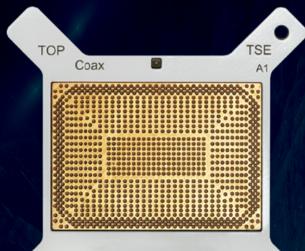

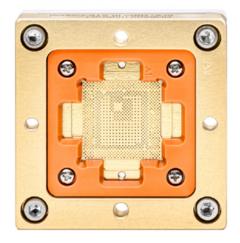

# COAXIAL ELASTOMER SOCKET

for >64Gbps ATE/SLT Test for Crosstalk free Board to Board Connector

ELTUNE-coax

Metal GND Structure Extremely Low Crosstalk >100Ghz@-20dB Inductance <0.1nH Min. pitch 0.6mm

D

G

GND Shielding by Metal housing

G

CONNECTION

GND

G: GND P: Power S: Signal

G,

# **COAXIAL ELASTOMER SOCKET**

for >64Gbps ATE/SLT Test for Crosstalk free Board to Board Connector

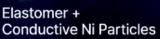

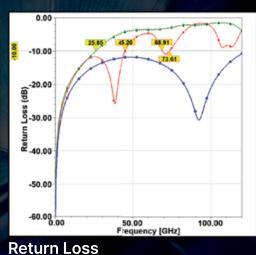

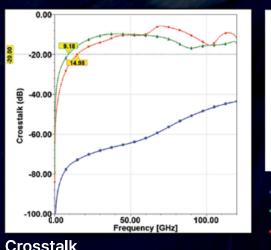

| Electrical Specifications (unit: GHz)                           |       |       |      |  |  |  |

|-----------------------------------------------------------------|-------|-------|------|--|--|--|

| 50Ω, 0.80mm pitch Spring pin Elastomer <b>ELTUNE</b> - <b>E</b> |       |       |      |  |  |  |

| Electrical Length(mm)                                           | 3.05  | 0.60  | 0.60 |  |  |  |

| Insertion Loss(S21) @-1dB                                       | 12.03 | 24.60 | >100 |  |  |  |

| Return Loss (S11) @-10dB                                        | 45.20 | 25.85 | >100 |  |  |  |

| Crosstalk (S31) @-20dB                                          | 14.98 | 9.18  | >100 |  |  |  |

Justin Yun justice@tse21.com Jimmy Hwang jimmyhwang@tse21.com

ELTUNE-coax Elastomer

Spring Pin

Crosstalk

www.tse21.com 189, Gunsu 1-gil, Jiksan-eup, Seobuk-gu, Cheonan-si, Chungnam, 31032, Korea

# Direct bonding: a key enabler for 3D technologies

By Emilie Bourjot, Frank Fournel [CEA-Leti]

irect bonding techniques are constantly in evolution to address "More Moore" and "More than Moore" challenges. CEA-Leti has developed expertise in direct bonding since the '90s with the emergence of silicon-on-insulator (SOI) technology. Since then, CEA-Leti teams have continued to actively innovate in direct bonding to widen the application field. This technique is based on the cohesion of two surfaces put intimately in contact at room temperature. Then, van der Waals forces (hydrogen bonds) and capillarity bridges create the needed adhesion energy. A postbonding annealing changes weak bonds into covalent bonds to make one piece of material at the end. Direct bonding now addresses not only substrate fabrication, but also the 3D interconnections domain with the emergence of hybrid bonding.

This article presents the different direct bonding techniques and their application in the microelectronics industry and R&D as developed by CEA-Leti. In the first part of the article, direct bonding physics are succinctly presented. Then, a summary of state-of-the-art bonding technologies is depicted, including hybrid bonding wafer-to-wafer (WTW), hybrid bonding die-to-wafer (DTW) and III-V heterogeneous bonding. Advantages, challenges, applications and stakes of each technique are compared with respect to the suitable application domain. A third part is focused on the latest hybrid bonding D2W results presented by CEA-Leti at ECTC 2022 and ESTC 2022. Integration challenges are discussed as well as the role of dedicated equipment development. The last section presents the potential markets and associated products, with an example of a chiplet with through-silicon vias (TSVs) and multi-layer stacking.

#### Introduction

The digitalization of the world is accelerating, which brings new useful services that increase the need for electronic components through a wide range of applications. System-in-package (SiP) and 3D integration schemes enable the possibility to mix different technologies and/or substrate materials together, addressing not only high-performance computing (HPC) applications requiring high-density interconnections, but also cost-sensitive applications (e.g., edge artificial intelligence and Internet of Things [IoT]). Breakthrough innovations are necessary to meet all specifications in terms of substrate materials and/or highdensity interconnections. Direct bonding represents a group of technologies that enable the bonding of two substrates vertically. This attribute matches perfectly with 3D requirements because it can be applied to high-density interconnections through hybrid bonding and can mix different materials with tiling. After a brief introduction on our expertise in direct bonding processes, a discussion of stateof-the-art processes for hybrid bonding and heterogeneous III-V D2W bonding is presented. Finally, we highlight the latest hybrid bonding D2W improvements and the critical role of TSVs in 3D integration.

# More than 30 years of expertise in bonding

CEA-Leti has developed deep expertise in direct bonding since the '90s with the emergence of SOI technology. From first lab work on oxide/silicon bonding, the technique was developed and maturated at CEA-Leti after the Unibond® SOI wafer was obtained. After more than 30 years, we have developed an international reputation in bonding development, including direct, polymer, thermocompression, eutectic and anodic bonding. Our role is to maturate bonding processes from proofof-concept to industrialization. More than 50 scientists and engineers are developing new solutions on direct bonding processes and process integration to products and we have more than 135 patents in this field. As such, wide knowledge on bonding mechanisms was built especially in direct bonding, on which fundamental mechanism models for adhesion [1] and adherence [2] have been proposed.

#### **Direct bonding processes**

Among bonding techniques, direct bonding is of particular interest for 3D applications. Direct bonding is a spontaneous bonding of two surfaces without liquid adhesive material. Among the different direct bonding technologies, molecular bonding – which implies hydrophilic surfaces – is the most common one. When two hydrophilic surfaces are intimately in contact at room temperature, van der Waals forces, hydrogen bonds and capillarity bridges create the needed adhesion energy to start and propagate this spontaneous bonding.

Just after the bonding, even if some covalent bondings are already present at room temperature, a post-bonding annealing is necessary to increase their density. The adherence energy, which is also called "the bonding energy," increases during the annealing using different physical-chemical mechanisms depending on the joining materials.

Definitively, the direct bonding phenomenon is different from thermocompression and adhesive bonding, which require, respectively, both temperature and pressure, or an additional material such as polymer to ensure contact between the two surfaces. Direct bonding is a spontaneous bonding and its thermal evolution does not require an external load. It is a selfmade bonding. Nevertheless, the price for this phenomenon is the stringent surface requirements of topography, planarity, roughness, and particulate contamination responsible for bonding defects. Surface cleanliness and topography are critical to have a successful direct bond.

Obviously, the direct bonding phenomenon is not limited to hydrophilic surfaces. Hydrophobic surfaces can also be bonded where only weak van der Waals forces are involved for adhesion. The stakes are to manage all surface characteristics to be compatible with the bond type involved. Therefore, in-depth knowledge of bonding physics is required to integrate the most suitable bonding technique to the targeted application.

# State-of-the-art direct bonding technologies

Direct bonding offers several possibilities depending on the surface to be bonded: 1) either a homogeneous material surface is bonded on another material, for example III-V on silicon, or 2) a heterogeneous (hybrid) surface composed of a mix of Cu and  $SiO_2$ , for instance, known as direct hybrid bonding. Stakes, advantages, challenges and applications depend on the technique that is used; these are summarized in **Table 1** and explained in the following paragraphs.

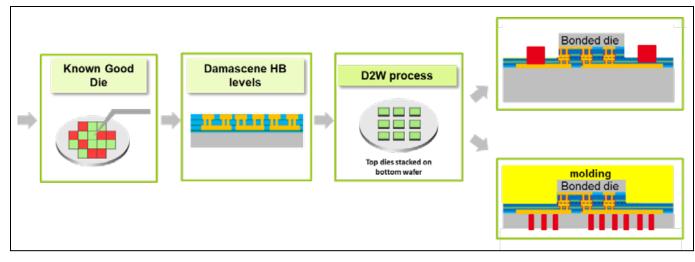

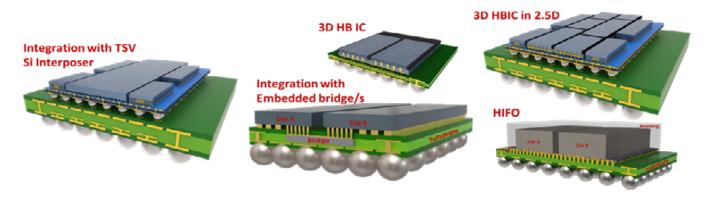

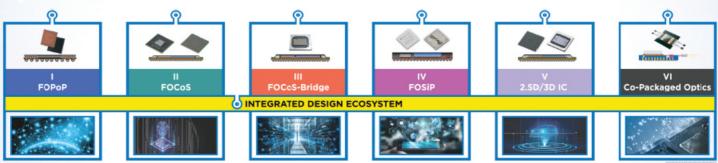

W2W and D2W direct hybrid bonding. Packaging and 3D integration have grown in importance as two of the key technology enablers to compensate for the slowing of two-dimensional scaling associated with Moore's Law. Big players have moved to new architectures, such as chiplets, thanks to the integration of "More than Moore" technologies, such as 2.5D and 3D integration, memory cubes, accelerators and heterogeneous architectures. This integration brings key elements of success with a much larger number of I/O connections, and the trade-off between performance and energy efficiency to advanced 3D system-on-chip (SoC) devices. Hybrid bonding is a good candidate for high-interconnect density because it enables connecting dies using tiny copper-to-copper connections, as opposed to bumps.

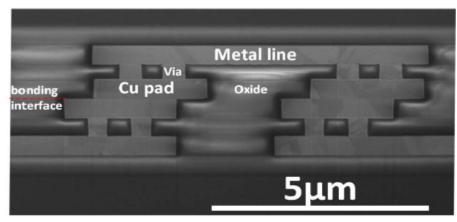

To achieve hybrid bonding, a Cu damascene level is adapted to reach the applicable bonding specification after a crucial planarization step is done on both tiers to be assembled. Planarization by chemical mechanical planarization (CMP) is definitely a key process step to ensure high yield. Ultra-low nanotopography must be guaranteed from the millimeter scale (flat die) down to the material scale (flat surface with low roughness) and going through to the micron scale (flat pattern). Enabling this ultra-low nanotopography in the space of the design rules with different Cu densities and Cu pad sizes was a unique challenge that was solved thanks to the achievement of CMP process control of consumables (slurry/pad/diamond disk/recipe parameters). A precise alignment during the direct bonding process is required to achieve the electrical path by joining the Cu patterns together. High-density interconnections

|                                       | Stakes                                                     | Advantages                                                                     | Challenges                                                                                                  | Application                            |

|---------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Hybrid bonding<br>W2W                 | Interconnection density                                    | Large know-how<br>In production                                                | Topography control of a<br>Cu/dielectric surface                                                            | Imagers, memory on<br>memory           |

| Hybrid bonding<br>D2W                 | Interconnection density<br>Yield<br>Heterogeneous 3D       | Design flexibility<br>Yield with KGD                                           | Topography control of a<br>Cu/dielectric surface<br>Alignment<br>Dicing and surface<br>cleanliness          | HPC, edge Al, logic                    |

| Heterogeneous<br>III-V D2W<br>bonding | Sparse integration of III-V<br>material on silicon devices | Dislocation free III-<br>V materials usually<br>highly processed               | Dicing and surface<br>cleanliness                                                                           | Displays, Imagers, RF,<br>telecom LIFI |

|                                       | III-Vs tiled on larger<br>diameter silicon substrate       | Opens doors to<br>modern fabs<br>Stiffer substrate<br>Saves scarce<br>material | CTE management<br>Dicing and surface<br>cleanliness<br>Design rules<br>Co-integration with Si<br>technology | Displays, Imagers, RF, telecom         |

Table 1: Stakes, advantages, challenges and applications depend on each technique.

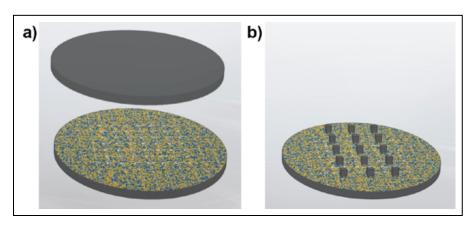

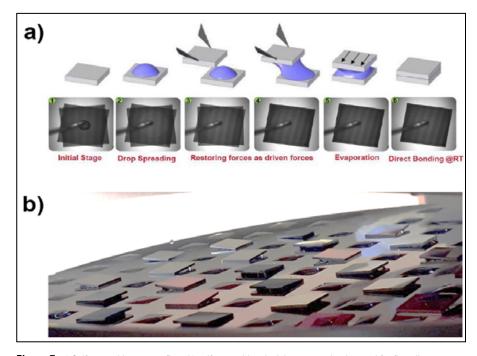

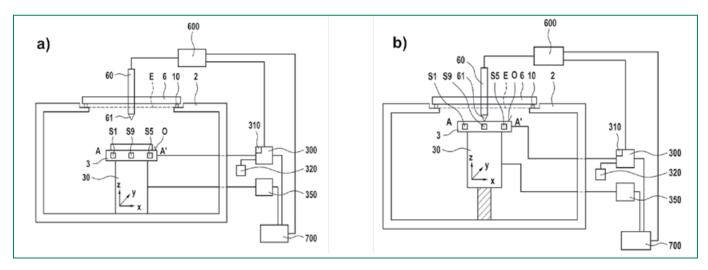

Figure 1: a) (left) W2W and b) (right) D2W bonding. SOURCE: CEA-Leti

can be achieved, with pitches ranging from  $10\mu m$  down to  $1\mu m$ .

Direct hybrid bonding offers two configurations of assembly: W2W and D2W (Figure 1). W2W hybrid bonding is already mature for imaging applications-starting with Sony in 2016. It is characterized by the alignment at wafer scale (Figure 2). With the latest generation of W2W bonders, suppliers claim alignment capability below 50nm 3o. The main advantage is high throughput, but the drawback is low flexibility for design because bottom and top dies need to have the same dimension. For more design flexibility, hybrid bonding D2W is more suitable. This process re-uses the know-how developed for W2W, but it adds dicing and cleanliness challenges. The known good die (KGD) concept can be applied to increase the overall product yield by selecting only good dies before assembling. DTW technology is of great interest for many applications such as edge devices with more and more real-time computing of a large amount of data with a limited power budget. Other "More than Moore" applications are good candidates like photonics with imagers and display for design flexibility, or optic transceivers and radio frequency (RF).

Heterogeneous III-V D2W bonding. While hybrid bonding is addressing Si technologies, other applications need the superior III-V materials' properties (electron and hole mobilities, direct band gap). However, III-V materials are not available in large substrate diameters, thereby closing access to advanced fabs. In addition, raw materials are scarce, making bulk substrates costly. Therefore, new solutions are needed to combine the advantages of III-V materials on a silicon wafer, which refers to heterogeneous III-V D2W bonding here. Two approaches can be considered: on the one hand, the technology (laser cavity, for instance) is performed before the assembly. It has the advantages of having good quality III-V materials and only a small amount of material is bonded at the right place [3].

A second path can be considered in which only a material thin-film template is transferred onto the silicon platform, using direct bonding of III-V coupons on a silicon wafer. The epitaxial device growth, or at least a part of it, could then be done later on the silicon wafer, allowing very narrow inter-device shrinkage [4]—this is called "tiling." This die "tiling" could be done on a sparse area but, in a very interesting manner, using the SmartCut<sup>™</sup> technology, a large area could be covered within an industrial

# Leading solutions

for next generation power semiconductors and advanced packaging

MKS | Atotech

High-quality electrolytic and electroless metal deposition processes are crucial for the semiconductor industry, which is why it relies on Atotech to provide leading solutions, products, and services.

Our focus on processes for advanced packaging and power semiconductor applications enables us to provide processes for, for example, the deposition of pillars,  $\mu$ -vias, and fine line RDL of highest purity Cu. In doing so, the toughest of reliability requirements for next-generation semiconductor devices are achieved. The Cu process suite is complemented by a variety of processes for the deposition of Ni, NiFe, Sn, SnAg, Au, and more.

Additionally, Atotech's ENEPIG processes are broadly applied in power semiconductors, for example, in the automotive industry, and enable the plating of Ni, Pd, and Au with highest purity and reliability, ensuring best-in-class interconnections via wire bonding, soldering, or sintering.

As a leading supplier of plating solutions for the semiconductor industry, we have a strong focus on R&D and are committed to continuously developing innovative and sustainable technologies for the devices of tomorrow.

Atotech an MKS Brand

info@atotech.com

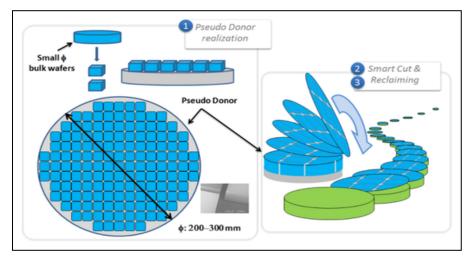

path (Figure 3). Using the SmartCut<sup>™</sup> technology involves first tiling III-V dies over a 200 or 300mm silicon substrate. This creates a so-called pseudo-donor wafer paved with dies several hundred microns thick. Second, this pseudo-donor is used to transfer collectively thin layers (100-1,000nm) of III-V dies on another silicon substrate using the SmartCut<sup>™</sup> technology. The pseudo-donor substrate can be reused many times. This work is underway jointly with Soitec [5].

For applications using large III-V areas, the SmartCut<sup>™</sup> tiling is a breakthrough

technology—it breaks the wafer-diameter ceiling and saves scarce material because only a thin layer is used rather than a bulk substrate. This type of tiling will be the key technology to bring these III-V materials into high-volume manufacturing for display applications, for instance. Substrates tiled with thin layers of III-V materials are then provided to foundries for further device processing. In that case, III-V material is present at the front end of the device fabrication process. This brings challenges to co-process III-V materials and silicon, but

Figure 2: Direct hybrid bonding cross section in W2W. SOURCE: CEA-Leti

Figure 3: Schematic of the SmartCut<sup>™</sup> tiling approach [5].

also opportunities because in that case, III-V and Si devices are next to each other, which facilitates the interconnects.

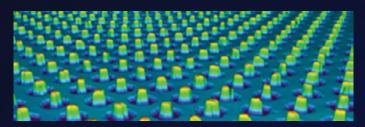

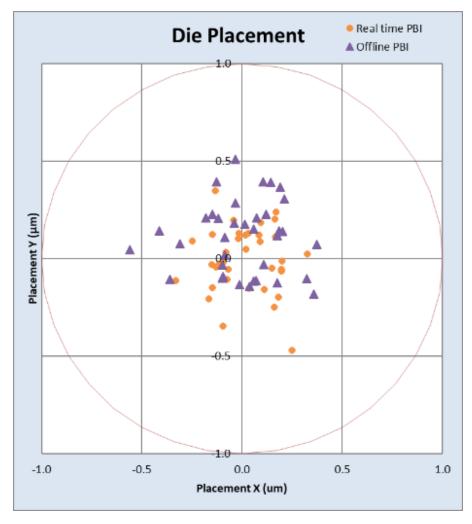

# Recent hybrid bonding D2W improvements

The latest trends featured at ECTC 2022 showed a strong interest in hybrid bonding D2W. (Figures 4-5) [6-9]. Challenges of direct hybrid bonding D2W remain in performance, yield and cost, which are driven by alignment capability, bonding quality and throughput, respectively. Die bonder equipment is, therefore, a key piece for industrialization; it must meet class 1 cleanroom and accurate surface-bonding specifications. A fruitful collaboration between CEA-Leti and SET Corp. enabled emergence of a die bonder specifically designed for hybrid bonding D2W with alignment capability of 1µm  $3\sigma$  post bonding. It integrates a local clean environment, adaptation of robotics to avoid particulate contamination and precise alignment thanks to its optical alignment capability. Regarding yield, the cleaning post dicing was the other challenge. Regular sawing offers a simple way of dicing dies, but it has a high level of contamination. We have developed an efficient strategy for die cleaning. The combination of those skills enables demonstration of a high-yield level and an alignment capability below <1µm  $3\sigma$  (Figure 6), after bonding with high electrical yield [8-9]. However, ensuring a high throughput with a high bonding precision remains a big challenge from an economic perspective.

Before explaining the different solutions under investigation, it is important to clarify some definitions of alignment. Machine intrinsic accuracy, die placement accuracy and die alignment post bonding are three components of global alignment. Machine intrinsic accuracy and die placement depend on optics, tool parameters and environment. The die integration characteristics and the alignment measurement method also play a role. Indeed, the best representation of a misalignment is a measurement at two extreme corners of the die. Therefore, the die alignment post bonding depends on all of those parameters.

An accurate alignment takes a long time. Therefore, several approaches exist to increase throughput based on a pick and place (P&P) tool with increased speed or collective bonding. Here, collective bonding refers to pre-aligned dies with a temporary bonding and high alignment

# adeia

# XPERI IP BUSINESS IS NOW ADEIA

Adeia turns ideas into innovations Our name may be new, but our roots run deep with decades of continued innovation. We invent, develop and license innovations that advance how we live, work and play.

# Adeia invented and pioneered Direct and Hybrid Bonding

# DBI<sup>®</sup> Ultra

Die-to-Wafer Hybrid Bonding

# DBI®

Wafer-to-Wafer Hybrid Bonding

# **ZiBond**®

Wafer-to-Wafer Direct Bonding

Better Ideas. Better Entertainment. adeia.com

Figure 4: D2W process flow. SOURCE: CEA-Leti

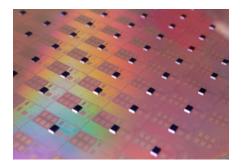

Figure 5: Die-to-wafer. SOURCE: CEA-Leti; COURTESY: P. Jayet

accuracy. The final bonding is then performed collectively by W2W. The alignment is then composed of combined D2W and W2W misalignment errors. The throughput is then limited by the P&P tool used for die placement of the temporary bonding. This solution seems to be limited to solve the D2W throughput issue.

One alternative strategy developed by CEA-Leti in collaboration with Intel is self-assembly (Figure 7). A gross prealignment >200µm is performed, while the fine alignment is realized by a water droplet and capillarity forces. This process can be implemented either in collective, or in P&P ways. In the collective way, dies are placed in a holder with a high-speed die sorter at low precision >200µm. All dies are then pickedup simultaneously by droplets and selfaligned. In the P&P, pre-alignment can be coarse enough to reach high throughput. The droplet completes the fine alignment to reach below 400nm  $3\sigma$ . The throughput could be improved up to 2,000 dies/hour. Dedicated self-assembly equipment needs to be developed in collaboration with equipment suppliers to ensure reproducibility for highvolume manufacturing.

Figure 6: Direct hybrid bonding cross section in D2W. SOURCE: CEA-Leti

Figure 7: a) Self-assembly process flow; b) self-assembly principle—water droplet used for fine alignment thanks to capillary forces. SOURCE: CEA-Leti

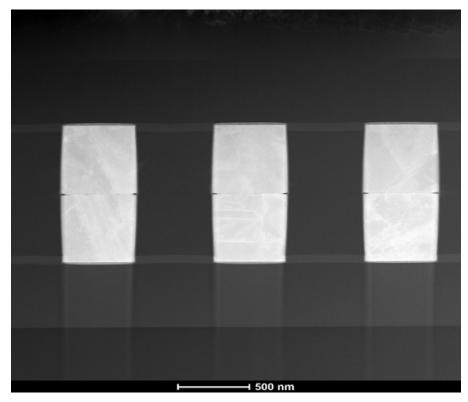

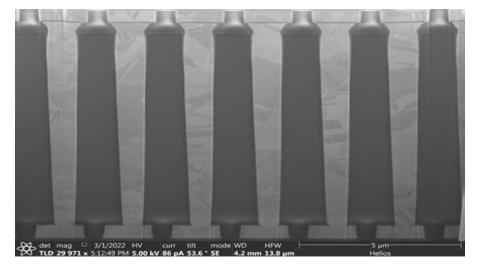

Figure 8: TSV structures. SOURCE: CEA-Leti

#### Benefits of TSVs for products

Concerning D2W hybrid bonding, it is important to mention the role of TSVs (Figure 8). By nature, systems featuring hybrid bonded types of interconnections will require an access to embedded metal pads and, ideally, in an array format to keep the density for further layer or ball grid array (BGA) connections, for example. An elegant way to access these contacts is the use of TSVs. Depending on the targeted products, several types of vias could be envisioned. For three-layer types of imaging devices [10], high-density TSVs in the range of Ø1um and 10um depth will be employed for the inner strata, while for active-interposer types of modules [11], TSV middle processes of Ø5µm to Ø10µm and 50µm to 100µm depth will be preferred. The effective coupling of appropriate TSV and hybrid bonding technologies appears as a strong leverage for the development of products with unprecedented dense interconnection architectures.

#### Summary

Direct bonding technologies are key enablers for 3D microelectronics.

They enable the mixing of exotic material and/or different technologies in one place for performance, design flexibility or heterogeneity. A wide range of direct bonding processes meet several applications' needs, from substrate development to back-end 3D interconnections, and the ability to manage bonding mechanisms and integration. For 3D schemes, direct hybrid bonding in W2W and D2W versions are extremely attractive for increasing highdensity interconnection. D2W pushes the assets of hybrid bonding by adding design flexibility and high yield. Challenges to manage the trade-off between throughput and alignment performance. Several process options are in development, such as improved P&P speed and selfassembly, where equipment suppliers play a critical role.

#### References

- D. Radisson, "Collage direct sur surfaces structurées," PhD Thesis, Grenoble, 2014.

- 2. F. Rieutord, et al., "Rough surface adhesion mechanisms for wafer

bonding," ECS Trans., vol. 3, no 6, p. 205, Oct. 2006.

- 3. B. Szelag, et al., "Advances on largescale integration CMOS-compatible hybrid III-V/Si laser on 200mm platform," Smart Photonic and Optoelectronic Integrated Circuits XXI, Mar. 2019, vol. 10922, p. 109221O.

- C. Besancon, et al., "AlGaInAs MQW laser regrowth on heterogeneous InPon-SOI: performance for different silicon cavity designs," Optical Fiber Comm. Conf. (OFC) 2021, p. W1B.1.

- 5. B. Ghyselen, et al., "Large-diameter III-V on Si substrates by the SmartCut Process: The 200mm InP film on Si substrate example," Phys. Status Solidi A, vol. 219, no 4, p. 2100543, 2022.

- 6. A. Jouve, et al., "Die-to-wafer direct hybrid bonding demonstration with high alignment accuracy and electrical yields," 3DIC, 2019.

- 7. E. Bourjot, et al., "Toward a complete direct hybrid bonding D2W integration flow: known-good dies and die planarization modules development," 3DIC, 2019.

- E. Bourjot, et al., "Known-good dies strategies compatible with D2W direct hybrid bonding," IEEE 71st Elec. Comp. and Tech. Conf. (ECTC), 2021, pp. 470–475.

- E. Bourjot, et al., "10µm and 5µm die-to-wafer direct hybrid bonding," ESTC, 2022.

- P. Vivet et al., "Advanced 3D design and technologies for 3-layer Smart Imager," Inter. Symp. on VLSI Tech., Systems and Appl. (VLSI-TSA), 2022, p. 1-2.

- P. Coudrain, et al., "Active interposer technology for chiplet-based advanced 3D system architectures," IEEE 69th ECTC, May 2019, pp. 569-578.

#### **Biographies**

Emilie Bourjot is a Project Manager at CEA-Leti, Grenoble, France. Her current activities involve developing advanced hybrid bonding schemes for 3D integration. Prior to joining CEA-Leti, she worked with GlobalFoundries (Germany, USA) and within the IBM Alliance (USA) on the development of advanced FDSOI technologies and sub-3nm nodes. She earned a MSc in Materials Physics from INSA Lyon (France) and a PhD from Aix-Marseille U., France. Email emilie.bourjot@cea.fr

Frank Fournel is head of wafer bonding engineering at CEA-Leti, Grenoble, France, and a board member of the international ECS Wafer Bonding Symposium Conference, the International WaferBond Conference, and the Low Temperature Bonding 3D Conference. He has a Master's in Materials Science from Ecole Supérieure de Physique et de Chimie Industrielle de la ville de Paris (ESPCI) in Materials Science, and a PhD from Grenoble U.

## SUSS EQUIPMENT SOLUTIONS ENABLING LEADING-EDGE PACKAGING TECHNOLOGIES

SUSS MicroTec is a leading supplier of equipment and process solutions for the semiconductor industry enabling state-of-the-art packaging technologies from R&D to high volume production.

With next generation lithography solutions for FOWLP and leading edge wafer bonding technologies for 2.5D and 3D stacking, we contribute to the advancement of innovations in the key areas of packaging and system integration.

Always be one step ahead — with solutions from SUSS MicroTec. Contact us for more information! SUSS MicroTec info@suss.com www.suss.com

# **3D Solution** for FC-BGA Bump Inspection

#### Most Precise 3D measurement

New High-End Products are constantly required for Finer Pitch Bumps. Substrate Warpage and Coplanarity have become much more important than ever for complex packaging.

INTEKPLUS has developed and provided most precise 3D measurement equipment for Fine-Pitch Bump such as µBump and Cu Pillar.

KOSDAD

STED COMPANY

(КАВ)

#### Real 3D inspection for Flip Chip Packaging

3D conditions such as Bump Height and Warpage are important quality factors for Flip Chip Packaging.

3D measurement with Accuracy and Precision, and output data required for FC substrate.

## iSIS Series for FC-BGA Bump Inspection

#### Yield improvement

Analyze bumps condition to increase production yield. 3D Inspection of bumps before packaging to avoid Si Die loss due to NG bumps.

#### **Fine-pitch inspection**

Inspect finest pitch bumps in mass-production. Shadow-free by WSI using coaxial illumination.

#### Accuracy and Precision

Bump height and coplanarity measured by high accuracy and precision enough to measure transparent Pl layer thickness.

INTEKPLUS KR HQ Sales person : YK Sung sygs@intekplus.com INTEKPLUS US Office Sales person : Harry Yun Harryyun@intekplus.com INTEKPLUS CN Office Sales person : Kevin Lin hisopio12@intekplus.com INTEKPLUS TW Office Sales person : Arthur Tung arthur@intekplus.com

#### INTEKPLUS JP Office

Sales person : SS Kim ssk@intekplus.com

## INTEKPLUS CO.,LTD.

Visual Technology for Semiconductor Package / Wafer / EV Battery / Display #263, Techno 2-ro, Yuseong-Gu, Daejeon, 34026 Korea Tel : +82-42-930-9900 Fax : +82-42-930-9999

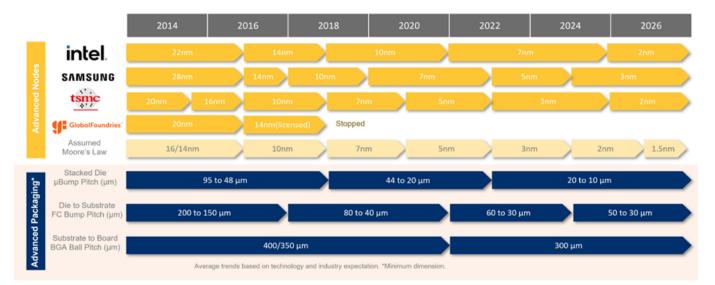

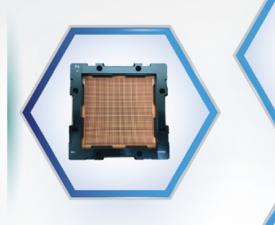

## High-precision die attach: a major pillar of advanced packaging

By Percy Lam [ASMPT Limited]

ver the last decade, semiconductor technology node advancement and the gradual increasing sophistication of advanced packaging have happened in tandem. Commencing with the introduction of embedded wafer-level ball grid array (eWLB) technology by Infineon more than 10 years ago, followed by the introduction of 2.5D packaging known as Chip on Wafer on Substrate (CoWoS<sup>®</sup>) by TSMC, a growing number of innovations in the arena of advanced packaging have been contributed by major manufacturers. According to Yole Group's advanced packaging market report in 2020 [1], advanced packaging revenue is swiftly catching up to the traditional packaging market. In 2014, advanced packaging (AP) accounted for 38% of the total packaging market. However, its (AP) market share will increase to around 50% in 2025, or around \$42 billion. In an 11year period from 2014 to 2025, AP revenue is forecast to almost catch up with that of traditional packaging.

The AP development roadmap closely follows the path of the advanced node front-end roadmap provided by the three major leaders in the world, namely TSMC, Intel and Samsung (Figure 1).

The continued node development from 10nm down to 2nm and even smaller is in question, however, as the commercial returns are not commensurate with the extremely high capital investment required. In order to reduce the financial commitment for future node development, an effective approach is switching from "only frontend node scaling" to "a combination of front-end scaling with back-end scaling." Heterogeneous integration (HI) is the way forward (Figure 2). HI is an approach using AP technologies that enable the integration of multiple chiplets with different functionalities and each fabricated using the best fit node in terms of technology and economics, to reassemble a system-ona-chip (SoC)-like function.

A nontrivial issue usually encountered by foundries or assembly houses using AP to realize the concept of HI is the large variety of die attach requirements needed to meet the ever-evolving AP technologies. High-precision die attach requirements have become a critical factor in accomplishing a successful AP rollout (see Figure 3).

# Important requirements for die attach tools

In order to actualize the intended advanced package structure, specifying adequate and realistic requirements for die attach tools during the tool selection process is a vital aspect of a quality-first execution strategy. The following sections discuss the applicable requirements for die attach tools.

Die placement accuracy. Capability of higher die placement accuracy depends on machine design of the die attach tool itself (Figure 4). Machine cost usually increases with die placement accuracy and is inversely related to productivity. Figure 4 shows an example of a high die placement accuracy measurement result based on the bond mode of a face-up die where the local alignment is executed by a high-precision die attach tool.

Various bond modes. To support the three bond modes of fan-out packaging, i.e., die first/face up, die first/face down or die last/face down, easy switching among the different modes is a basic requirement. A heated bond collet tool and a heated bond chuck for die attach film (DAF) bonding are required for die face-up bonding at elevated temperatures. Flux dipping for mass reflow flip-chip bonding is an option for redistribution layer (RDL)-first/die-

Figure 1: Technology roadmap – front-end manufacturing vs. advanced packaging. SOURCE: Yole Group, 2020 [1]

# **COAXIAL SOCKET**

**Bandwidth up to** 112Gbps

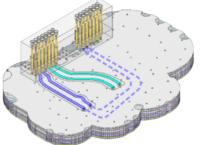

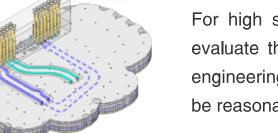

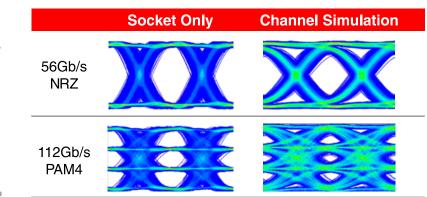

## **3D Stacking Simulation**

0

**Return Loss**

50 Freq [GHz

Brownie Coaxial

Channel Simulation

112Gb/s PAM4

평-30 -40

-60

**Co-grounding Design**

**EM Wave**

For high speed test application, it's necessary to evaluate the performance of the entire channel at engineering stage to ensure the specifications can be reasonably defined during testing.

## **Eye Diagram**

ЦÌ,

| Solution       | Bandwidth | Crosstalk    | Impedance (50Ω)  |

|----------------|-----------|--------------|------------------|

| Plastic Socket | <20 GHz   | -10 ~ -25 dB | <b>△&gt;10</b> % |

| Coaxial Socket | >80 GHz   | -50 ~ -70 dB | <b>∆3 ~ 5 %</b>  |

Figure 2: Various approaches of accomplishing heterogeneous integration (HI). SOURCE: ASMPT internal report, 2019

last/face-down mode, which is important for high-density fan-out applications. In the case of thermocompression bonding (TCB), flip-chip bonding with local reflow is a must requirement, though typically, it cannot co-exist with fan-out bond modes.

**Die size.** Because of the varying die sizes required for different processes, the range of die sizes can vary from 0.5mm x 0.5mm to a size as large as 26mm x 33mm. The size of molded compound die can be up to 70mm x 70mm. It is a challenge for a die attach tool to allow such a large die size variation from pick-up until the attach process on the substrate is complete.

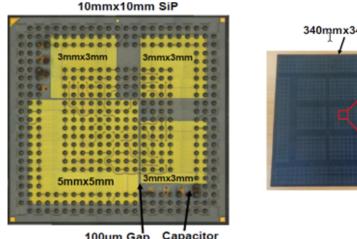

**Multi-die requirement.** As HI continues to prevail, multi-die packages containing dies of different sizes will become common (**Figure 5**). The die attach tool should be able to support a single recipe to handle different die sizes. Hardware support required includes tooling designed for different die sizes and the tooling such as the ejector, die pick collet, and die bond collet should be automatically changed. Additionally, wafers of different dies should be automatically loaded from the wafer cassette, without the need for human intervention to support tooling part conversion and recipe program loading.

**Thin-die requirement.** Because the package profile is another essential factor when considering AP, sometimes die thickness would go down below 50µm. For some specific applications, such as memory die for stacking, as well as bridge die for embedding, the thickness could be as thin as, or less than, 30µm. Normal pin for die ejection might become insufficient to ensure crack-free die pick-up; specially designed needle-less multi-blade ejector technology has been proven to be a high-volume manufacturing (HVM) solution for thin-die handling (**Figure 6**).

| Packaging                  | Bonding Mode / Requirement                                                                                                                                                                                        | Placement Accuracy Required            |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| Die 2 Die 1<br>Fan-out SiP | <ul> <li>Chip-to-Wafer (C2W) or Chip-to-Panel (C2P),</li> <li>Die First &amp; Face-down mode</li> <li>Global &amp; Local alignment mode</li> <li>Room Temperature and Elevated Temperature<br/>Bonding</li> </ul> | C2W: +/-5µm<br>C2P: +/-5~10µm          |  |

|                            |                                                                                                                                                                                                                   | 1                                      |  |

|                            | <ul> <li>Chip-to-Wafer (C2W) Face-up DAF Bonding</li> </ul>                                                                                                                                                       | +/-3µm                                 |  |

|                            | <ul> <li>Chip-to-Wafer (C2W) Flip Chip (Mass Reflow or<br/>TCB)</li> </ul>                                                                                                                                        | MRFC: +/-3~5µm<br>TCB: +/-2µm and <1µm |  |

| Die 2 Die 1                | <ul> <li>Bridge Die Bonding by Flip Chip (Mass Reflow or<br/>TCB)</li> </ul>                                                                                                                                      | MRFC: +/-3~5µm<br>TCB: +/-2µm and <1µm |  |

|                            | Bridge Die Bonding by Face-up DAF Bond                                                                                                                                                                            | +/-1 to 5µm                            |  |

| High-Density Fan-out       | <ul> <li>Chip-to-Substrate (C2S), Compound Die Flip Chip<br/>(Mass Reflow or TCB)</li> </ul>                                                                                                                      | MRFC: +/- 5μm<br>TCB: +/-2μm           |  |

|                            |                                                                                                                                                                                                                   | •                                      |  |

|                            | <ul> <li>Chip-to-Wafer (C2W) Flip Chip (Mass Reflow or<br/>TCB)</li> </ul>                                                                                                                                        | MRFC: +/-3~5µm<br>TCB: +/-2µm and <1µm |  |

|                            | <ul> <li>Bridge Die Bonding by Flip Chip (Mass Reflow or<br/>TCB)</li> </ul>                                                                                                                                      | MRFC: +/-3~5µm<br>TCB: +/-2µm and <1µm |  |

| HBM SoC HBM                | <ul> <li>Bridge Die Bonding by Face-up DAF Bond</li> </ul>                                                                                                                                                        | +/-1 to 5µm                            |  |

| 2.5D Packaging             | <ul> <li>Chip-to-Substrate (C2S), Compound Die Flip Chip<br/>(Mass Reflow or TCB)</li> </ul>                                                                                                                      | MRFC: +/- 5μm<br>TCB: +/-2μm           |  |

Figure 3: Examples of major advanced packaging and placement accuracy requirements.

Bond force. Depending on the bonding material property, bonding processes and die sizes, the required bond force may vary across a large range. For fan-out applications, a bond force ranging from 0.5N to 30N is usually sufficient to cope with most of the requirements. In the case of TCB, the required bond force can be as high as 300N.

Figure 4: Die placement accuracy of 1µm. SOURCE: ASMPT internal report, 2019

Substrate dimensions. Substrates can be 12-inch wafers or glass carriers, 300mm x 300mm metal carriers, 50mm x 50mm singulated substrates, or 600mm x 600mm metal carriers. Die attach tools are typically classified as wafer-level (12-inch wafer or 300mm quad panel) or panel-level (up to a 600mm x 600mm panel); consequently, the maximum substrate dimensions must be considered while selecting a die attach tool.

Cleanliness. Class 100 is the most common cleanliness requirement for a die attach tool for AP. Certainly, demand for a higher degree of cleanliness up to Class 1 is now being required for emerging applications, and the process cost of ownership will be reflected in the technology requirement.

Inline automation. Automatic material load/unload by means of overhoist transport (OHT) or automatic guided vehicle (AGV) is recommended, especially when preparing for HVM. Semiconductor Equipment Communication Standard (SECS) and the Generic Model for Communications and Control of Manufacturing Equipment (GEM) are the basic standards that apply to communications between the die attach tool and equipment automation (EAP) host.

Traceability. Traceability is one of the most important manufacturing control requirements in HVM especially when the product is for automotive applications. Basic information such as: wafer, substrate, bonding parameters, and inspection results of all production activities, is allowed for access, storage and uploading to the manufacturing host computer database.

Chip: 3mmx3mm

100um Gap Capacitor

Chip: 3mmx3mm

Chip: 5mmx5mm Chip: 3mmx3mm Capacitor

Figure 5: Multi-die fan-out package. SOURCE: [2]

# Throughput got you down?

# Speed things up with Deca's 600mm panel technology!

Offering a 5X increase in usable area as compared to a standard wafer, increasing efficiency by upwards of 20% for large designs, eliminating pesky reticle limitations, and increasing the speed of die placement by solving die shift problems using Deca's patented Adaptive Patterning<sup>®</sup>.

WE CLEAN IT UP. ADAPTIVE PATTERNING\* FROM ODDECA

thinkdeca.com

Figure 6: Needle-less ejector system for handling

thin-die pick up. SOURCE: ASMPT

chemical shrinkage of the EMC, the CTE of the carrier, gravity, the debonding process, etc.

- The die shift caused by the CTE mismatch between the EMC and silicon, which is also influenced by chemical shrinkage of the EMC, the type of EMC, and the thermal release tape in use.

- The amount of die shift compensation that can be accomplished by using intelligent offset introduced during the die attach process (see Figure 7).

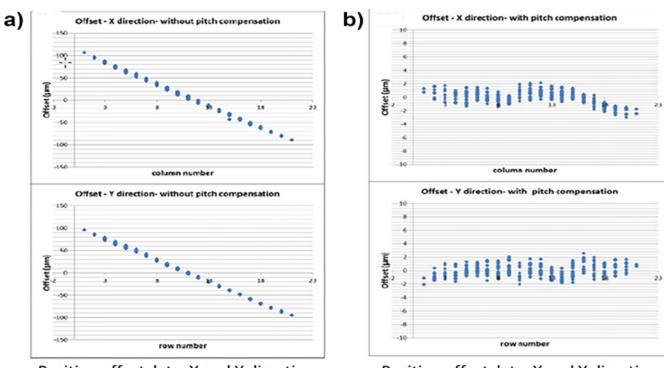

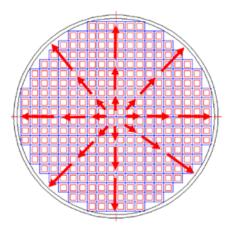

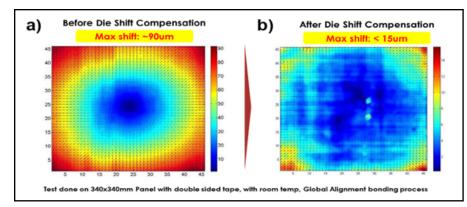

**Die systematic shift.** During encapsulation of a die-attached substrate, die shift may happen and can be found after debonding of the molded substrate (**Figure 8**). Oftentimes, the trend of die shift can be observed to be systematic. The major contributing factor is materialrelated shrinkage of the carrier, adhesive and EMC. Fortunately, the issue can be predicted and compensation provided during die pick-and-place (**Figure 9**).

Wafer substrate warpage handling capability. Substrate handling is often complicated by substrate warpage.

Position offset data: X and Y direction (without pitch compensation)

# Position offset data: X and Y direction (with pitch compensation)

Figure 7: Die systematic shift position offset data in the X and Y directions: a) without pitch compensation; and b) with pitch compensation. SOURCE: [3]

# Challenges with the die attach process

The following sections discuss the challenges associated with the die attach process.

Die shift in fan-out packaging (waferand panel-level fan-out). There are still many different aspects of process, material and equipment development needed for further improvement of fan-out packaging quality and yield improvement. The major challenges are as follows:

- Warpage caused by a mismatch between the coefficient of thermal expansion (CTE) for the epoxy mold compound (EMC) and silicon.

- Impact on the process caused by

Figure 8: Directions of die shift from the wafer's center. SOURCE: ASMPT

Oftentimes substrate warpage can be as large as up to five millimeters. This serious issue is basically related to the complicated structure for the AP application where it is no longer a bare silicon or glass carrier. For example, the substrate can be fabricated with multilayer RDLs with asymmetric metal density. Or, the substrate can have unevenly distributed embedded components. Such structural differences will lead to warpage either at room temperature or at elevated temperatures. Machine design, therefore, requires appropriate attention to such mechanical and process considerations (Figure 10).

Flux-cleaning issue. When the die size increases and the bump pitch

- · Can be fully automated

- Robust and easy to recalibrate offline

- Highly repeatable calibration processes

according to ITS90 and ISO 17025

- Temperature range: -65°C to 300°C, ice-free at cold temperatures

- Temperature accuracy below 30mK

# ERS

## Thermal Chuck Systems

- -65°C to 550°C

- Available in 6", 8" and 12"

- Individual vacuum designs

- Nickel/Gold coated plates

- High voltage up to 10kV

- Ultra-low noise

- Anti-magnetic

in

## ERS electronic GmbH

www.ers-gmbh.com, info@ers-gmbh.de

Figure 9: Die shift compensation by Nucleus FOWLP die bonder: a) before die shift compensation; and b) after die shift compensation. SOURCE: ASMPT

Figure 10: Wafer substrate warpage on a vacuum chuck. SOURCE: ASMPT

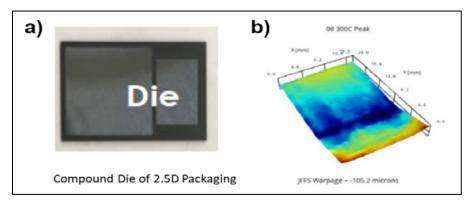

Figure 11: a) Compound die in a 2.5D package; and b) warpage scan image. SOURCE: ASMPT

decreases as a result of advanced node development, there are technical issues in removing all flux from beneath a die after die attachment via TCB. If flux residue remains beneath a die and is transferred to subsequent processes, the final yield will be reduced. The method of "flux-less TCB" is currently under development and it can be a solution for the above issues.

Large compound die handling issue. When the development trend of 2.5D packaging is toward including more chiplets in the same package, the compound die size increases to three, or even four times, the size of a reticle. Flip-chip bonding of extra large compound die on a substrate will become increasingly difficult as the size of compound die increases. A compound die consists of different-sized and thickness silicon dies and an EMC. The CTE values of silicon and EMC materials have a considerably wide range, therefore, die warpage will be compounded due to the differing degrees of expansion of the silicon and EMC materials.

Design of a die attach tool to handle an extra large compound is essential in ensuring good bondability and yield as follows (**Figure 11**): 1) Ensures temperature uniformity for a large heater for handling the extra large compound die; 2) Ensures warpage control by mechanical means; 3) A customized tooling design follows the characteristics of a particular compound die; and 4) Enables analysis of potential die crack/stress issues when handling a compound die from pick-up to attachment on the substrate

#### Summary

To enable heterogeneous integrations during the development of advanced packaging, a technique requiring highprecision die attach is necessary. The rising requirements of advanced packaging – in tandem with the development of advanced nodes – have raised the bar for highprecision die attach capabilities. In the new era of advanced packaging, selecting a dependable and long-term partner in equipment development to accomplish the arduous demands of advanced packaging development should be a top project goal.

#### References

- 1. "Technology Roadmap Frontend Manufacturing vs. Advanced Packaging," Yole Group, 2020.

- 2. J. H. Lau, et al., "Fan-out waferlevel packaging for heterogeneous integration," IEEE Trans. on Comp., Packaging and Mfg. Tech., vol. 8, no. 9, pp. 1544-1560, Sept. 2018, doi: 10.1109/TCPMT.2018.2848649.

- M. Li, et al., "Characterizations of fan-out wafer-level packaging," Inter. Symp. on Microelectronics. Vol. 2017, No. 1, International Microelectronics Assembly and Packaging Soc., 2017.

#### Biography

Percy Lam is Sales Manager at ASMPT Limited, Hong Kong, with responsibilities of product management and business development in the Advanced Packaging Technology Equipment sector. Areas covered are die attach solutions for FOWLP/PLP, with a focus on promoting package assembly equipment solutions for heterogeneous integration applications. He graduated from the Chinese U. of Hong Kong, majoring in Electronic Engineering. Email: percy.lam@asmpt.com

# Look Beyond

# **LB**Semicon

# **The Best Solution Provider**

LB Semicon provides the full **turn key service** including RDL, Fan-out WLP, WLCSP, Probe Test, Back-end and Bumping.

These services are mainly used to DDI, CIS, PMIC that are applied in TVs, smartphones and many other electronic devices.

Founded in 2000, LB Semicon has completed all the preparations to enter the FOWLP market, which is expected to grow further in the future.

- Semail marketing@lbsemicon.com

- Website www.lbsemicon.com

- Facebook www.facebook.com/lbsemicon

- in LinkedIn https://www.linkedin.com/company/lbsemicon

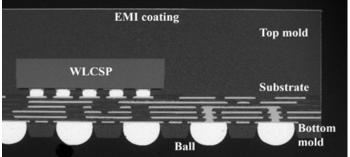

# **Double-sided SiP for 5G and wearable applications**

By David Wang, Mike Tsai, J. Y. Chen, YP Wang [Siliconware Precision Industries Co., Ltd]

he trend in medical wearable devices - such as those used for collecting medical data (e.g., heart rate detection, electrocardiographs (ECGs), and various sensors) - requires small form factor devices, smaller module sizes, multi-IC and component integration, low power consumption, and better heat dissipation. The module size of the single-sided system in package (SiP) device no longer meets these next-generation requirements. The double-sided SiP structure, however, is expected to provide solutions for more diverse applications of wearable products in the future. The double-sided SiP structure utilizes double-sided surface mount technology (SMT) and dual-sided molding to shrink the overall module size. Furthermore, it can be reduced in size so that it is about 40~60% lighter

and thinner than single-sided SiP devices to improve power supply efficiency and reduce noise emission.

In this article, we report on tests conducted on double-sided SiP structures to assess module-level warpage and thermal dissipation performance. The simulation and experiments included a design of experiments (DOE) on the molding process using different molding compounds. Regarding thermal performance, a solution was found that can improve performance 24~38%. The double-sided SiP module can provide an advanced solution to address the module size, cost, performance, and time-tomarket requirements for internet of things (IoT) devices and the wearables market.

The study described in this article will also demonstrate that the package die strength of the double-sided SiP structure

can be improved by selecting the proper strip grinding process. The extra low-k (ELK) material stress performance using a 3-point test methodology was also studied so as to select the suitable doublesided SiP structure for the end product of the board-level manufacturing process. From an electrical integration point of view, a shorter signal transmission path is required to get good electrical performance (i.e., signal integrity [SI] and power integrity [PI]) rather than a side by side flip-chip based structure. The performance verification was confirmed by simulation and measurement. The reliability testing verification includes temperature cycle testing (TCT), hightemperature storage life testing (HTSL) and unbiased highly accelerated stress testing (u-HAST) performed on the double-sided SiP structure.

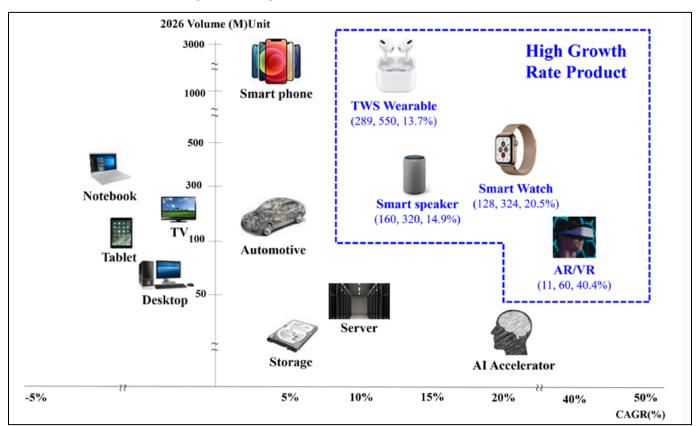

Figure 1: Market volume and SiP application. SOURCE: 2021 Vol., 2026 Vol., '21~'26 CAGR, PRISMARK

#### Introduction

The mobile phone and tablet computer markets have matured. The next fast-growing markets will be IoT and wearable devices. These products require a small size, a thin profile, good electrical properties and multi-functional requirements. From the perspective of packaging development, and keeping in mind the need for high-volume manufacturing of electronic products, the processing speed, and the required electrical characteristics, system on a chip (SoC) has been established as the key development direction for future electronic product design. However, with the increasing cost of SoC production in recent years, its development faces a bottleneck, therefore, the development of SiP is getting more attention by the industry.

In general, either die split (with the same function) or die partition (with a different function) will be the most effective methodology to reduce wafer cost, provide a small form factor, and realize the required product time-to-market. Chiplet integration is the way to make chips work as though they were one chip while actually being composed of several smaller ones. Chiplets are widely used to keep improving system performance despite the fact that traditional Moore's Law scaling is nearing its end.

Moore's Law is quickly approaching its limitations—its getting more difficult to reduce feature sizes. Heterogeneous integration by way of SiP, 2.5D/3D and fan-out solutions are driving the "More Than Moore" concept. The definition of heterogeneous integration includes single-chip, multi-chip, integrated photonics, microelectromechanical systems (MEMS), sensors, and radiofrequency devices. These packaging solutions are available today to make next-generation products a reality. SiP technology realizes the characteristics of light, thin, short, multifunctional, and low power consumption of the entire range of electronic products. The rise of lightweight products such as mobile devices and wearable devices make SiP an increasingly important packaging solution.

The current market share of smart watches indicates that the future of this market segment is still promising and also contributes to the trend toward SiP packaging. An advanced SiP package can reduce module size and enhance the system power. For example, a key item is connectivity with respect to receiving data from the network. The different application groups and their growth rates are shown in Figure 1. SPIL has learned from market trends that future packaging technologies will depend on increasing functionality and miniaturization. Using different assembly technologies to integrate and miniaturize components into a single package is similar to integrating active and passive partitions from other packaging platforms. The SiP platform can provide a good solution to meet performance, size, and low cost while also meeting the miniaturization requirements of each product and extend it to other applications such as IoT sensors, mobile phones, consumer products, and the automotive industry.

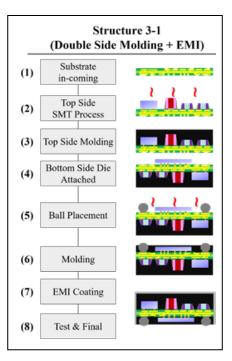

# Double-sided SiP structure (structure 3-2)

The following sections discuss thermal dissipation performance and warpage performance of structure 3-2/double-sided molding + thermal insulation material (TIM) (see Figure 2).

**Thermal dissipation performance verification.** 2D and 3D integration approaches are compared side by side with

respect to assembly methodology to reduce the size and space during the product layout arrangement stage (see Figure 2). A standard SiP package structure (Structure 1) is shown in Figure 2. Its advantage is that it uses the mature SMT process, but the tradeoff is the design layout limitation due to the side by side placement. Other key concerns are the small form factor as well as the thin thickness requirement that is limited on a single-sided SiP. A double-sided SiP with one side molding (Structure 2) can provide a smaller package (PKG) size, but thermal performance is the major challenge. Double-sided SiP modules (Structures 3-1, 3-2) have very small component to component spacing (40~60% smaller) and a one time molding technology. Compared to structure 2, both structures 3-1 and 3-2 with thermal pad and TIM, respectively, provide solutions that offer high heat dissipation.

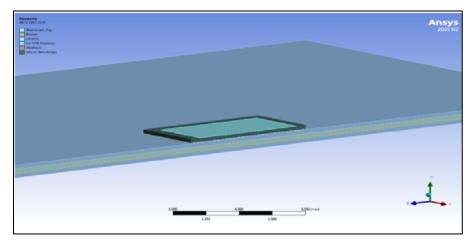

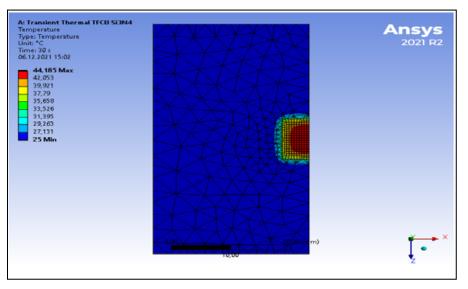

The double-sided SiP thermal test vehicle was designed with  $2 \times 2mm$  thermal measurement test die on the bottom side. The junction temperature of the thermal test die is measured through epoxy molding compound (EMC) material and a thermal e-pad to verify the thermal dissipation performance result, which is directly correlated to the simulation data collection. The thermal PCB was designed in 4L PCB (4"x4.5") and measured under still air conditions with the power at 1W. Junctionto-air resistance ( $\theta$ JA) defines the heat flow between the chip's surface and air. Junctionto-board resistance ( $\theta$ JB) defines the heat flow between the chip's surface and the board's surface. The unit is mounted on a measurement printed circuit board (PCB) and connected with measured output I/O.

The simulation result shows a worse  $\theta JA$  with a 1.3x ratio and the  $\theta JB$  with 1.2y ratio by using a normal EMC (K=1W/mK) compared to a single-sided SiP. A

| Item                 | Structure 1 | Structure 2   | Structure 3-1                        | Structure 3-2                     | Structure 3-3                |

|----------------------|-------------|---------------|--------------------------------------|-----------------------------------|------------------------------|

| Feature              | Single Side | Double Side   | Double Side Molding<br>+ Thermal Pad | Double Side Molding<br>+ TIM      | Double Side Molding<br>+ EMI |

| Package<br>Structure | <b></b>     |               |                                      |                                   | <del>7 llag</del>            |

| PKG Size             | 100%        | Reduce 40~60% |                                      |                                   |                              |

| Thermal<br>Solution  | NA          | NA            | Add Thermal Pad                      | Add Thermal Interface<br>Material | NA                           |

Figure 2: Comparison of different SiP design structures.

# smiths interconnect

# Cutting-edge Connectivity DaVinci Micro Test Socket

The coaxial structure of the DaVinci Micro test socket provides ideal pin to pin isolation reducing the effect of cross talk during testing. This allows for at speed functional testing of your IC.

- Controlled impedance interface

- Spring probe technology with homogenous alloy, protects against solder build up and increased probe life

- Optimized for power integrity of DUT

Mobile SoC

- Patented insulated metal socket housing provides un-matched mechanical strength

- For use with manual test, bench test and HVM Production testing using the same socket

DaVinci Micro inherits the DaVinci coaxial technology for IC applications to 350µm pitch. DaVinci Micro's fully shielded signal path negates the effects of cross-talk during testing, allowing an immediate yield enhancement over non-DaVinci products.

High Speed Digital

Memory

double-sided SiP – by using high thermal EMC material (K=2.5W/mK) – achieves a 20%  $\theta$ JA (1.1x) thermal enhancement, and a 30%  $\theta$ JB (0.9y) thermal enhancement when compared to using a normal EMC material (K=1.0W/mK). When a thermal interface material (TIM) is used (Ag epoxy with 25W/mK), the simulation data shows the 0.99x  $\theta$ JA ratio with a 24% thermal enhancement and a 0.75y  $\theta$ JB with a 38% thermal enhancement.

Warpage performance verification. Another key challenge of the proposed double-sided SiP platform is warpage performance. The DOE design factors are defined as standard normal EMC, thermal EMC type factor and TIM material. The package warpage performance is measured using the Shadow Moiré methodology (JEDEC standard). The normal EMC with TIM has a better warpage result (room temperature: -10µm; high temperature: 13µm) than using a high thermal EMC material without a TIM (room temperature: -16µm; high temperature: 8µm). The difference in these two results is due to the low coefficient of thermal expansion (CTE) mismatch during molding of the structure. Based on the signed warpage chart result, three legs are within the JEDEC warpage requirement (max. 80µm). And both instances of the normal EMC with a TIM can pass the warpage requirement for the double-sided SiP structure.

# Double-sided SiP structure (structure 3-3)

The sections below discuss electrical performance verification and structural strength analysis of structure 3-3/double-sided molding + EMI (see Figure 2).

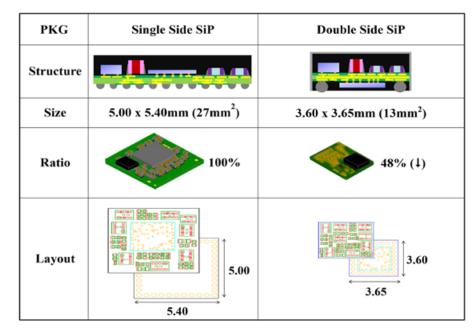

Electrical performance verification. Structure 3-3 shown in Figure 2 and the process flow shown in Figure 3 are responses to the demand for miniaturization of products. Figure 3 provides examples of SiP structure designs from single-sided SiP to double-sided SiP that enable the reduction in package size from 5.00 x 5.40mm  $(27mm^2)$  to 3.60 x 3.65mm  $(13mm^2)$ . The high degree of integration along with achieving the required performance are achieved by using a double-sided stacking process as shown in Figure 4. The total area is then reduced by 50%, and better electrical performance (>40%) is achieved by using a vertical signal transmission path and adding a ground (GND) plane on L2. The RLC extraction can, therefore, be reduced by using a double-sided SiP

Figure 3: Process flow of a double-sided SiP structure (double-sided molding + EMI).

| Structure          | Net<br>Name | Ls (nH)         | Cs (pF)         | R (m Ohm)        |

|--------------------|-------------|-----------------|-----------------|------------------|

| Single Side        | Α           | 1.177           | 0.801           | 242.22           |

| SiP                | В           | 1.185           | 0.806           | 223.40           |

| Double Side<br>SiP | А           | 0.705<br>(40%1) | 0.327<br>(59%1) | 104.32<br>(57%1) |

|                    | В           | 0.503<br>(58%1) | 0.268           | 63.39<br>(72%1)  |

Table 1: RLC extraction simulation comparison result.

Figure 4: Comparison of single-sided SiP and double-sided SiP structures.

structure. **Table 1** shows the simulation result for RLC extraction (i.e., R: lower resistance is better for signal loss, L: lower inductance is better for signal propagation delay control, C: lower capacitance is better for noise and voltage control).

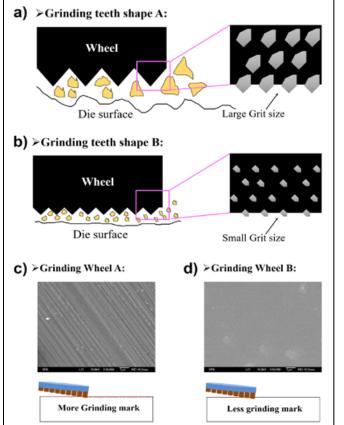

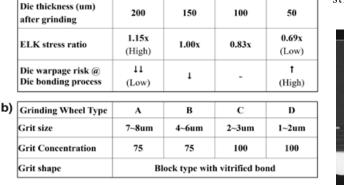

Structural strength analysis. In this experiment, the warpage performance of different die thicknesses and of different packaged die strengths are studiedthis is important because the thickness requirement is getting critical for doublesided SiP platforms. In order to evaluate the optimal die thickness and die strength, a series of grinding wheel parameters were selected-for example, the grit sizes of the teeth, concentrations, and shapes of the various teeth (see Figure 5a). As shown in Figure 5b, the scanning electron microscope (SEM) image shows how a different grinding wheel selection will result in a surface mark difference. Grinding wheel A is rougher than grinding wheel B. The finer grinding wheel will have a smooth surface, but a longer manufacturing

> time is required to meet the target die thickness because of the small grit size.

Another crucial parameter to be considered when optimizing ELK stress in a double-sided SiP structure is die thickness. A stress analysis was conducted to evaluate ELK stress as a function of die thickness at 200µm, 150µm, 100µm,

## High Pin Count

Pitch ≥0.80mm Pin Count ≥10.000

Coplanarity <0.35mm

#### WLCSP Probe Head

Pitch ≥0.15mm Pin Count ≤6000

Longevity >1000K

#### Coaxial Bitch

Pitch ≥0.40mm

Insertion Loss >40GHz@-1dB Crosstalk >35GHz@-52dB

## Probe Pin

Pitch ≥0.12mm

Power ≤6.5A

Frequency >140GHz

Heatsink <100W

Heatpipe 100W - 1000W

Liquid Cooling 300W - 1500W

tts REV:0

Pitch ≥0.35mm Insertion Loss >60GHz@-1dB

Return Loss >30GHz@-20dB

Figure 5: a) Grinding teeth shape A; b) Grinding teeth shape B; c) Grinding wheel A; and d) Grinding wheel B.

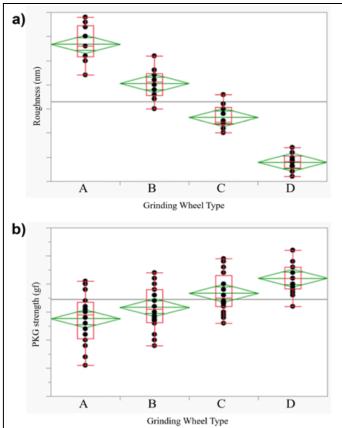

Figure 6: a) Roughness vs. grinding wheel type; and b) Package strength vs. grinding wheel type.

and 50µm. After the grinding process, the bottom thinner die resulted in the lower ELK material stress ratio, although there is a process risk during die bonding because of die warpage. The summary of die thickness impact on ELK stress in a double-sided SiP structure is shown in Table 2a.

A 3-point bending strength test was also conducted to confirm package strength, which is modulated by the external

Leg1

Items

a)

bending stress. The bending test also allows the determination of flexibility, bending strength, breaking strength and the fracture resistance of the material. During the bending test, deformation occurs at the midpoint of the test samples, and the bending force causes a concave surface or bending fracture. A force is applied to the test sample at its midpoint to form a concave surface with a pre-defined radius

of curvature. The package (PKG) die strength is defined

as the maximum stress that an object can withstand before being bent and broken.

To compare the effect of grinding wheel type, we selected four types of wheels for a grinding process DOE study. The grit size of the grinding wheel ranged from 7~8 $\mu$ m to 1~2 $\mu$ m, and the grit concentration ranged from 75 to 100, and the grit shape (i.e., block type of grit shape with vitrified bond structure); these parameters are summarized in Table 2b.

We also measured the die roughness on a double-sided SiP structure with different

Leg2

Leg3

Leg4

Table 2: Structure strength analysis results: a) Summary of die thickness

impact on ELK stress in a double-sided SiP structure; and b) Comparison of the

impact of various grit sizes with respect to grinding wheel types.

Figure 7: Double-sided SiP of a BGA ball cross-section scanning electron microscope (SEM) result.

| # | Reliability Test Items | Read Point  | Sample size | O/S Test and SAT<br>Result |

|---|------------------------|-------------|-------------|----------------------------|

| 1 | Time Zero              | Tθ          | 0 / 231 pcs | All Pass                   |

| 2 | MSL3                   | Pre-con     | 0 / 154 pcs | All Pass                   |

| 3 | TCT (-55 °C ~+125 °C ) | 1000 Cycles | 0 / 77 pcs  | All Pass                   |

| 4 | u-HAST (130°C/85%RH)   | 96 Hours    | 0 / 77 pcs  | All Pass                   |

| 5 | HTS (150°C)            | 1000 Hours  | 0 / 77 pcs  | All Pass                   |

Table 3: Summary of reliability tests conducted.

grinding wheel types (A, B, C and D). The roughness level was such that A > B > C>D (i.e, wheel A is rougher than the others). We used the 3-point test to check the package (PKG) die strength. The greater PKG strength was achieved using a fine grit size with wheel D because of the higher die strength that can be accomplished with the smooth silicon die surface and mold surface. The test results of the roughness and 3-point bending using the different grinding wheel types are shown in Figures 6a and 6b.

#### **Reliability results**

The grinding wheel selection can enhance the package strength and reduce the risk of die and package cracking caused by structural warpage. The finer grinding wheel type (wheel type D) resulted in a greater package die strength due to the smooth silicon die and mold surface but in contrast, it increased process time. The double-sided cross-section image of a SiP structure is shown in **Figure 7**. The SMT result shows a double-sided SiP with top side molding, bottom molding, and the main die.

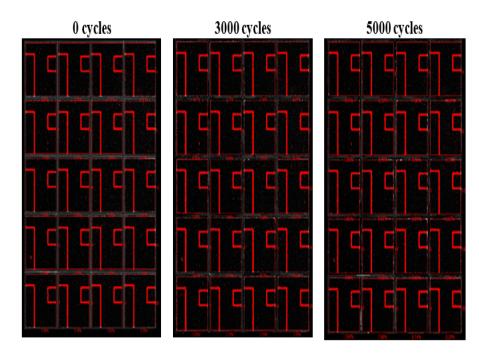

In this study, the following JEDEC reliability test conditions were used: precondition with MSL3, temperature cycling test (TCT) at -55–125°C for 1,000 cycles, un-biased highly accelerated stress testing (u-HAST) at 130°C for 96 hours, and hightemperature storage life (HTSL) testing at 150°C for 1,000 hours. The open/short (O/ S) test and scanning acoustic tomography (SAT) inspection were done, and all reliability test results had passed as shown in **Table 3**.

#### Summary

Compared to a single-sided SiP structure, a double-sided SiP structure can provide good thermal performance by using a thermal pad design and TIM (i.e., Ag epoxy with 25W/mK with 0.99x  $\theta$ JA ratio with 24% thermal enhancement, and 0.75y  $\theta$ JB with a 38% thermal enhancement). The normal EMC with TIM achieved a better warpage result because of the low CTE mismatch during the molding process done on the structure.

The double-sided SiP package provides the small form factor and good electrical performance required for 5G and wearable electronics applications. For the advanced double-sided SiP structure, we studied the effects of different die thicknesses and grinding wheel roughness values on the package strength. Also, a 3-point bending test methodology was selected to evaluate the suitability of the double-sided SiP structure for use in the end product at the board-level manufacturing process. The finer grinding wheel type (wheel type D) provided a better package die strength due to the smooth silicon die and mold surface, but it resulted in a lower grinding throughput. To achieve a higher throughput, grinding wheel type A would be the best choice. Finally, the double-sided SiP structure passed reliability requirements including pre-condition MSL 3, TCT (1,000 cycles), u-HAST (96 hours) and HTSL (1,000 hours). The double-sided SiP can provide an innovative solution to address the small form factor, cost reduction, electrical performance, and time-to-market requirements for 5G and wearable products in the near future.

#### References

- J-Y. Lai, T-Y. Chen, M-H. Wang, M-K. Shih, D. Tarng, C-P. Hung, "Characterization of dual side molding SiP module," Proc. 67th Electronic Comp. and Tech. Conf. (ECTC), 2017, pp. 1039-1044.

- M. Tsai, R. Chiu, D. Huang, F. Kao, E. He, J. Y. Chen, et al., "Innovative packaging solutions of 3D double side molding with system in package for IoT and 5G application," Proc. 69th ECTC, 2019, pp. 700-706.

- M. Tsai, R. Chiu, Ming-fan Tsai, E. He, E. Yang, T. Chang, et al., "Heterogeneous integration of double side SiP for IoT and 5G application," Proc. 71st ECTC, 2021, pp. 1038-1043.

- T-W. Liao, W-H. Lai, H-C. Shih, D-L. Chen, D. Tarng, CP Hung, "Mechanical reliability analysis of dual side molding SiP module," Proc. 2021 Inter. Conf. on Electronics Packaging (ICEP), 2021, pp. 93-94.

- B-H. Ma, D. Ho, Y-P. Wang, F. Yen, S. Guo, R. Chiu, "Highly integrated assembly processes solutions for double-sided-SiP package," Proc. IEEE 8th Elec. System-Integration Tech. Conf. (ESTC), 2020.

- M. Tsai, K. Chang, R. Hsieh, W. Li, K. Chang, R. Chiu, et al., "Double side SiP of structure strength analysis for 5G and wearable application," Proc. 72nd ECTC, 2022, pp. 18-23.

#### **Biographies**

David Wang is a Department Manager, Corporate R&D at Siliconware Precision Industries Co., Ltd., Taichung, Taiwan, R.O.C. He has over 25 years of industry experience especially focusing on fan-out packaging technology development and advanced assembly analysis. He has published over 10 conference papers and patents. Email: davidwangl@spil.com.tw

Mike Tsai is a Technical Deputy Manager, Advanced SiP Product Integration at Siliconware Precision Industries Co., Ltd., Taichung, Taiwan, R.O.C. He received his MS degree from National Chung Hsing U. (NCHU). He has over 10 years of job experience and published 11 papers in the semiconductor industry, with a special focus on FC, PoP and SiP of advanced assembly technology.

WX3000<sup>™</sup> Metrology and Inspection Systems for Wafer-Level and Advanced Packaging

# 2-3X Faster with High Resolution and High Accuracy

WX3000 3D and 2D metrology and inspection system provides the ultimate combination of high speed, high resolution and high accuracy for wafer-level and advanced packaging applications to improve yields and processes.

#### Powered by Multi-Reflection Suppression (MRS) Sensor Technology

The 3-micron NanoResolution (X/Y resolution of 3 micron, Z resolution of 50 nanometer) MRS sensor enables metrology grade accuracy with superior 100% 3D and 2D measurement performance for features as small as 25-micron.

100% 3D and 2D metrology and inspection can be completed simultaneously at high speed (25 300mm wafers/hour and 55 200mm wafers/hour) as compared to a slow method that requires two separate scans for 2D and 3D, and only a sampling process.

www.cyberoptics.com

opyright © 2022. CyberOptics Corporation. All rights reserved.

# Meeting cost and technology requirements using MLF/QFN

By Marc Mangrum [Amkor Technology, Inc.]

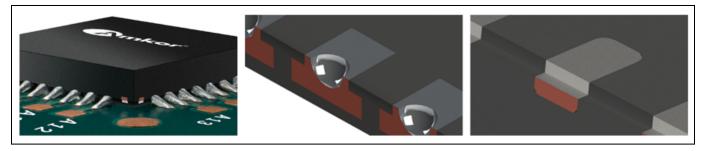

*icro*LeadFrame (MLF)/ quad flat no-lead (QFN) packaging technology

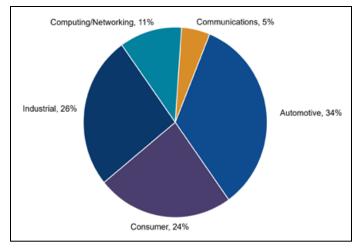

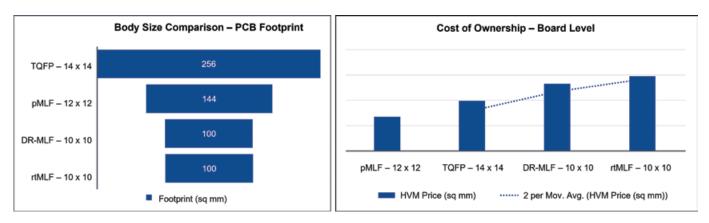

is the fastest growing IC packaging solution today. From a market segment perspective, MLF packaging solutions represent more than a 111B-unit market for 2022 across five markets: automotive, consumer, industrial, networking, and communications (Figure 1). The package solution requirements across these markets vary but, the fundamental values the MLF packaging brings to each one is consistently the same: 1) a flexible form factor, 2) adaptable interconnect technology, 3) electrical and thermal performance, and 4) a cost-effective solution.

#### Flexible form factor

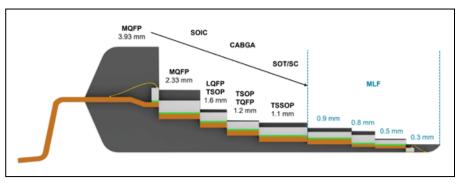

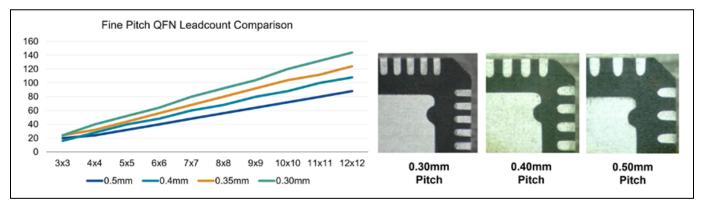

The flexible form factor of MLF packaging enables the technology to service all markets, meeting unique dimensional, environmental and application requirements. In these markets, the MLF packaging solution is being utilized to solve space and functionality challenges. As an example, the capability to form cavities has resulted in the MLF becoming a widely used and versatile solution in the microelectromechanical systems (MEMS) and sensor markets. The automotive industry continues to rely on this technology for solutions in all areas of the automotive electronics deployment. Applications range from infotainment systems to magnetic sensors for steering controls, to even complex moisture sensing systems for automatic windshield wiper systems and battery control management systems. Body sizes ranging from <1.0mm x 1.0mm to >12mm x 12mm are available (Figure 2).

The broad range of JEDEC package thicknesses enables the MLF packaging technology to meet the demanding size requirements of the portable handheld, Internet of Things (IoT), gaming networking/computer, industrial and the broader consumer markets. Typical body thickness ranges from 2mm to 0.30mm. Ultra-thin capability is also possible down to less than  $200\mu$ m using both wire-bond and flip-chip interconnect solutions. The thinnest IC packaging solution is the die itself followed by wafer-level chip-scale packaging (WLCSP) and then the MLF over molded packaging technology. As shown in **Figure 3**, MLF represents the conditioning (HVAC) systems, medical devices, satellite systems, audio/ visual home electronics, and home and commercial appliances. In any identified electronic product, there is a 99.9% chance a device utilizing QFN packaging technology is in it. The wide use of this packaging technology is not just about body thickness either. Body size, lead

thinnest over molded leadframe technology.