# Chip Scale Review®

ChipScaleReview.com

The Future of Semiconductor Packaging

Volume 25, Number 1

January • February 2021

Emerging process and assembly challenges in electronics manufacturing page 12

- Wafer-scale S-MCM

- 600mm WLFO on PLP

- Revealing invisible defects on large 600mm panels

- Going beyond traditional temporary bonding materials

- Heterogeneous integration prompts test content to "shift left"

- High-throughput flexible direct imaging for packaging/MEMS fabrication

- Extreme Si thinning and nano-TSVs to advance 3D heterogeneous integration

Subscribe

## Making the connected world possible™

# Palomar Die Bonders

High accuracy, high flexibility eutectic and epoxy die bonding specializing in precision assembly of complex packages

# Palomar Wire & Wedge Bonders

High-speed, robust chip-to-die interconnections, ball-and-stitch, ball bumping, wedge and ribbon bonding

# Innovation Centers

Specializing in contract manufacturing and process development to deliver rapid ROI for new product introductions

# SST Vacuum Reflow Systems

Unique combination of vacuum, pressure and heat to create highly reliable, void-free solder

Advanced Photonic & Microelectronic Packaging Solutions delivering improved yield, reduced assembly times and rapid ROI

www.PalomarTechnologies.com

# CONTENTS

#### January • February 2021 Volume 25, Number 1

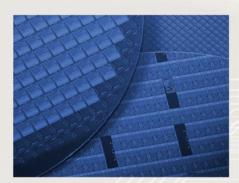

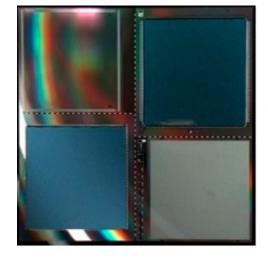

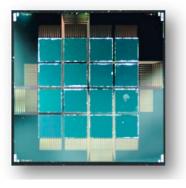

Cover image represents bare die on a wafer. These die were used in the assembly of a MEMS package, which was integrated into a pressure sensor. MEMS are responsible for the sensing element of heterogeneous integration and are one of many application types that will advance tremendously by leveraging intricate multi-die designs to deliver greater performance in a more compact footprint.

Photo courtesy of Universal Instruments

#### **DEPARTMENTS**

4 FROM THE EDITOR

The wonders of quantum computing

By Debra Vogler, Sr. Technical Editor [Chip Scale Review]

7 TECHNOLOGY TRENDS

Heterogeneous integration prompts test

content to "shift left"

By Dave Armstrong

[Advantest America, Inc.]

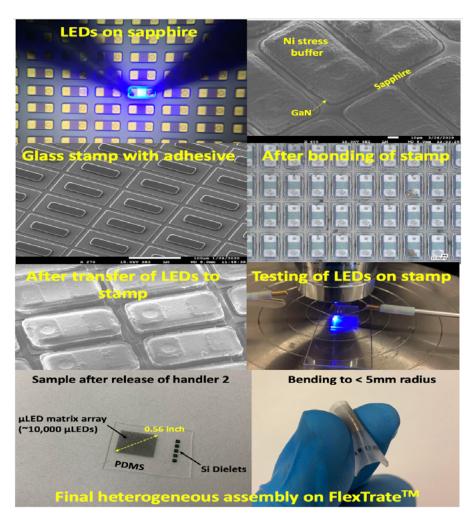

54 TECHNOLOGY TRENDS

Adhesive bonding for flexible microLED display assembly

By Goutham Ezhilarasu, Subramanian Iyer [UCLA] Ajit Paranjpe [Veeco Instruments, Inc.] Jay Lee [DISCO Corporation] Frank Wei [DISCO Hi-Tec America, Inc.]

## DIE-TO-WAFER (D2W) BONDING SOLUTIONS

- Fusion and hybrid bonding for next-generation heterogeneous integration

- Collective D2W bonding enabled by extensive knowledge in carrier preparation and die handling

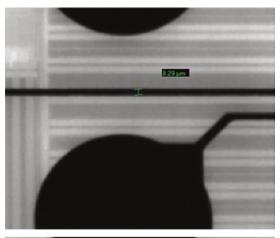

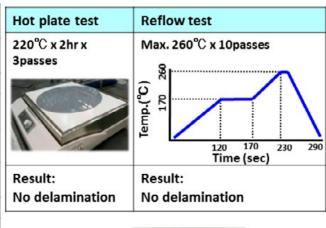

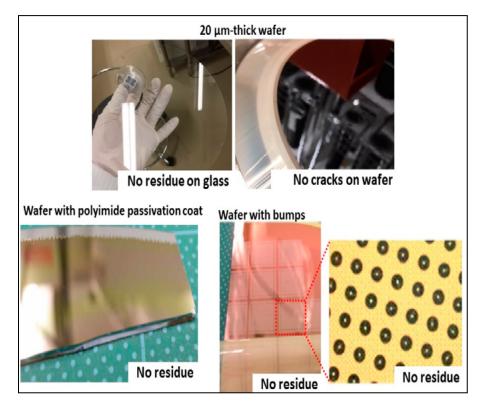

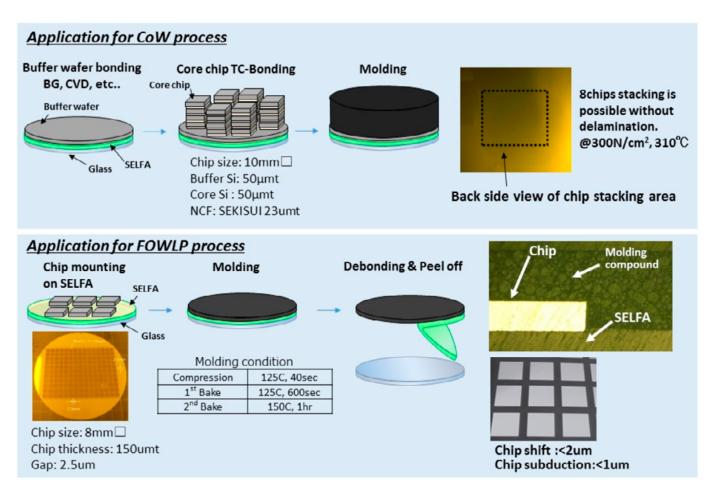

- Direct placement D2W activation and cleaning complete solution with EVG®320 D2W

- Production-ready equipment solutions for successful integration of chiplets

- Heterogeneous Integration Competence Center™ serving as leading-edge incubation center for customers and partners

## Chip Scale Review

ChlpScaleReview.co

The Future of Semiconductor Packagin

#### **STAFF**

Kim Newman Publisher knewman@chipscalereview.com Lawrence Michaels Managing Director/Editor Imichaels@chipscalereview.com Debra Vogler Senior Technical Editor dvogler@chipscalereview.com

#### **CONTRIBUTING EDITORS**

Steffen Kröhnert - Advanced Packaging steffen.kroehnert@espat-consulting.com John L. Lau, Ph.D - Advanced Packaging john\_lau@unimicron.com

Ephraim Suhir, Ph.D - Reliability

suhire@aol.com

Rao R. Tummala, Ph.D - Advanced Packaging rao.tummala@ece.gatech.edu

#### **EDITORIAL ADVISORS**

Andy Mackie, Ph.D (Chair) - Indium Corporation Rolf Aschenbrenner, Dipl.-Phys. - Fraunhofer IZM Arun Gowda, Ph.D - GE Global Research John Lau, Ph.D - Unimicron Leon Lin Tingyu, Ph.D - National Center for Advanced Packaging (NCAP China)

#### SUBSCRIPTION-INQUIRIES

Chip Scale Review

All subscription changes, additions, deletions to any and all subscriptions should be made by email only to subs@chipscalereview.com

Advertising Production Inquiries: **Lawrence Michaels**

Imichaels@chipscalereview.com

Copyright © 2021 Haley Publishing Inc.

Chip Scale Review (ISSN 1526-1344) is a registered trademark of

Haley Publishing Inc. All rights reserved.

Subscriptions in the U.S. are available without charge to qualified individuals in the electronics industry. Chip Scale Review, (ISSN 1526-1344), is published six times a year with issues in January-February, March-April, May-June, July-August, September-October and November-December. Periodical

postage paid at Gilroy, Calif., and additional offices.

POSTMASTER: Send address changes to Chip Scale Review magazine P.O. Box 2165  $\,$

Morgan Hill, CA 95038 Tel: +1-408-846-8580

E-Mail: subs@chipscalereview.com

Printed in the United States

Volume 25, Number 1 January • February 2021

#### **FEATURE ARTICLES**

#### 12 Emerging process and assembly challenges in electronics manufacturing

By Glenn Farris [Universal Instruments]

## 18 Wafer-scale superconducting multi-chip module

By Rabindra N. Das, Vladimir Bolkhovsky,

Alex Wynn, Ravi Rastogi, Scott Zarr, Leonard M. Johnson

[Quantum Information and Integrated Nanosystems

Group, MIT Lincoln Laboratory]

## 25 600mm wafer-level fan-out on panel-level processing with 6-sided die protection

By Jacinta Aman Lim, YunMook Park, Byung Cheol Kim, Edil Devera [nepes]

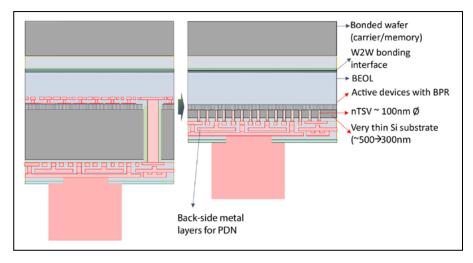

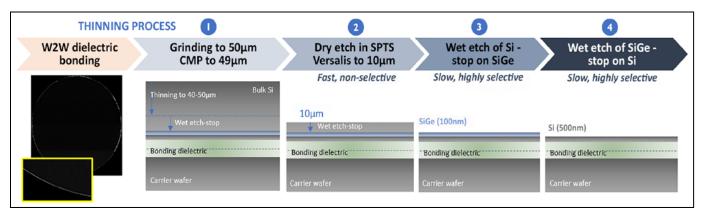

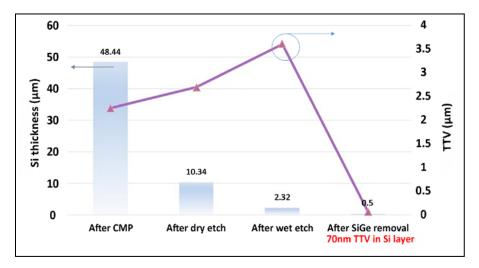

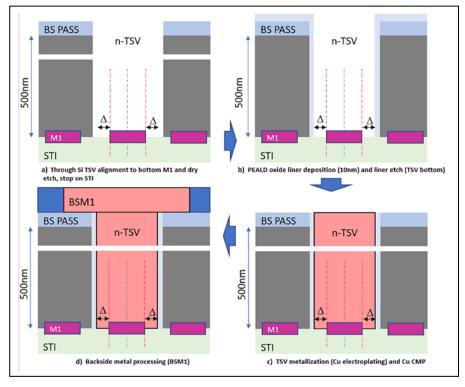

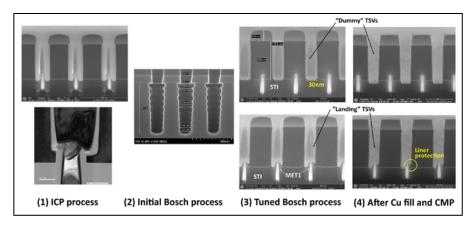

#### 34 Extreme Si thinning and nano-TSVs to advance 3D heterogeneous integration

By Dave Thomas [SPTS Technologies]

Anne Jourdain [imec]

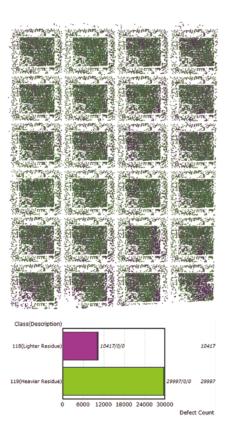

## 39 Revealing invisible defects on large 600mm panels

By Woo Young Han [Onto Innovation]

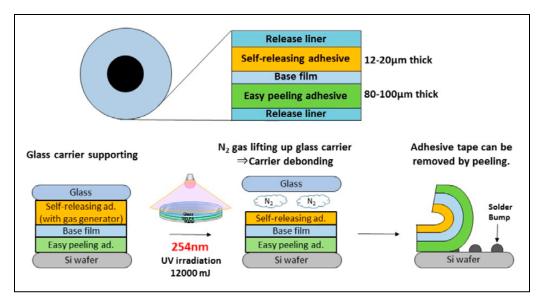

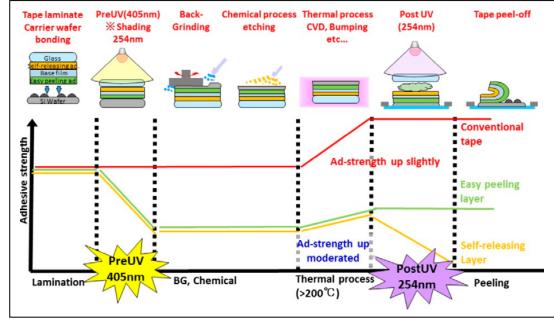

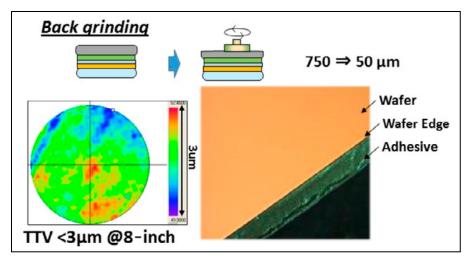

## 44 Going beyond traditional temporary bonding materials

By Taro Shiojima, Munehiro Hatai, Minoru Inoue, Ryoichi Watanabe, Toshio Enami, Daihei Sugita [SEKISUI CHEMICAL CO., LTD.]

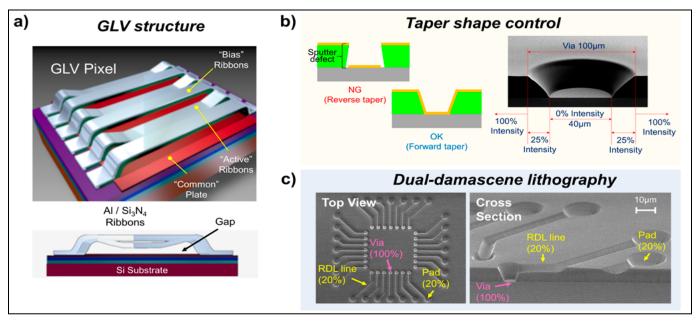

## 50 High-throughput flexible direct imaging for packaging/MEMS fabrication

By Shota Majima, David Hyde [SCREEN Semiconductor Solutions Co., Ltd.]

## FROM THE EDITOR

## The wonders of quantum computing

By Debra Vogler, Sr. Technical Editor

hen I first laid eyes on the IBM Q System One computer (an "integrated universal approximate quantum computing system" according to IBM's news release) at SEMICON West 2019, I was stunned. I had seen photos of it beforehand, but in person—it was a "wow" moment. I felt the same way I did as a kid when President Kennedy challenged the nation to land a man on the moon-and then watched it happen less than 10 years later. When quantum computing (QC) was discussed at IWLPC 2019, I felt challenged as senior technical editor of this magazine to solicit content from industry experts that would tackle the impact of QC and applications such as artificial intelligence (AI) on the future of packaging and test. (While AI also uses classical computing, it will benefit from OC capabilities as that technology is further developed.)

Industry experts heeded *Chip Scale Review*'s call for QC/AI/next-generation computing content, and as a result, we were able to publish several relevant articles in 2020 that included:

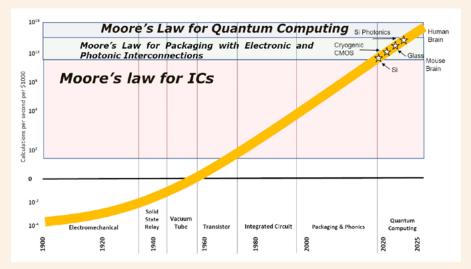

- "Post-Moore's Law electronics: now, until quantum electronics," (R. Tummala/Georgia Tech, Mar/Apr);

- AI's impact on 3D packaging: heterogeneous integration," (S. Kumar/Yole Développement, Korea, May/June);

- 3) "Electronic packaging for future electronic systems," (M. Töpper, T. Braun, R. Aschenbrenner/Fraunhofer IZM, Jul/Aug);

- "Enabling AI with heterogeneous integration," (N. Fan/ASM Pacific Technology Ltd., Sept/Oct);

- 5) "A deep-learning solution for heterogeneous package inspection,"

(S. Chitchian/INTEKPLUS Corporation Ltd., Sept/Oct);

- "Enabling AI with heterogeneous integration," (A. Kumar, M. Farooq/IBM Research, Nov/Dec).

In 2021, CSR will be asking industry experts to, once again, put forth the vision that will drive the packaging and test sectors. Heterogeneous integration will continue to play a major role and, as semiconductor processes continue to show signs of blurring the boundaries between front-end-of-line, middle-end-of-line, and back-end-of-line, there will undoubtedly be more blurring of the lines among our standard coverage topics. QC will continue to be a topic of significant interest. In our first issue of the new year, members of the Quantum Information and Integrated Nanosystems Group at MIT Lincoln Laboratory (R. Das, V. Bolkhovsky, A. Wynn, R. Rastogi, S. Zarr, L. Johnson) present their strategy for using laser direct write (LDW) and optical lithography to fabricate 200mm waferscale superconducting multi-chip modules (S-MCM) for interconnecting multiple active superconducting flux quantum (SFQ) chips for next-generation cryogenic processing systems. The authors note that, "the demand for superconducting computing scalability beyond arrays of a few superconducting chips is driving the need for greater wiring densities and more functionality onto a single cryogenic package."

As the industry continues implementation of QC and AI, I look forward to receiving abstracts from our long-time authors, as well as those who have not written for CSR before. Our readers need articles that shed light on the challenges with respect to packaging qubits, such as: reducing electromigration (EM) loss, the impact of dielectric loss on how to scale wiring layers, the impact of a low thermal budget for Josephson junctions (JJs), and developing superconducting throughsilicon vias (TSVs), among others (ref.: "Fabricating Quantum Technologies," G. Ribeill/Raytheon Technologies, SEMICON West 2020).

Here's looking to innovation (and to better times) in 2021.

Computing performance driven by Moore's Law and post-Moore's Law technologies. SOURCE: "Post-Moore's Law electronics: now, until quantum electronics," (R. Tummala, *Chip Scale Review*, Mar/Apr 2020)

## **Semiconductor Package Inspection**

## INTEK-PLUS

## Fast, Accurate, and the most Advanced

INTEKPLUS specializes in 2D and 3D Surface Inspection and Metrology for Semiconductor Package Products. We provide the World's fastest Inspection Capability to achieve High Productivity.

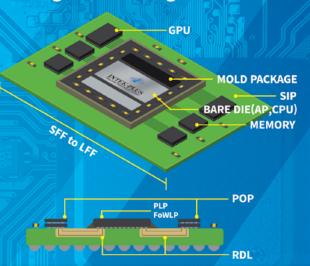

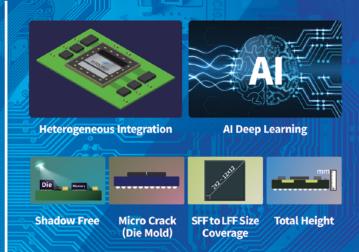

#### **High-end Package Trends**

#### **Supreme Vision Solution**

**Out-Tray Inspection**

iPIS-140 / 240 / 240+ / 340

\* Hexa Model for 4 Sides

In-Tray Inspection

iPIS-380 / 560 / 580

\* Hexa Model for 4 Sides

Inspection + Tape & Reel + ARC

iPIS-380TR / 560TR / 580TR

- \* TR Model for Tape & Reel

- \* ARC Ext. for Full Automation

Looking for Sales Representative in Europe, America, Southeast Asia(Singapore, Malaysia, Philippines, Thailand, Vietnam)

#263, Techno 2-ro, Yuseong-Gu, Daejeon, 34026 Korea Tel:+82-42-930-9900 Fax:+82-42-930-9999 For more information www.intekplus.com / sales1@intekplus.com

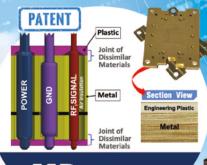

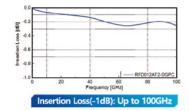

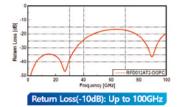

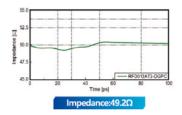

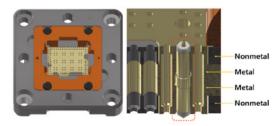

# Connectivity

Smiths Interconnect test sockets and probe cards offer superior quality and reliability in semiconductor test applications.

Leading-edge engineering, development and simulation expertise supporting automated, system-level and development test platforms for area array, wafer level, peripheral and PoP devices.

#### **Area Array Test**

- In-house maintenance and contact replacement

- Entirely shielded signal path\*

- Controlled impedance\*

- High speed test to 67GHz Analog & 56Gbps Digital\*

- System simulation modeling

\*DaVinci Series

#### Wafer Level Test

- Reliable RF signal integrity

- Excellent compliance and contact force

- Simple maintenance

- Quick installation

## **TECHNOLOGY TRENDS**

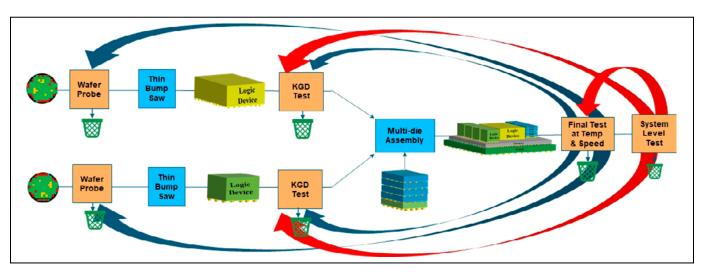

# Heterogeneous integration prompts test content to "shift left"

By Dave Armstrong [Advantest America, Inc.]

eterogeneous integration and the resulting need for knowngood die (KGD) are driving the transition to a new test flow, best described as "shift left." With this flow, test functions once performed at system-level test are moving to final test, or a KGD test step that occurs after thin-bump sawing. Similarly, final-test functions are shifting left to the KGD step or to the wafer-probing step (Figure 1).

The need for this shift-left flow arises because many companies today are starting to ship KGD-including some very complex artificial intelligence (AI) devices— and others are shipping memory stacks. In these examples, there is no longer a packaged-device ship location. Shipping parts in die form represents a new ship location, and you have a critical need for more test content prior to that ship location to make sure the devices are of sufficient quality for subsequent heterogeneous integration. Indeed, you may not have a profitable product if you do not push your quality upstream. Pushing quality upstream gets you profit downstream.

Consider the traditional test flow. At the wafer-test step, automatic test equipment

and a wafer prober find hard rejects and perform scan and some functional test at one temperature. At the KGD test step, automatic test equipment (ATE) and a singulated die prober confirm scan and functional tests at a second temperature. At final test, ATE and a device/die handler with active thermal control perform packaged device test, extended scan test, parametric performance test, at-speed test, high-power test, and stress tests. And finally, a system-level tester repeats packaged device tests and performs boot-up tests and fuse blowing.

The flow described above may have been sufficient five or six years ago when multidie integrations might have had one large logic part and four high-bandwidth memory (HBM) devices. But today, people are moving to heterogeneous devices that have 30, 40, or 50 devices on them, and the error elements of each one of those die multiply together. If you have 0.99% good devices and you multiply all the error elements together, you could very easily end up with an assembly that has only a 60% probability of being good. So the fundamental challenge is that you need to get not just 0.99% good parts, but 0.9999% good parts. This is where

people suggest that we are moving past the parts per million into an industry where parts per billion is the new norm.

As a result of the new quality requirements noted above, you have to do a lot more testing at wafer, or perhaps after thin bump sawing, where you can actually perform active-thermal-control thermal testing, where you can do full-power testing of your part, and where you can do at-speed testing of your part. People are finding that by being able to do at-speed, at-power test of KGD, they can do pretty much all the testing that they used to do at final test. In turn, final test is becoming more of a system-level test step—performing boot-up testing, for example, and checking whether your software and firmware are working.

A big challenge for heterogeneous integration is simple continuity. You might have 40,000 bumps on your logic part, and you may have ten of those logic parts, so you easily could have a half a million bumps that have to make good contact. And then you have other parts with other I/O, so you have a very large amount of continuity checks and interface tests to perform. And that's where some of the IEEE standards come into play, because you can't necessarily

Figure 1: Test content is shifting left, from system-level test to final test and KGD test—and from final test to KGD test and wafer-level test.

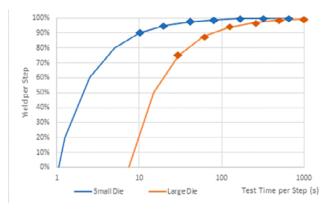

**Figure 2:** This graph shows yield per step vs. test time per step for successive test steps; half the remaining faults were detected in the next step, which takes twice as long as the previous step.

check those externally. Consequently, IEEE P1500 and related I/O tests are critical.

There are some misperceptions in the industry that need to be addressed. For example, you may ask, "If I get 90% yield, have I got a 90% good product?" The answer is no. You only know that 90% of the tests you have run yield positively, but the tests you have run may not cover 90% of the potential faults. And then the next question is, "If I spent ten seconds to get to 90%, how long do I need to spend to get the rest of the percentage?" And here you face the law of diminishing returns. You can approach 100% coverage exponentially, but some faults you are never going to find.

#### Math examples

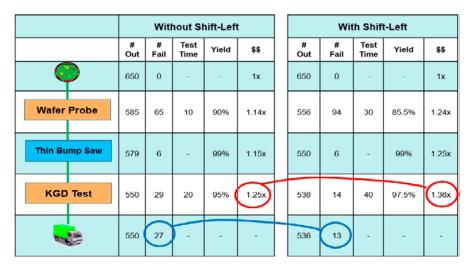

Consider the math behind a sequence of KGD test steps, based on some reasonable assumptions regarding test time and quality of product. Assume half of remaining faults are detected in each successive test step, which takes twice as long as the preceding step (Figure 2). Further, assume a small 10x10mm device fabricated in 10nm technology with 650 die per wafer and a four-site test with 90% yield at wafer probe. As shown in **Figure 3**, the shift-left strategy increases manufacturing cost by 9% but reduces unfound failures shipped by 51%. The walkaway here is that you can increase quality by finding 51% of the previously unfound faults before shipment with a small investment in additional testing.

For a larger logic part, you will have to work harder to obtain observability and controllability, and test time will be longer. Nevertheless, the same metric seems to

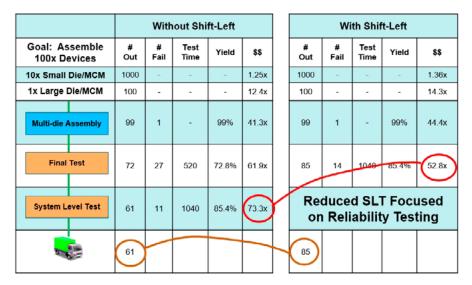

apply as for the smaller part. Consider single-site testing of a 10nm device with 85 die per wafer. Assume that without using a shift-left flow, this device requires a 30s wafer-probe time at 75% yield and a 60s KGD test time for 87.5% yield. With the shiftleft flow, manufacturing cost increases 16%, but unfound failures shipped are reduced by 53% (Figure 4). Finally, consider a multi-chip module that, without left shift, requires a 520s final test for 72.8% yield and a 1,040s system-level test for 85.4% yield. The shift left flow reduces manufacturing cost 28% and increases parts shipped by 37% (Figure 5).

#### **Test system changes**

For an effective shift-left strategy, test systems will require some changes. One key point is that active thermal control is becoming important, and it is something you cannot do on wafer probers. With wafer probers' chucks and high thermal mass, you can just set them at a temperature and hope it stays there.

Figure 3: For a small device, the shift-left strategy increases manufacturing cost by 9%, but reduces unfound failures shipped by 51%.

|               |          | Witl      | nout Sł      | nift-Left |       | With Shift-Left |           |              |       |       |  |

|---------------|----------|-----------|--------------|-----------|-------|-----------------|-----------|--------------|-------|-------|--|

|               | #<br>Out | #<br>Fail | Test<br>Time | Yield     | \$\$  | #<br>Out        | #<br>Fail | Test<br>Time | Yield | \$\$  |  |

| •             | 85       | 0         | -            | -         | 7.4x  | 85              | 0         | 1            | -     | 7.4x  |  |

| Wafer Probe   | 64       | 21        | 30           | 75%       | 10.2x | 56              | 29        | 90           | 65.6% | 12.4x |  |

| Thin Bump Saw | 63       | 1         | -            | 99%       | 10.3x | 55              | 1         | 1            | 99%   | 12.5x |  |

| KGD Test      | 55       | 8         | 60           | 87.5%     | 12.4x | 52              | 3         | 120          | 93.8% | 14.3x |  |

|               | 55       | 7         | -            | 1         |       | 52              | 3         | 1            | ,     |       |  |

**Figure 4:** For a large logic part shipping as a KGD using the shift-left strategy, manufacturing cost increases 16%, but unfound failures shipped are reduced by 53%.

### Your trusted partner in IC testing

**Figure 5:** For a multi-chip module, the shift-left strategy reduces manufacturing cost 28% and increases parts shipped by 37%.

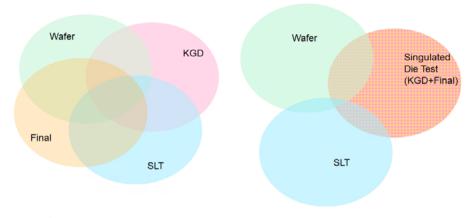

**Figure 6:** The move from: a) (left) a traditional test flow to b) (right) a shift-left test flow eliminates one test insertion and reduces over-testing.

Active thermal control (ATC) is feasible at the KGD test step, however, using a system such as the Advantest HA1000 die-level handling and probing system for singulated die testing.

In addition to ATC (with junction-temperature feedback per the device under test [DUT]), a KGD tester is able to take on final-test functions such as atspeed testing, which will require high-speed instruments, high-power supplies, high-frequency probes, and high current-carrying-capacity probes.

As KGD testers take on final-test functions, some traditional KGD tests, including two-temperature testing, will shift left to wafer test. And finally, system-level test functions, including

packaged device test, boot-up tests, and fuse-blowing, will shift left and can be performed on either a traditional final-test system or on a system-level-test system. What is required at this step is a system-focused environment with system-focused code that can boot up the device under test and run its firmware and software. A key benefit of the shift left flow is that it can eliminate one test insertion. One less test insertion means one less test cell—one less handler—bringing about significant financial benefits.

A related issue the industry is contending with is over-testing. If today we have wafer test, KGD test, final test, and system-level test, the reality is that a lot of tests are run four times, or at least two or three times. If we remove one test insertion, then by definition you are not going to be doing any tests four times over. In general, the Venn diagram regions in **Figure 6** will move away from each other, resulting in less overlap.

#### Summary

Several conclusions arise regarding this overview of the shift-left concept. First, test content itself is an incredibly valuable resource, and it is a resource that we can move around. For example, an  $f_{MAX}$  test can be done at the wafer level, it can be done at final test, or it can be done at system-level test. What we need to look at is where is the best place for us to do this important test for each device.

If you are shipping KGD, prior to shipment you will need to screen for obvious failures, confirm functionality at temperature extremes, find assembly-induced problems, and perform speed and power binning, full built-in self-test (BIST) and scan, high-speed I/O test, and fuse blowing.

In addition, this overview of shift left reconfirms what may be obvious to anybody in the industry: more testing sooner will increase the quality of your product for a small incremental cost increase. You will have to pay for test in any event, and making that payment sooner will allow you to: 1) save packaging cost, 2) reduce the number of good parts scrapped because of another part's problem in a shared multidie assembly, and 3) it will allow you to end up with an ultimately lower cost, more profitable product.

#### **Biography**

Dave Armstrong is Director of Business Development at Advantest America, Inc., San Jose, CA, and is also Chairman of the Test Technology Working group for the Heterogeneous Integration Roadmap. Prior to Advantest, he spent over two decades in HP/Agilent's IC test group, and before that he worked in the semiconductor industry in areas of IC and system design, product/yield engineering, as well as test engineering. He has degrees in Electrical, Computer, and Environmental Engineering from the U. of Michigan. Email d.armstrong@advantest.com

### **Global No.1! Total Test Solution Provider!**

ISC provides all the answers to the 5G semiconductor test solutions. ISC is here as the future approaches with IT, BT, Autonomous Car, and 5G.

ISC is a total test solutions based on a product portfolio that can test all semiconductor IC and IT products, providing the highest quality products in the shortest time to realize customer satisfaction and impression

#### **ELASTOMER SOCKETS & INTERPOSERS**

- High performance and competitive prices

- High speed & RF device capability

- No load board pad damage & no contact trace on the ball

- Customized design to meet challenging budget constraints

- Full thermal and electrical simulation

#### **POGO SOCKET SOLUTIONS**

- Various design available

- Excellent gap control & long lifespan

- High bandwidth & low contact resistance

#### **BURN-IN SOCKET SOLUTIONS**

- No ball damage

- Direct inserting on Burn In Board without soldering

- No damage on Burn In Board land

- Simple structure without sub PCB & easy maintenance

#### THERMAL CONTROL UNIT

- Extreme active temperature control

- · Customized design to meet challenging requirements

- Price competitiveness through self-designing and fabrication

- Safety auto shut-down temperature monitoring of the device & thermal control unit

- Full FEA analysis for strength, deflection, air flow and any other critical requirements

#### Hi-fix & Burn In Board

- High performance and competitive price

- Test fine pitch, high speed device at hot & cold temperature

- Customized design to meet individual requirements

# Emerging process and assembly challenges in electronics manufacturing

By Glenn Farris [Universal Instruments]

he semiconductor and semiconductor equipment industries expect to see a strong upturn in the next few years, with advanced packaging technologies a significant beneficiary of the market's strength. 5G, artificial intelligence, edge computing, persistent memory, integrated power management, and the transition to sub-5nm silicon technology are all driving the need for innovative packaging solutions. These solutions integrate silicon produced with disparate process nodes and deliver maximum performance at optimal cost.

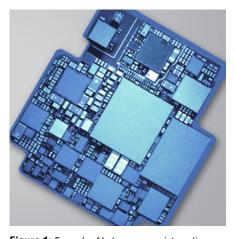

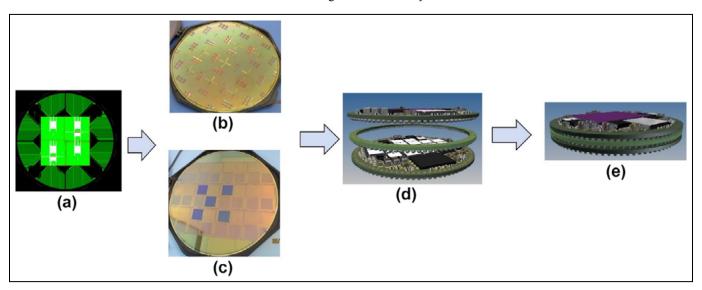

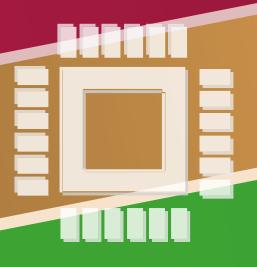

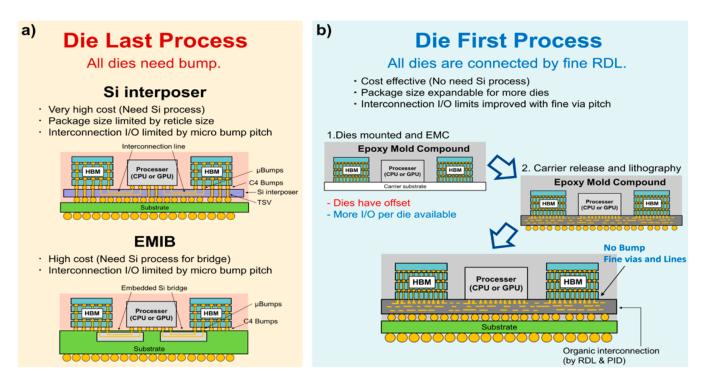

Heterogeneous integration (Figure 1), which utilizes a multitude of interconnect methodologies (from fan-

**Figure 1:** Example of heterogeneous integration application.

out to silicon interposer, to chiplet), addresses this challenge but requires unique solutions for efficient, cost-effective die placement. High-speed, high precision multi-die placement, directly and efficiently extracted from a range of different sized wafers, is critical to enable cost-effective assembly.

Complex multi-die architectures support a wide range of applications, including: insulated-gate bipolar transistor (IGBT), antennae-in-package (AiP), microelectromechanical systems (MEMS), high-performance computing (HPC), and advanced packaging products, each of which benefit from this technology. These architectures also create several challenges for efficient, cost-effective assembly. Accurate die placement, efficient changeover from picking one die type, or wafer type, to a different type, and the ability to mix wafer, tape, and tray fed material are critical to enable mass production solutions.

## Alternatives for implementing multi-die architectures

Multiple alternatives have been proposed to implement the multi-die architectures noted above. Some of these examples are described below.

EMIB. Embedded multi-die interconnect bridge (EMIB) is an elegant and cost-effective approach to the inpackage high-density interconnect of heterogeneous chips. EMIB uses a very small bridge die with multiple routing layers. This bridge die is embedded as part of the substrate fabrication process.

FOPLP (fan-out panel-level packaging). One of the latest packaging trends in microelectronics is FOPLP, which has a high potential for significant package miniaturization concerning package volume, but also with respect to its thickness. The technological core of FOPLP is the formation of a reconfigured molded wafer combined with a thin-film redistribution layer (RDL) to yield a surface-mount device (SMD)- compatible package.

FOWLP (fan-out wafer-level packaging). FOWLP is an integrated circuit packaging technology, and an enhancement of standard wafer-level packaging (WLP) solutions. In FOWLP, the wafer is diced first, but then the dies are very precisely re-positioned on a carrier wafer or panel, with space for fan-out kept around each die. The

carrier is then reconstituted by molding, followed by making a RDL atop the entire molded area (both atop the chip and atop the adjacent fan-out area), and then forming solder balls on top.

InFO (integrated fan-out wafer-level packaging). InFO is an innovative wafer-level system integration technology platform, featuring high-density RDL and through-InFO via (TIV) for high-density interconnect and performance for various applications, such as mobile, high-performance computing, etc.

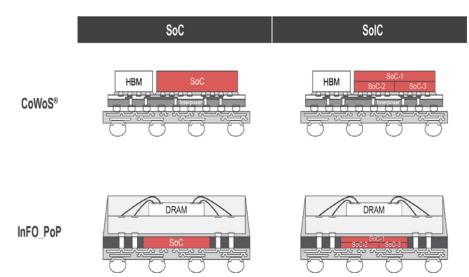

CoWoS® (chip-on-wafer-on-substrate). CoWoS® is a 2.5D wafer-level multi-chip packaging technology that incorporates multiple dies side-by-side on a silicon interposer in order to achieve better interconnect density and performance. Individual chips are bonded through micro-bumps on a silicon interposer forming a chip-on-wafer (CoW). The CoW is then subsequently thinned such that the through-silicon via (TSV) perforations are exposed. This is followed by C4 bumps formation and singulation. A CoWoS® package is completed through bonding to a package substrate.

SOIC (small outline integrated circuit). SOIC is a surface-mounted integrated circuit (IC) package that occupies an area about 30–50% less than an equivalent dual in-line package (DIP), with a typical thickness being 70% less.

**SiWLP** (system in wafer-level package). A SiWLP is fabricated using "RDL-first" technology for FOWLPs and provides high chip-I/O density, design flexibility, and package miniaturization.

**2.5D. 2.5D** is a packaging methodology for including multiple die inside the same package.

eWFO (embedded wafer fan-out). eWFO is fabricated in either wafer fabs using back end of line (BEOL) tools, materials and processes, or at outsourced semiconductor assembly and test suppliers (OSATS) using their built-up fabs and tools.

#### **Heterogeneous integration**

Moore's law is still providing a reduction in transistor size by a factor of two each year, but in the most advanced nodes we are no longer getting a corresponding reduction in cost. The combination of the need for performance advancement at lower cost is leading to new architectural paradigms. Printed circuit board assembly (PCBA)-based systems need to shrink into microelectronic form factors to address the needs of edge computing. SoC semiconductor devices are disaggregating to optimize process nodes by function.

The net result of the disaggregation noted above is a new approach to device packaging: heterogeneous integration. Rather than trying to cram functionality into a smaller package, the world is moving to optimize the performance of the chip with the performance of the package. This results in complex packaging assembly needs, and the need to support much thinner die handling. These resulting solutions require the combination of multiple die part numbers transferred from different wafer types (see Figure 2).

In the case of InFO, two different die types are evident, including SoC and dynamic random-access memory (DRAM). Each of these may utilize a different feeding source, potentially with one device fed direct from the wafer and another from a Joint Electron Device Engineering Council (JEDEC) standard tray. The key advantages of InFO are higher compute density and faster training time.

In the case of CoWoS®, three die types are evident, an SoC, a DRAM, and a silicon interposer (Si). These span a very wide die size range, requiring highly flexible placement platform capability.

TSMC's innovative CoWos® advanced packaging technology (Figure 2) integrates logic computing and memory chips in a 3-D manner for advanced products targeting artificial intelligence, cloud computing, data center, and super computer applications. This revolutionary 3-D integration facilitates power-efficient, high-speed computing while reducing heat and CO<sub>2</sub> emissions.

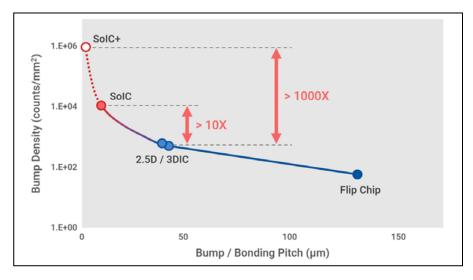

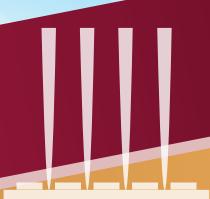

The transition to either siliconbased chip-to-chip interconnects or lithographically-processed interconnects requires extreme placement accuracy (Figure 3). At these pad pitches, placement accuracy below 10 µm is required. Assembly

Figure 2: Example of CoWoS® architecture (top) and InFO\_PoP architecture (bottom). Both applications are represented with and without SOIC integration.

Figure 3: Representation of typical interconnect pad pitch for 2.5D and 3D structures. The graph highlights pad pitch for 2D vs. SOIC.

Figure 4: Wafer-level fan-out application on a 600mm x 600mm substrate.

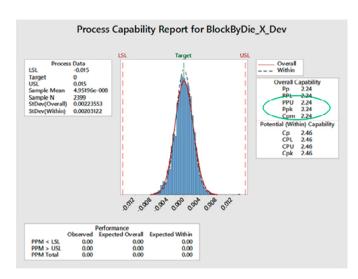

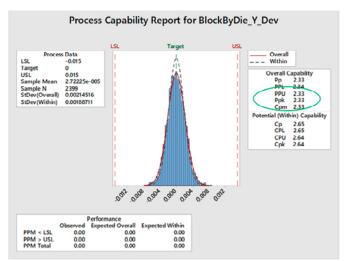

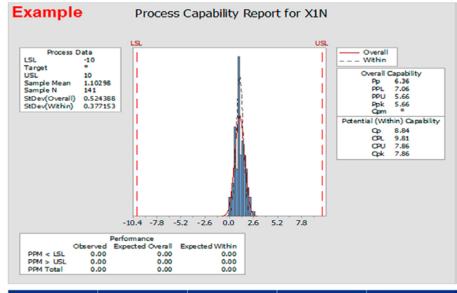

Figure 5: X-axis and Y-axis placement accuracy data at 16Kcph shows a standard deviation of <2.3µm.

| ALL ROTATIONS | X-AXIS | Y-AXIS | THETA    |

|---------------|--------|--------|----------|

| Min           | -7.34  | -6.58  | -0.04949 |

| Max           | 7.01   | 6.96   | 0.04672  |

| STDev         | 2.83   | 2.50   | 0.02     |

| Avg           | -0.84  | -0.41  | 0.00     |

| Cpk           | 1.08   | 1.28   | 1.56     |

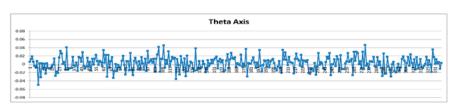

Figure 6: Theta accuracy statistics for 40mm x 40mm die on interposer.

| СРК  | X1N                | Y1N                | X2N                | Y2N                |

|------|--------------------|--------------------|--------------------|--------------------|

| 1.33 | $\pm$ 3.19 $\mu$ m | $\pm$ 3.01 $\mu$ m | $\pm 3.16~\mu m$   | $\pm 2.88~\mu m$   |

| 1.67 | $\pm$ 3.73 $\mu$ m | $\pm 3.58~\mu m$   | $\pm$ 3.83 $\mu$ m | $\pm$ 3.61 $\mu$ m |

Figure 7: XY scatterplot of AMS results. The table shows specification limits corresponding to Cpk values of 1.33 and 1.67 based on the above means and standard deviations. Data indicates system accuracies of <3.2µm @ Cpk 1.33.

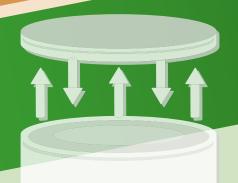

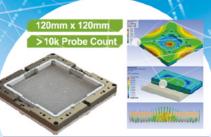

of these heterogeneous integration structures in a FOWLP, FOPLP, SLP or embedded process requires that this accuracy must be maintained over a placement area as large as 600mm x 600mm (**Figure 4**). To determine the feasability for these requirements, we assembled over 12 panels with an approximate 6mm x 6mm die with sub-50µm pitch copper pillar bumps utilizing our FuzionSC<sup>TM</sup> platform.

Four panels were built to establish a baseline and to validate trimming requirements by spindle and by placement location. These results were then incorporated into the placement map of the system. Six panels were then assembled and all placements were measured for X, Y and Theta variation (Figure 5). As can be seen from the data, the system was validated to be able to place die at speeds >16Kcph, with an accuracy of <2.3 µm standard deviations.

As die sizes for high-performance computing applications grow, the theta accuracy also becomes critical for precision pad to bump alignment. A study was completed assembling 40 large bumped die on an interposer, with all results measured (**Figure 6**). The results of this study demonstrated a capability of <0.075deg @ Cpk 1.56.

In high-volume manufacturing, active monitoring and control is required to maintain accuracy as a function of temperature, time, or number of placements, which prevent drift. An example solution is an accuracy management system (AMS), which monitors the placement performance of each spindle using a standard high-precision slug, and actively adjusts

# MPM | Camalot | Electrovert | Vitronics Soltec | Despatch

# Printing, Dispensing, Reflow, Cleaning and Thermal Processing Equipment for Semiconductor Packaging

ITW EAE is advancing innovation and development of next generation technology for semiconductor packaging. New technology that dramatically improves productivity and yields.

The MPM® Edison™ is the most accurate printer in the market. The Camalot® Prodigy™ dispenser features advanced technology like the Dynamic Dual Head™ that can synchronously dispense with two pumps regardless of part-to-part rotation. Vitronics Soltec reflow systems provide unmatched reliability. Electrovert® centrifugal and in-line cleaning systems provide high-performance cleaning of advanced packages. Despatch® offers high-performance ovens for polyimide curing and more.

## Designed for semiconductor yield improvement

Electronic Assembly Equipment

ITW EAE

spindle height to control for any variation identified.

Studies were conducted to determine baseline system performance using the AMS, such that any spindle variation over time could then be controlled (**Figure 7**). As can be seen from the results, AMS can resolve down to system accuracies of  $<3.2\mu m$  @ Cpk 1.33.

Substrate and interconnect dimensions require placement capability over large substrates up to 600mm x 600mm at sub-10µm XY accuracy and sub-0.075° theta accuracy to achieve high yield. Placement rates of >16K have been demonstrated at this performance level—a key aspect to minimizing the cost of assembly.

Additionally, as die thicknesses are reduced below 100 µm, there is an increased potential for cracking, chipping or uncontrolled warpage when handling and transporting die in tape or tray. Taping or tray transfer also has negative impacts on lead time and work in process (WiP). By transitioning to direct pick from wafer with a high-speed placement platform, die damage can be eliminated, while lead-time and WiP are reduced. Direct pick from wafer, however, presents several challenges that must be addressed. First, the process of stretching and unstretching a wafer can also lead to chipping, and must be eliminated. Second, with multiple die types and wafer types, a single placement solution needs to efficiently handle multiple die types picked from different wafers by minimizing the "changeover" time from one wafer type to a different wafer type.

A solution that can stretch and store wafers in an assembly system, asynchronous from pick operations in a wafer table, can eliminate stretch/unstretch cycles as well as maximize overall system utilization. Such a solution has been developed and evaluated utilizing a patented cartridge storage and transfer system for wafers. Data collected has demonstrated that such a system eliminates the need to unstretch a wafer until consumed. It also results in a reduction in wafer

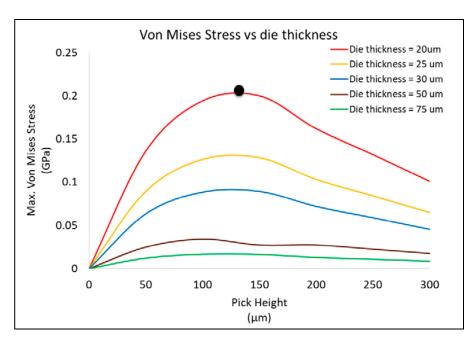

Figure 8: Study on key ejection parameters affecting die stress to ensure optimal ejector performance.

"changeover" time of approximately 50%. For large die applications, where the overall time to pick all die on a single wafer can be under 120 seconds, this can result in an overall system throughput improvement on the order of 25%. Likewise, for heterogeneous integration applications where a wafer exchange may occur in as few as 30 seconds, this can lead to overall throughput improvements of up to 100%.

Key benefits of the patented cartridge system includes: 1) minimizing deexpansion events; 2) managements of multiple wafer sizes; 3) reduction of downtime for tooling changeover; 4) accommodation of difficult die types (thin, large, high aspect ratio); and 5) elimination of die chipping with programmable stretch.

Key features of the online expansion system include: 1) eliminates the need to pre-expand wafers; 2) supports four 13-slot wafer cassettes or two 25-slot cassettes; and 3) four slots per side allow for management of four cartridges each.

Another feature of this solution is a high-precision (sub-micron X,Y,Z) servo-driven ejector that precisely releases the die from the wafer, allowing for fast wafer to placement handoff. In order to determine the correct ejector operation, our Advanced Process Lab (APL) undertook a study to examine the key ejection parameters affecting die stress. Results of this study are presented in **Figure 8**.

#### Summary

In conclusion, advanced semiconductor packaging applications are growing in volume and complexity and require new assembly solutions to ensure high yield at the best overall cost per placement. Innovative solutions have been assessed and proven to be viable, delivering the required accuracy over the SEMI standard large panel format. These solutions have additionally demonstrated the speed and utilization required for efficient and economic assembly operations. Heterogeneous integration delivers the ability to optimize the performance of the chip with the performance of the package.

#### Biography

Glenn Farris is VP Marketing and Corporate Strategy at Universal Instruments, Conklin, NY USA. He joined Universal in 2013 as VP, Marketing and has been instrumental in leading the company into developing strategic relationship with some of the world's largest technology leaders. He holds an MBA in Marketing and Finance from Santa Clara U., an MS in Engineering from Stanford U., and a BS in Engineering from Purdue U. Email glenn.farris@uic.com

## SUSS EQUIPMENT SOLUTIONS ENABLING LEADING-EDGE PACKAGING TECHNOLOGIES

SUSS MicroTec is a leading supplier of equipment and process solutions for the semiconductor industry enabling state-of-the-art packaging technologies from R&D to high volume production.

With next generation lithography solutions for FOWLP and leading edge wafer bonding technologies for 2.5D and 3D stacking, we contribute to the advancement of innovations in the key areas of packaging and system integration.

Always be one step ahead — with solutions from SUSS MicroTec. Contact us for more information!

SUSS MicroTec info@suss.com www.suss.com

## Wafer-scale superconducting multi-chip module

By Rabindra N. Das, Vladimir Bolkhovsky, Alex Wynn, Ravi Rastogi, Scott Zarr, Leonard M. Johnson [Quantum Information and Integrated Nanosystems Group, MIT Lincoln Laboratory]

his paper describes a strategy to combine laser direct write (LDW) and optical lithography (I-line) to fabricate 200mm wafer-scale superconducting multi-chip modules (S-MCM) for interconnecting multiple active superconducting flux quantum (SFQ) chips for next-generation cryogenic processing systems. The packaging strategy includes the development of S-MCM (48mm X 48mm) using large single I-line reticles, followed by reticle stitching to fabricate nearly the largest possible stitched S-MCM (96mm X 96mm) using a four mask/layer process. The stitching process starts with sequential exposure of multiple I-line photomasks - with small overlap (stitched area) to realize larger combined circuit areas for design-critical S-MCM layers with minimum linewidths of 0.8-1µm. The process also utilizes laser direct write (LDW) lithography to make wider (>1µm) features such as fan-out circuits, extending the stitched circuit area to include the entire 200mm wafer as a single S-MCM.

#### Introduction

As CMOS reaches the end of Moore's Law, scaling and power consumption continue to be a challenge, thereby driving the need to develop "beyond-CMOS" device technologies to advance highperformance computing. Superconducting electronics using Josephson junctions (JJs) as active devices are a promising candidate for high-performance computing because of their extremely low gate energies, fast clock speeds, and lossless signal propagation for data transport [1]. A major technical challenge facing superconducting circuit technology is achieving a very large scale of integration (VLSI). Developing a VLSI capability (10<sup>7</sup> or more JJs) with 100s of SFO chips in proximity to one another along with auxiliary semiconductor electronics (e.g., power supplies, clock generators, output amplifiers) in a single system is highly desirable to realize lossless circuit functionalities required for superconducting computing architectures. However, such VLSI capability has yet to be demonstrated.

This paper presents a system-on-wafer approach for integrating a large number of SFQ chips onto a full 200mm wafer S-MCM. This approach increases the circuit complexity (number of JJs) that can be integrated within a given cryogenic space by producing high chip-to-chip connectivity. Connecting superconductor electronics components using our approach enables a parallel scaling path. Connectivity of individual chips through superconducting wiring offers significant advantages relative to the equivalent integration methods for semiconductor-based electronics. With low-loss superconducting lines, power requirements for drivers and receivers for inter-chip communication can be equivalent to on-chip communication. This kind of communication is in stark contrast to CMOS-based integration where the number of I/Os can quickly dominate the power budget for a similar system. We present a niobium-indium microbump scheme to produce a variety of stitched and wafer-scale S-MCMs. This scheme enables the heterogeneous integration of known good chips to increase circuit density, functionality, and reduce the circuit footprint. In addition, we discuss thermocompression bonding of niobiumindium microbumps and their electrical performance at cryogenic temperatures.

Development of wafer-scale S-MCM proceeded in three steps. In subsequent sections, we will discuss the fabrication of a single reticle S-MCM, multiple reticles based stitched S-MCM, and stitched reticles with laser direct writing based wafer-scale S-MCM.

## Single reticle superconducting MCM

As an intermediate step towards demonstrating a large-area stitched S-MCM, a 48 x 48mm<sup>2</sup> S-MCM fabrication using a single I-line mask set (without

stitching) was evaluated. The S-MCM comprised four superconducting metal (Nb) layers and one resistor layer, allowing for several impedance-controlled clock and data lines. The MCM stack-up [2] requires a 0.8µm wide line to achieve 50 Ohms impedance. For S-MCM, all the critical layers with tight impedancecontrolled lines are fabricated by I-line lithography. The primary goal of this design is to evaluate minimum feature sizes for 48mm x 48mm circuits with a single mask exposure. The design includes snake/comb test structures and critical dimension (CD) cells (0.8µm lines) around the 48mm x 48mm periphery to evaluate the maximum S-MCM size within the limitations of the I-line photolithography tool; patterning aberrations may occur near the edge of the full reticle field, which is monitored using these structures. Second, the design includes perimeter and interior array interconnects that cover full reticle (20mm x 20mm) to be tested with SFQ chip flip-chip bonding. Scanning electron microscopy (SEM) results indicate that it is possible to create 48mm x 48mm critical circuits with a single I-line mask exposure, with the potential to be extended to the entire I-line field for stitched MCMs. In the next section, we will show stitching of 48mm x 48mm I-line masks (four masks/ layer) to produce 96mm x 96mm MCMs with 0.8µm CDs for Nb routing layers.

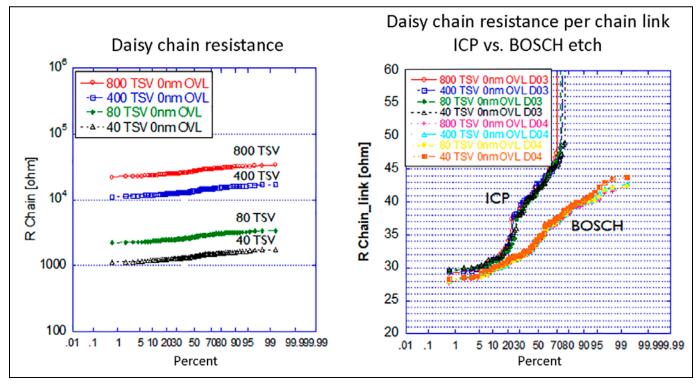

Prior to the stitching demonstrations, the flip-chip bonding process was tested using a two-component daisy chain structure. The first half of the structure consists of a single 200mm diameter S-MCM with many 20mm x 20mm bumped areas. Each bumped area contains many short and discontinuous wire segments terminated at a bump on either end of the segment. The second half of the structure is created by passive 20mm x 20mm Si chips that contain complementary wire segments terminated at bump pads; when the two halves are bonded together, they form a

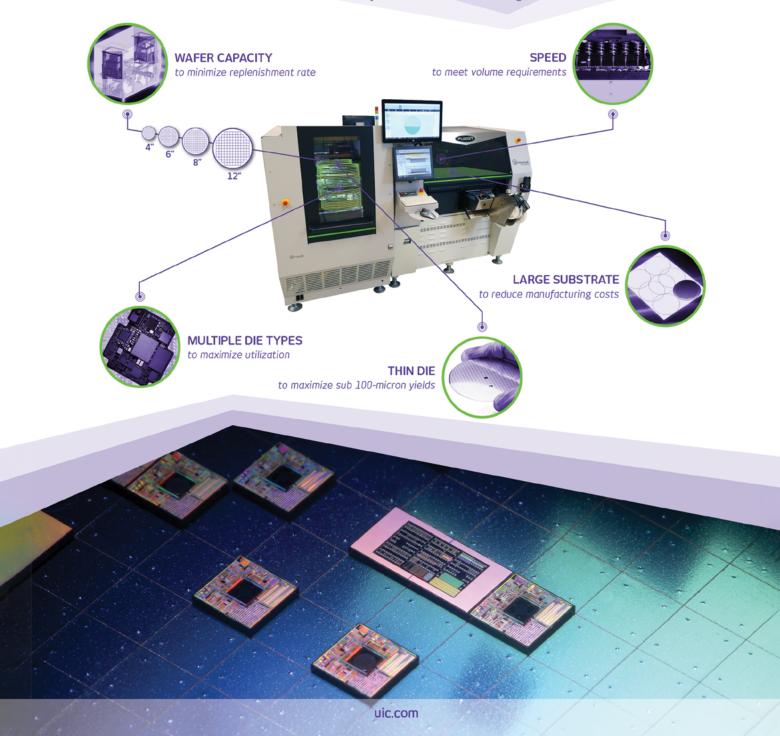

Advanced Packaging enables the world's most innovative products for 5G, Al, Edge Computing, AiP, and Integrated Power Management.

Consumer, Automotive and IoT devices are getting smaller and thinner, 2.5D and SiP multi-die packages are becoming more complex, InFO and Panel Fan-Out are driving large-format batch processing, and volume demands are rising.

These new challenges demand a comprehensive solution that breaks traditional boundaries for efficient multi-die assembly.

Introducing the **High-Speed Wafer Feeder** from Universal Instruments – **The world's fastest rapid-exchange multi-die feeder**. Combined with Universal's FuzionSC<sup>™</sup> Platform, it is the **ultimate multi-die solution for heterogeneous integration**.

- 16K cph dual-wafer tables, low-force pick heads

- Up to 52 unique wafers types at once; 4", 6", 8", 12"

- One-step "wafer-to-placement" handoff

- Synchronous wafer stretch and storage

- Maximum panel sizes up to 635mm x 610mm

- Maximum die size range with thinnest die

complete daisy chain that can be tested for continuity and total resistance. These devices are surrogates for a superconducting wafer-scale MCM and the associated superconducting chips to be connected. The current microbump fabrication process uses a single I-line liftoff process on the superconducting MCM. An interconnect layer (1000nm Nb, 20nm Ti, 50nm Pt, 150nm Au, 2000nm In) and an underbump metalization (UBM) layer (1000nm Nb, 20nm Ti, 50nm Pt, 150nm Au) are evaporated onto the S-MCM, and superconducting chips, respectively. The I-line photo process is important for reducing wafer-scale photoresist defects, defining bump diameter, and improved alignment to maintain electrical properties and minimize bump-bonding issues.

Figure 1 shows flip-chip S-MCMs bonded with 20mm x 20mm and 5mm x 5mm superconducting chips. We have fabricated 48mm x 48mm S-MCMs with niobium-indium (Nb-In) microbumps. Thermocompression (TC) bonding of Nb-In microbumps provides sufficient mechanical strength, creates lowresistance electrical interconnects, and produces minimum spacing between the chip and S-MCM. Furthermore, large Sichip bonding reduces the total number of bonding cycles and simplifies the assembly process. For example, Figure 1 shows a 2-chip (20mm x 20mm) S-MCM and a 16-chip (5mm x 5mm) S-MCM, which used 2, and 16 TC bonding cycles, respectively to complete each S-MCM. Additionally, because of minimum spacing and edge keep-out regions for dicing and in-line metrology, 2-chip (20mm x 20mm) S-MCMs can have a significantly higher active circuit area compared to a 16-chip S-MCM for a given lithography process.

As a case study of larger area flipchip interconnections, a 25mm x 25mm S-MCM with niobium-indium microbumps and a 20mm x 20mm superconducting chip were bonded together to fabricate a daisy chain structure. By alternating daisy chains in the lay-up prior to bonding, the Nb-In microbumps electrically connect the daisy chains. The S-MCMs include a 20mm x 20mm flip-chip daisy chain structure prepared with approximately 10,000 or 100,000 niobium-indium microbumps. To assess the electrical performance of the bump bonded full reticle chips, the S-MCMs with 20mm x 20mm chips were attached to a PCB card and wire bonded to measure I-V characteristics of bump interrupted niobium at 4.2K [2]. Niobiumindium microbumps not only showed very low resistance in the range of 0.05-0.1 milliohm at 4.2K, but also maintained high niobium critical current. We measured 20 mm x 20 mm flip-chip daisy chains ranging in number of interconnect segments from a few thousand to tens of thousands of microbumps in series. The I-V curve of approximately 24,000 Nb-In microbumps series flip-chip daisychain had a niobium critical current in

excess of 50mA at 4.2K. The large number of microbumps per chip, compact bump geometry, high critical current of niobium, and high current-carrying capacity of the microbumps enable this process to be suitable for building VLSI flipchip structures and developing complex superconducting computing systems.

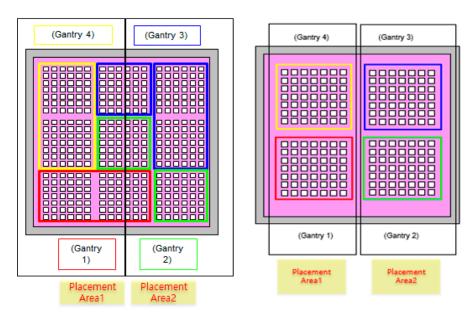

#### Stitched S-MCM

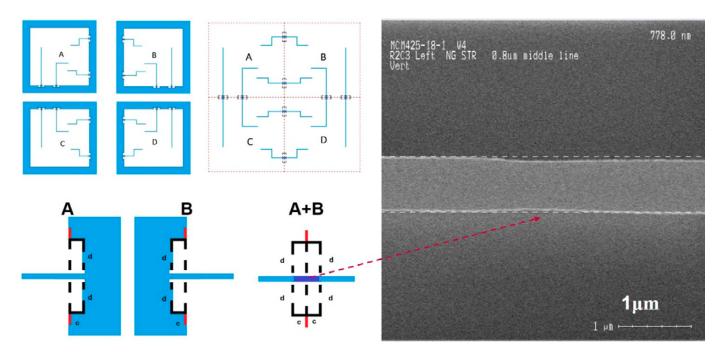

In this section, we detail the fabrication processes for reticle stitching. The previously described single reticlebased S-MCM fabrication process was modified to create a larger area stitched S-MCM. Figure 2 represents the stitching process where circuit lines of individual reticles are stitched at a stitch boundary. Four I-line photomasks (A, B, C, D) were joined together to create a stitched field. Photomask A and photomask B were stitched in the X-direction, while photomask A and photomask C were stitched in the Y-direction. Similarly, photomask B and photomask D were stitched in the Y-direction, while Photomask C and photomask D were stitched in the X-direction. The individual size of each photomask reticle (A, B, C, D) will determine the overall stitched field size. For example, a 35mm x 35mm reticle and a 48mm x 48mm reticle will produce 70mm x 70mm and 96mm x 96mm stitched S-MCMs respectively, for a four masks per layer process. Figures 2c and d also show an enlarged stitching area between photomask A and photomask B. Mask A has a circuit line extending into the chrome area. The extensions in the chrome area are defined as the overlap length where the line will expose twice (i.e., a double exposure). We optimize the overlap length as  $0.25\mu m$ . So, for a stitched line with a 0.25µm overlap length on each side, a minimum 0.5µm long line at the stitch boundary will expose photoresist twice for stitching. A double-exposed resist line will distort the linewidth at the stitch boundary. An optimal 0.25μm overlap length for each side provided the least amount of linewidth distortion at the stitch boundary. Additionally, corresponding SEM micrographs of a 0.8µm line going through the stitch boundary (in the X-direction) shows a representative example. SEM images (Figure 2e) show an approximately 70-110nm linewidth variation within a 1µm

**Figure 1:** Superconducting multichip modules (S-MCM) with attached superconducting test chips: a) (left) Optical image of a 48mm x 48mm S-MCM bonded with two 20mm x 20mm superconducting test chips; b) (right) Optical image of 32mm x 32mm S-MCM bonded with sixteen 5mm x 5mm superconducting test chips. One 20mm X 20mm superconducting test chip and sixteen 5mm X 5mm chips have the same circuit area.

Figure 2: Illustration of the stitching process with I-line clear field photomasks. The blue color defined in the images is a chrome layer in the mask: a) (top left) Four individual (A, B, C, D) pre-stitched reticles and their orientation prior to stitching; b) (top right) A stitched reticle. Stitching of the four individual reticles produces a single stitched field. For example, four 35mm x 35mm individual reticles will produce a 70mm x 70mm-stitched field. The bottom images represent an enlarged stitch area: c) (bottom left) This image represents a circuit line within individual reticles prior to stitching, and d) (bottom right) represents a circuit line stitched in the stitched reticle. e) SEM micrographs of a 50 0hms (0.8μm) line at the stitch boundary with a 0.25μm overlap.

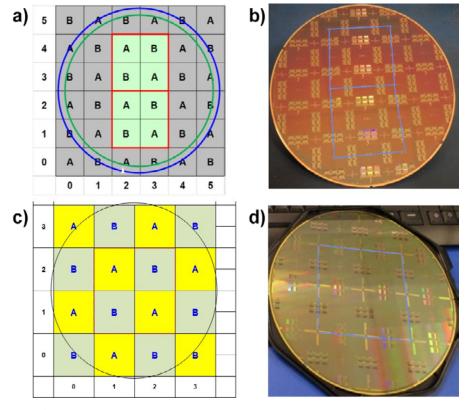

**Figure 3:** A stitched S-MCM wafer before dicing. Each design targeted a different reticle size for stitching: a) (top left) Schematic of a 35mm X 35mm I-line reticle stitching approach to create two 70mm X 70mm stitched S-MCMs; b) (top right) A corresponding image of two 70mm x 70mm stitched S-MCMs on a 200mm wafer; c) (bottom left) Schematic of a 48mm x 48mm I-line reticle stitching approach to create a single 96mm x 96mm stitched S-MCM; and d) (bottom right) Corresponding image of a 96mm x 96mm stitched S-MCM on a 200mm wafer.

length at the stitch boundary for a 0.25µm overlap. Electrical simulation shows that these kind of linewidth variations at the stitch boundary are electrically small and have little impedance effect below 1THz [3].

We have designed, fabricated, and tested two stitched S-MCMs. Figure 3 shows examples of stitched S-MCM based on 35mm X 35mm and 48mm X 48mm reticles. A stitched design includes a variety of impedance controlled lines, resonators, snake/combs, and via chains going back and forth between one reticle to the other and measured linewidth distortion at the stitch boundary. For example, a variety of snake/comb lines with linewidth/space ranging from  $0.8\mu m/1\mu m$  to  $2\mu m/2\mu m$  that travel back and forth through the stitch boundary were evaluated and compared to reference structures that were located away from the stitch boundary and did not see the stitching process.

Wafer-scale room-temperature electrical testing was used to evaluate reticle stitching. Each S-MCM wafer has a total of 384 test structures and each structure consists of snake/combs with LW/LS in the range of 0.8µm/lµm and larger. Out of 384 test structures, 96 test structures are stitched. As desired,

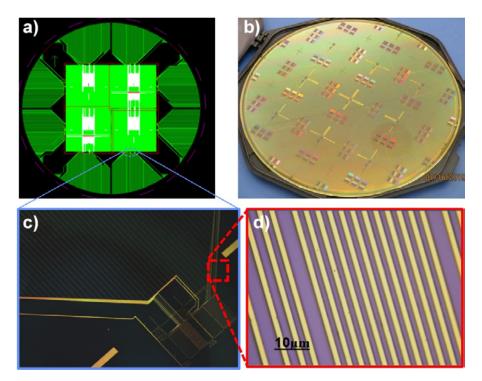

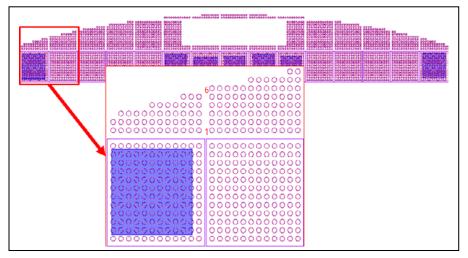

**Figure 4:** A 200mm wafer-scale S-MCM fabrication approach with a combination of laser direct write and I-line photolithography: a) GDS layers to create wafer-scale S-MCM; b) A corresponding image of wafer-scale S-MCM; and c-d) Enlarged optical micrographs of laser direct write based fan-out circuits.

the test structure shows no abnormal variation after stitching. Furthermore, the I-V characteristics of the snake/combs structures show wafer-to-wafer consistency. The measured RT resistance of stitched niobium snake/combs are similar to the non-stitched niobium snake/combs.

#### Wafer-scale S-MCM

Traditional wafer-scale MCM fabrication approaches use laser direct write or contact photolithography. Both approaches produce wider lines than the I-line process and require thicker dielectric in order to achieve the desired  $50\Omega$  impedance. Our approach uses reticle stitching for critical layers to

achieve a  $50\Omega$  impedance without changing the dielectric thickness and laser direct write provides additional wafer-scale fan-outs. Figure 3 shows that stitching increases S-MCM sizes and decreases the total number of S-MCMs per wafer. For example, 35mmX35mm and 48mmX48mm reticles will produce 16 S-MCMs and 6 S-MCMs per 200mm wafer, respectively. Whereas stitching of 35mmX35mm and 48mmX48mm reticles will produce two S-MCMs and one S-MCM per 200mm wafer, respectively. Wafer real estate usage from a 35mmX35mm MCM to a 96mmX96mm MCM was reduced from 62.3% to 29.3%, respectively, and remaining area of the wafer will be diced out.

We have fabricated 200mm wafer-scale S-MCMs by combining I-line and laser direct write methods. The process uses stitching of multiple I-line photomasks to produce critical design layers with minimum feature sizes around 0.8µm. For example, Figure 4 uses a 48mmX48mm reticle to create 96mmX96mm large stitched layers. Subsequently, applied laser direct write lithography (LDW) for connecting reticles with wider (>1µm) lines [3], adding fan-out circuits and extending circuit features to the entire wafer real estate. This kind of wafer-scale S-MCM with a wafer-interposer-wafer (WIW) configuration [4] offers many advantages. The wafer-scale S-MCM eliminates the need for substrates, printed

Figure 5: A wafer-scale assembly process with a superconducting multichip module (S-MCM): a) I-line and LDW GDS layers for wafer-scale S-MCM; b) A corresponding wafer-scale S-MCM; c) Flip-chip wafer-scale bonded S-MCM with 20mm x 20mm superconducting test chip; and d) Schematic of wafer-to-wafer assembly options; (e) Schematic of a future 3D wafer-interposer-wafer (WIW) integration strategy. The superconducting chip, interposer, and wafer-scale S-MCMs are fabricated separately and joined together using flip-chip connection.

circuit boards (PCBs) and associated assembly processing. In this approach, the superconducting test chip joined using niobium-indium or indium u-bumps that provide both electrical connectivity and mechanical stability between the different chips. The combination of I-line and LDW reduces the total number of masks. The use of single photoresist for UBM and micro-bump fabrication not only reduces additional processing steps, but also minimize/eliminate bumprelated defects suitable for wafer-scale S-MCM fabrication. Furthermore, LDW lithography utilizes full-wafer real estate and provides fan-out circuits for attaching connectors and cables to connect with the next level of semiconducting electronics. Wafer-scale S-MCM circuits will a create a loss-less, superconducting path for chipto-chip communication, whereas the traditional approach will go through a multilevel of assemblies with many normal metal interrupted superconducting paths.

The niobium-indium microbump thermocompression bonding approach can be extended to attach multiple 20mm x 20mm chips to a single, large superconducting MCM wafer, which is a valuable capability as we consider scaling to larger systems, such as waferscale S-MCM demonstrations. The use of wafer-scale S-MCM technology for the base superconducting module enables a combination of active and passive interconnect-based circuits; such an S-MCM could be used both for superconducting chips (singleflux-quantum [SFQ], rapid singleflux-quantum [RSFQ], quantum flux parametron [QFP]) in proximity to one another, along with auxiliary semiconductor electronics (e.g., power supplies, clock generators, output amplifiers) in a single system.

As illustrated in Figure 5, the multiple wafer-to-wafer assembly approach creates a system that can accommodate a

large number of superconducting chips. In **Figures 5d** and **e**, we also show a schematic view of how these wafer-scale S-MCM signals will be routed through a high-density interposer to produce wafer-interposer-wafer (WIW) configurations. In general, three types of signals are envisioned: DC, 50 Ohm characteristic impedance for clock line, and 10-20 Ohm characteristic impedance for the data line. As we look further out, we also consider a superconducting PCB to assemble a WIW structure for various superconducting cryogenic packaging solutions.

#### Summary

The demand for superconducting computing scalability beyond arrays of a few superconducting chips is driving the need for greater wiring densities and more functionality onto a single cryogenic package. One way to address this demand is with the use of flip-chip integration of wafer-scale S-MCMs with microbump-based interconnects to electrically interface multiple superconducting chips. Niobium-indium microbump-based flip-chip interconnects are capable of maintaining very low interconnect resistance, which are advantageous for superconducting packaging.

We have demonstrated large S-MCM (48 x 48mm<sup>2</sup>) fabrication with single I-line mask exposure and thermocompression bonding to attach up to 20mm x 20mm superconducting chips to the S-MCM module. We have shown that the sequential exposure of two photomasks (e.g., A and B,) with small overlap (stitched) can produce larger S-MCM substrates up to 96 x 96mm<sup>2</sup> with four masks/layer combined. I-line and laser direct write photolithography combinations demonstrated full-wafer S-MCM fabrication capability. These combined features show the potential to scale S-MCM technology with highdensity, low-resistance interconnects to wafer-size substrates, thereby enabling system integration for next-generation superconducting VLSI systems.

#### **Acknowledgments**

We gratefully acknowledge M.A. Gouker, S.K. Tolpygo, R. Lambert, R. D'Onofrio, C. Stark, and P. Murphy for useful discussions, and K. Magoon, P. Baldo, T. Weir, M. Townsend, M. Augeri, J. Liddell, B. Osadchy, M. Hellstrom, C. Thoummaraj, and J. Wilson for valuable technical assistance. This research was funded by the Defense Advanced Research Projects Agency (DARPA). Opinions, interpretations, conclusions and recommendations are those of the authors and are not necessarily endorsed by the United States Government.

#### References

- 1. D. S. Holmes, A. L. Ripple, M. M. Manheimer, "Energy efficient superconducting computing-power budgets and requirements," IEEE Trans. on Applied Superconductivity, 23(3)1701610 (2013).

- 2. R. N. Das, V. Bolkhovsky, S. K. Tolpygo, P. Gouker, L. M. Johnson, E. A. Dauler, M. A. Gouker, "Large-scale cryogenic integration approach for superconducting high-performance computing," IEEE Electronic Comp. & Tech. Conf. (ECTC) Proc., 675-683 (2017).

- 3. R. N. Das, V. Bolkhovsky, C. Galbraith, D. Oates, J. J. Plant, R. D. Lambert, et al., "Interconnect scheme for die-to-die and die-to-wafer-level heterogeneous integration for highperformance computing," IEEE ECTC Proc., 1611-1621 (2019).

- 4. R.N. Das, F. D. Egitto, J. Lauffer, B. Bonitz, B. Wilson, M. D. Poliks, et al., "3D-interconnect approach for high end electronics," IEEE ECTC Proc., 1333-1339 (2012).

Rabindra N. Das is a Member of the Technical Staff in the Quantum Information and Integrated Nanosystems Group, MIT Lincoln Laboratory, Lexington, MA USA. Prior to MIT, he was a Principal Engineer at Endicott Interconnect Technologies (formerly IBM Endicott). Dr. Das has 18 years of experience in microelectronics packaging development for applications ranging from HPC to medical to quantum electronics. He holds 48 patents and more than 100 publications. Email Rabindra.Das@ll.mit.edu

Vladimir Bolkhovsky is a Member of the Technical Staff in the Quantum Information and Integrated Nanosystems Group, MIT Lincoln Laboratory, Lexington, MA USA. He has more than 40 years of experience in the semiconductor industry and in superconductor process development. He received an MS in Chemical Engineering and holds multiple patents and has more than 20 publications.

# international TEST SOLUTIONS

PROBE CARD CLEANING

TEST

CONTACTOR

CLEANING

CHUCK CLEANING WAFER

**ENGINEERED CLEANING SOLUTIONS**

FOR THE SEMICONDUCTOR INDUSTRY:

Improving yield, reducing cost.

www.inttest.net

# 600mm wafer-level fan-out on panel-level processing with 6-sided die protection

By Jacinta Aman Lim, YunMook Park, Byung Cheol Kim, Edil Devera [nepes]

urrently, a 300mm carrier wafer for fan-out wafer-level packaging (FOWLP) is the mainstream format used for power management integrated circuits (PMICs), radio frequency (RF) and other single-die applications. As the volume of these devices continues to rise, the need for migration to panel sizes larger than 300mm becomes a necessity for cost reduction and capacity.

The fastest adoption of fan-out technology is now in 5G, automotive and healthcare. Traditional applications such as audio codecs, PMICs, micro-controller units (MCU) and RF continue to use FOWLP as an alternative to wafer-level chip-scale packaging (WLCSP) due to its 5-sided or 6-sided die protection. As fanout packaging becomes mainstream and in order to get broader adoption of it, the need for driving down the cost continues to be at the forefront of fan-out suppliers.

The 600mm x 600mm format utilized in this study leverages existing backend processing equipment used on 200mm and 300mm wafers for cost savings. Utilizing existing equipment enabled the panel to be singulated into 4x300mm or 9x200mm square segments to enable probe testing.

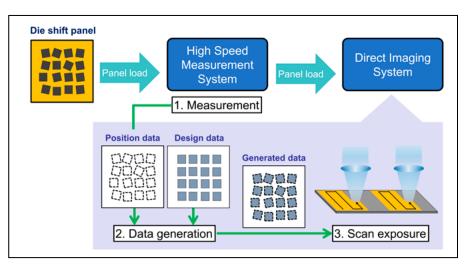

Coupling the 6-sided die protection process M-Series<sup>TM</sup> with 600mm x 600mm panel-level processing paves the way for innovative methods for fan-out processing. New photolithography processing that utilizes laser direct imaging (Adaptive Patterning<sup>TM</sup>) to auto scale for dieshift mitigation is heavily dependent on segmentation of the panel. In this instance, the 600mm panel is either segmented into 4x300mm, 9x200mm or 1x600mm for the photolithography steps. Depending on the number of fiducials used during the photolithography steps, capital expenditure and exposure accuracy would be highly dependent on the segmentation chosen. In addition, new metrology tools and panel warpage management will need to be considered for quality assurance.

This paper will present a case study of utilizing 600mm x 600mm panel size to process a single die with 6-sided die protection. Considerations for repassivation, redistribution layer and solder ball placement will be discussed. Challenges pertaining to large panel processing through the repassivation and redistribution layer will be presented; additionally, panel-level inspection considerations post mold cure, reliability considerations, and the future of 600mm x 600mm panel-level processing for 6-sided die protection will be summarized.

## Introduction to wafer-level packaging

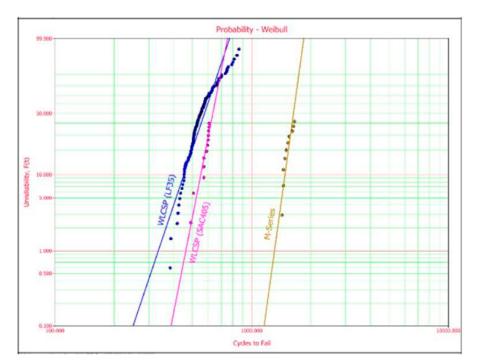

There are several types of wafer-level packaging (WLP) in the industry. The mainstream is WLCSP, or fan-in, followed by variations of FOWLP. In the example shown in **Table 1**, we look at two fan-out processes in comparison with WLCSP. In comparison with processing complexity, the left-most column (M-Series<sup>TM</sup>) ranks highest, with WLCSP being the least complex. In terms of package reliability, 6-sided die protection ranks highest compared to WLCSP as shown in the Weibull plot (**Figure 1**). In the plot, a 6mm x 6mm WLCSP test chip, which was also used on a 6.25mm x

6.25mm fan-out package, was tested with board-level temperature cycling (TC) on a 1mm board, with SAC405. The bump pitch was at 500µm with no under bump metallization (UBM). There were no TC failures up to 1000 cycles. The plot in Figure 1 shows >200% improvement for TC over WLCSP [1].

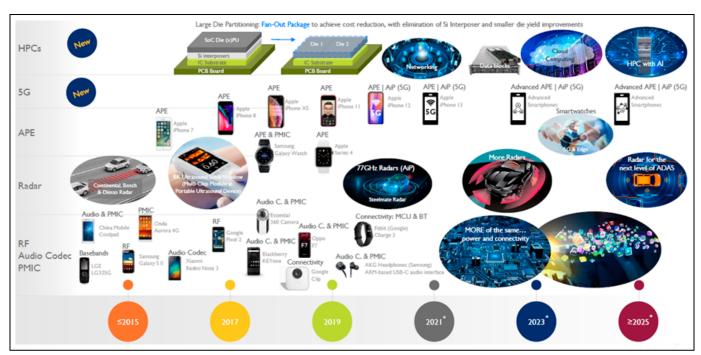

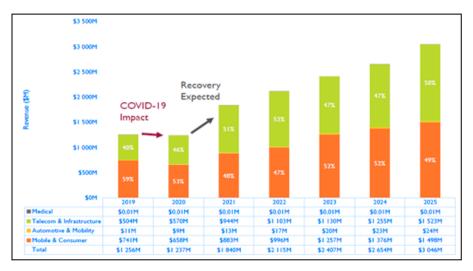

#### Fan-out packaging drivers

As can be seen from **Figure 2**, some of the major market drivers are RF, audio codec, PMIC, radar, 5G and high-speed computing [2].

5G adoption is central to large data transfers to enable a new user experience. and enabling better cloud-based business management as well as increasing our level of interaction with one another. In comparison to flip-chip ball grid array (FCBGA) packages, the interconnect length between the integrated circuit (IC) and the antenna is shorter, thereby reducing the signal loss from the radio frequency (RF) chip in fan-out packaging. Leading players such as TSMC and Mediatek have shown that fan-out packaging can enable low transmission loss and high antenna performance for mmWave system integration [2].

As for high-performance computing (HPC), a surge in the number of Internet

Table 1: Attributes between FOWLP and WLCSP.

Figure 1: Weibull plot for WLCSP vs. M-Series™. SOURCE: DECA

of Things (IoT) devices is boosting the demands for HPC systems and data centers. Higher functionality coupled with smaller package sizes are main drivers for fan-out system in package (SiP). The industry is relying more on heterogeneous solutions to integrate dies with shorter and denser interconnections [2]. Based on early stage testing, high-bandwidth and high-speed SERDES signal is positively

validated by fan-out packaging from many fabless players like NVIDIA, Mediatek, Nephos and HiSilicon.

Lastly, for radar at 77GHz, advanced driver assistance systems (ADAS) are paving the way for full autonomy in the automotive industry [2,4]. A 77GHz automotive radar system offers key advantages over a 24GHz radar and light detection and ranging (LiDAR) because of

its robustness in detection, range resolution and simultaneous multiple-depth detection under severe environmental conditions. Fan-out packaging is already established in radar and 77GHz performance is proven to be better than other packaging platforms such as flip-chip ball grid array (FCBGA). This improvement is because of the routing of redistribution layers (RDLs) from thin-flim processing in FOWLP, thereby resulting in very small layer dimensions and tolerances. Consequently, the fine line/space from RDL processing enables low-loss wiring and superior RF performance [2,4].

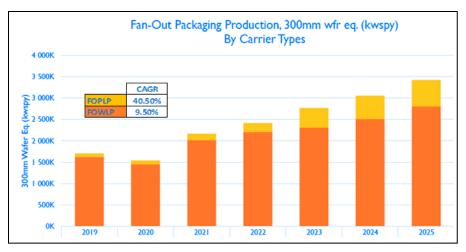

## Production volume of fan-out packaging

In terms of production volume, both FOWLP and FOPLP are growing, though FOPLP will grow significantly faster from 2021 and beyond (Figure 3). We do note that the COVID-19 pandemic (Coronavirus) has caused a contraction of the overall economic activity, negatively impacting semiconductor development and production as seen in 2019 and 2020 [2,5]. FOWLP revenue will continue to experience some decline in 2020, reflecting the COVID-19 impact for mobile and consumer applications.

Data-driven end systems, however, continue to grow in delivering more data functionalities paving the way to 5G adoption. FOWLP revenue for

Figure 2: Fan-out packaging drivers. SOURCE: YDR20078 Fan-out Packaging 2020 Yole Report, Yole Développement

## LEENO **Total Interface Solutions**

**Spring Contact Probe**

90um Pitch~

**Probe Head**

#### **Specification**

Pitch: Min.120um Spring Force: 8.0g@250um Current Rating : 1.3A Inductance: 0.3 nH

Probe for Fine Pitch Probe Head

**Logic Test** Socket

> High Speed

Frequency: >20GHz VSWR: < 1.2

**Automatic Coaxial Probe**

#### **Electrical Analysis**

CCC Test, HFSS, TDR Eye Diagram **4Port VNA Test**

**MP** Socket

**Large Device** Socket

#### Specification

Frequency: 80GHz(BGA), 100GHz(QFN, LGA)

Pitch : 0.25mm~ Crosstalk: -60dB Impedance : 50Ω±10%

**Coaxial Probe for** 100GHz

Figure 3: Production volume FOWLP vs. FOPLP. SOURCE: YDR20078 Fan-out Packaging 2020 Yole Report, Yole Développement

Figure 4: Fan-out packaging market revenue by end market. SOURCE: YDR20078 Fan-out Packaging 2020 Yole Report, Yole Développement

Figure 5: M-Series™ key process steps. SOURCE: DECA

telecom and infrastructure is improving moderately in 2020 and expected to recover in 2021 [2] (Figure 4).

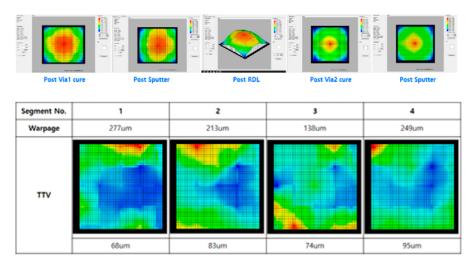

Based on the positive outlook for FOWLP in general, outsourced semiconductor assembly and test suppliers (OSATS) have been gearing up to meet the customer demands for 2021 and beyond. One of the key areas in FOWLP development is expanding from the traditional 300mm round carrier to a 600mm x 600mm panel-level processing for fan-out. Specifically, we will be focusing on 6-sided die protection with mold compound material from a 300mm round carrier to 600mm x 600mm 6-sided die protection with mold compound material. We will further discuss some of the key challenges with managing die shift, panel warpage and panel design.

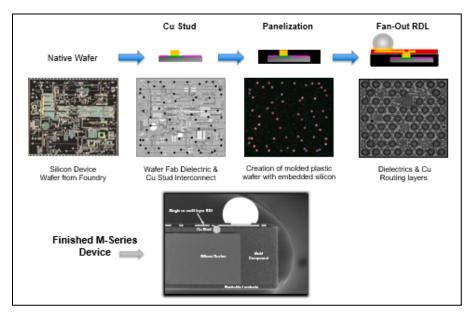

## 6-sided die protection with mold compound

The process for a molded M-Series<sup>TM</sup> device is illustrated in **Figure 5**. We begin with the incoming silicon wafer, either in 200mm or 300mm format. The wafer first undergoes a copper stud buildup process for connecting the silicon to the outside of the molded package in a subsequent process. The wafer is then singulated to prepare for the next step of panelization.

During the panelization process, the singulated die is picked and placed onto a temporary carrier face up, with the copper studs up. Once the entire panel is populated with known good die (KGD), the carrier undergoes a mold compression process. Subsequent processes such as Dielectric 1, RDL, Dielectric 2, UBM and solder ball placement are now similar to those done in WLCSP processing.

The unique portion of the photolithography process is the use of laser direct imaging, which is mask-less. In this instance, traditional reticles and masks are eliminated. The process works by dynamically adjusting a portion of the interconnect structure to accurately connect to the copper studs that are protruding through the mold compound for each individual die in the molded panel. A proprietary design tool adjusts the fan-out unit design for each package on the panel so that the first via layer and the fan-out RDL pattern are properly aligned to the pillars of the die. The design files for each panel are imported to a lithography machine that uses the design data to dynamically apply a

Figure 6: Die shift illustration from chip attach to post-mold cure.

custom adaptive pattern to each panel [1]. Utilizing this photolithography process helps with mitigating issues encountered during die shift  $(X, Y, \Theta)$ .

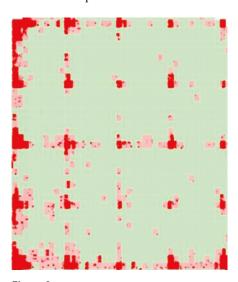

## Key challenges in 600mm panel processing

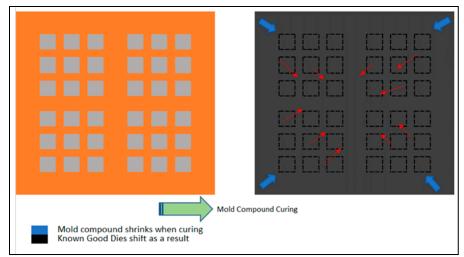

Some of the key challenges in 600mm x 600mm PLP are die shift during the panelization process, warpage control, mold thickness variation, C-mode scanning acoustic microscopy (CSAM) for defect detection, panel segmentation and panel design to satisfy a >99.5% yield requirement. Some of these challenges are addressed in the sections below.

**Panelization.** In **Figure 6**, an example of why die shift occurs is illustrated. There are two major areas for die shift. The first will occur at the chip attach process and the second will occur during the mold compression process. During the chip attach process, singulated die may experience a shift in the x, y or  $\theta$

**Figure 7:** Die position compensation and mold dispense need to be optimized.

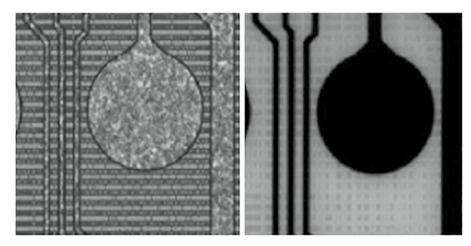

Low Magnification

**CSAM Verification**

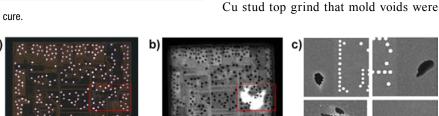

**Figure 8:** a) Example of CSAM defects: a) low magnification microscope; b) CSAM inspection; c) (four panels) Mold void after panel top grind post-CSAM.

direction. This shift can be attributed to an incorrect recipe set-up or pick and place bond heads that are not aligned to the center of the die, or to optical misalignment.

During the mold compression process, mold material tends to shrink and therefore tends to gravitate towards the center of the panel. Consequently, this shrinkage also affects die placement from

the previous process. An example of a 600mm X 600mm panel that will require further improvements in mold dispense is shown in Figure 7. Referencing Figure 7, die shift during mold compression can be mitigated by applying a die position compensation during the chip attach process. In addition, the mold dispense pattern can be optimized to ensure better coverage and the minimization of total thickness variation (TTV) within the panel. The use of laser directed imaging

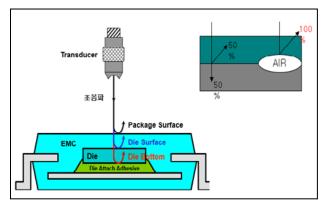

Figure 9: CSAM mechanism for checking mold voids.

present from CSAM inspection. In this example, the CSAM is performed prior to the Dielectric 1 process.

to compensate for minor die shifts during RDL patterning will also contribute to

CSAM inspection: mold voids detection. Mold voids can occur because of short gel time, short spiral flow length of the mold compound, contamination on the interface between silicon and mold compound material, or an un-optimized mold dispense profile and parameters, to name a few causes. In the example from Figure 8b, mold voids are normally detected with a CSAM metrology tool because a standard microscope will

not be able to detect voids at the mold

compound to the Si interface layer

(Figure 8a). Figure 8c confirms post-

overall panel yield.

In the example shown in **Figure 9**, the entire panel is submerged in water. Ultrasonic waves cannot pass through air pockets and therefore, the waves reflects at different interfaces or defects. For example, any air pockets or areas where the ultrasonic wave cannot pass through will be reflected 100%. This, in turn, provides us with a mapping of what the

Figure 10: TTV and warpage profile results from evaluation.

| Silicon BG Thickness     | 280um – 700um |

|--------------------------|---------------|

| Mold Thickness           | 405um – 815um |

| Fan Out Ratio            | <1.1          |

| TTV Spec Requirement     | <50um         |

| Warpage Spec Requirement | <1mm          |

**Table 2:** Evaluation plan for warpage and TTV for 600mm PLP.

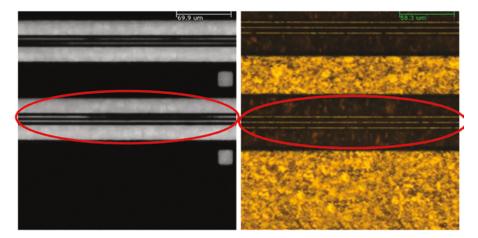

defect area looks like and its location on the molded panel.